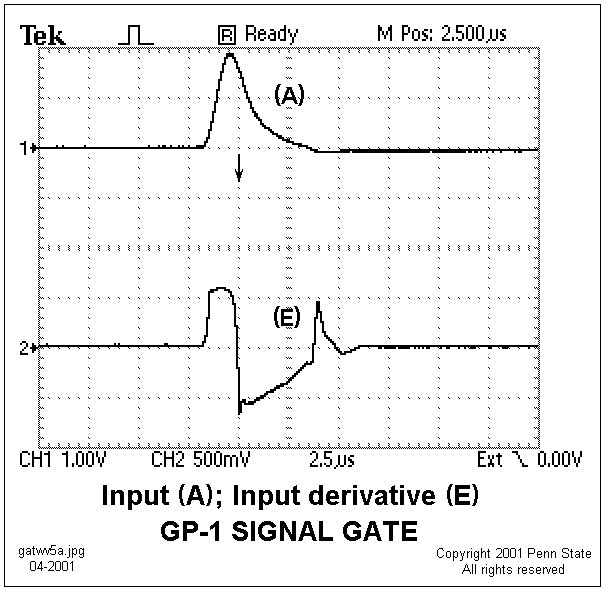

Monophasic input signal from

the Simulator at point (A) on the Signal

Gate circuit diagram and input signal derivative found at point (E).

The following Schmitt trigger, U7a, is triggered when the first downward

limb of (E) crosses zero slightly after the input peak. The leading

edge of U7a output, in turn, triggers the gate pulse

generator, U10, if, and only if, the input peak occurs within the 18-microsecond

duration of the enable pulse (D).

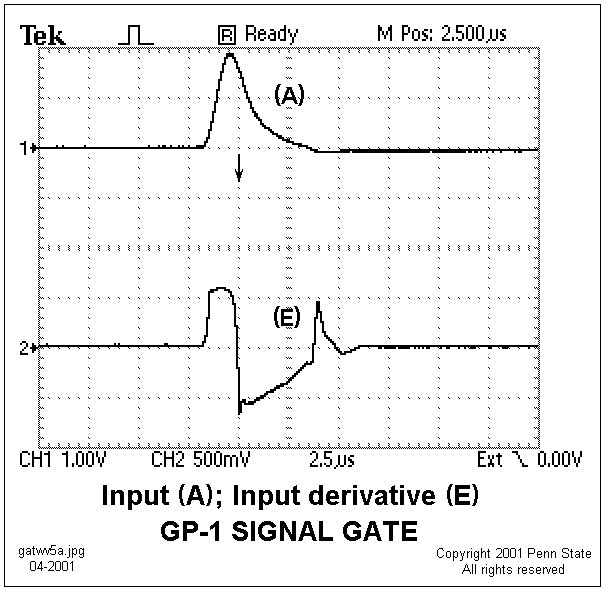

Monophasic input signal from

the Simulator at point (A) on the Signal

Gate circuit diagram and input signal derivative found at point (E).

The following Schmitt trigger, U7a, is triggered when the first downward

limb of (E) crosses zero slightly after the input peak. The leading

edge of U7a output, in turn, triggers the gate pulse

generator, U10, if, and only if, the input peak occurs within the 18-microsecond

duration of the enable pulse (D).