## Description

The UD series of ULC  $^{\text{m}}$ s is optimized for conversion of small- to medium-sized PLDs, CPLDs and FPGAs. This series use a unique architecture that provides a high I/O-to-gate ratio. Devices are implemented in high-performance CMOS technology with 0.8-mm (drawn)/0.65-mm (effective) channel lengths, and are capable of supporting flip-flop toggle rates of 200 MHz, operating clock frequencies up to 100 MHz, and input to output delays as fast as 7 ns.

The I/O-intensive architecture of the UD series efficiently supports a conversion of many PLD architecture and FPGA devices types, which would typically result in pad-limited designs with very low core utilization in more traditional gate-array families.

Conversion to the UD series of ULC can provide a significant reduction in operating power when compared to the original PLD or FPGA. This is especially true when

compared to many PLD and CPLD architecture devices, which typically consume 100 mA or more even when not being clocked. The UD series has a very low standby consumption of 0.4 nA/gate typically, which would yield a standby current of 4 mA on a 10,000 gate design. Operating consumption is a strict function of clock frequency, which typically results in a power reduction of 50% to 90% depending on the device being compared.

With better noise margin at the inputs, and higher drive available on outputs, UD ULCs provide I/O buffers that are better suited for bus interfaces in comparison with FPGAs and PLDs. At the same time, careful latch-up prevention (see section on Technology) completely eliminates the comparative benefits of bipolar technology. Additional safeguards in circuit and technology design afford ESD protection levels in excess of 2000 V.

### Features

- High performance ULC<sup>™</sup> family suitable for small to medium sized PLDs and FPGAs

- Conversions to approximately 8000 FPGA gates

- Pin counts to 100 pins

- Any pin-out matched due to no dedicated pads

- 0.8-mm (drawn)/0.65-mm (effective) single-layer metal CMOS technology

- Two routing levels in metal and silicide polysilicon

- All inputs incorporate a Schmitt trigger (0.4-V hysteresis) for improved noise immunity

- High current drive capability on each I/O

- Programmable sink/source current up to 12 mA per buffer (UD10, UD16)

- Programmable sink/source current up to 24 mA per buffer (UD02, UD03, UD09, UD14, UD27)

- Up to 48 mA of sink/source current per output pin with parallel output buffers

- Full range of packages: DIPs, SOICs, LCCs/PLCCs, PQFPs/TQFPs, PGAs/PPGAs

- Unique built-in voltage translation allowing mixed voltage operation:

- 0- to 5-V input voltage allowed on all inputs and I/Os when operating at 3.3 V

- No input clamping before 7-V Minimum

- Offers voltage level translation when interfacing between 5-V and 3.3-V logic

## **Product Outline**

| Part<br>Number | Pads | Equivalent<br>FPGA Gates | Maximum<br>Drive |

|----------------|------|--------------------------|------------------|

| UD02           | 31   | 750                      | 24 mA            |

| UD03           | 25   | 800                      | 24 mA            |

| UD09           | 51   | 2800                     | 24 mA            |

| UD10           | 68   | 3100                     | 12 mA            |

| UD14           | 78   | 4100                     | 24 mA            |

| UD16           | 84   | 4700                     | 12 mA            |

| UD27           | 100  | 8400                     | 24 mA            |

#### Architecture

The architecture of the UD series is optimized with: (i) a high I/O-to-gate ratio, (ii) efficient handling of high current outputs, and (iii) high speed at both internal cells and output buffers. All of this is accomplished with the simplicity and reliability of single-layer metal technology.

# **UD Series**

# TEMIC Matra MHS

The I/O-to-gate ratio improvement is achieved through careful I/O placement and gate bank configuration.

Several design considerations support the high-drive capability of the UD Series.

To support the high currents, and to additionally maximize  $V_{OL}$  and  $V_{OH}$  for better noise margins at the outputs, wide  $V_{DD}$  and  $V_{SS}$  buses are used on the arrays. These reduce the resistance and thus the IR drop to the outputs.

The configuration of the I/O circuitry is optimized for efficient implementation of TTL-level compatible digital circuits. TTL input level and cell control logic are built in to the I/O without the use of additional core logic for level translation or control logic.  $I_{OH}$  is optimized at standard TTL-level V<sub>OH</sub>, and outputs do not swing rail-to-rail for improved noise margins. As a result, UD series ULCs are not recommended for applications which require CMOS output levels or are driving analog circuitry.

The output buffer transistors are designed such that the output current for each output can be programmed depending on user needs. This enables support of the different current requirements of the different PLD and FPGA types. It can also allow the designer to achieve a higher drive capability than on the original PLD or FPGA for selected pins. In many applications, only a select number of outputs need high-current drive. To eliminate the need for excessive ground bussing, the output buffer can be configured in steps of 6 mA to 24 mA.

### Technology

The UD series is unique in the industry in providing small channel lengths and single-layer metal technology. The choice of this technology provides the best available combination of cost and performance for PLD and FPGA conversions.

Single-layer metallization requires only one customization mask. Since mask costs significantly affect minimum order sizes, the single mask required for single-layer metallization makes the UD series the preferred family for ULC conversions up through 100 pins which do not have any special requirements (such as battery back-up) which would dictate the use of another technology.

Historically, the need for dual-layer metal was a function of the intrinsic need for two layers of connections, and the lack of availability of a silicided polysilicon layer for the second connection layer in addition to one layer of metal. Although ordinary polysilicon has been available for such connections and is in fact sometimes used, its resistivity is 500 to 1000 times greater than metal. This prevents its use in high-performance circuits and necessitates dual-layer metal. Silicided polysilicon is roughly 100 times more conductive than ordinary polysilicon and is now available on advanced manufacturing technologies. Although larger devices will require two layers of metal to eliminate the signal skews on long global connections (such as clock signals which would be caused by the interconnect impedance of silicided polysilicon wherever it is used for crossovers), moderate sized devices supported by the UD series do not require two layers of metal due to the small number of crossovers needed.

With single-layer metal technology, excellent routability and utilization are achieved in the UD series through high-density routing channels that are made possible by the dense 0.8-mm technology. An adequate number of routing channels within the cell area allows dense and high-speed intracell connections within macrocells without requiring external routing. A high number of routing channels in the global routing areas further provides easy and efficient inter-macrocell connectivity and thus high performance and high gate utilization. Under certain conditions, routing tracks ordinarily reserved for intracell connections can also be used for intercell connections. Polysilicon connections are only used for short distances across gate banks. The architectural approach of the UD series reduces the need for such connections compared to conventional architectures.

### **I/O Options**

400-mV Schmitt triggers are provided as standard at each input. Outputs can be open collector, tri-state, or internally pulled-up or pulled-down, among many available configurations.

### **3.3-V** Compatibility

Several factors are influencing the growing trend toward 3.3-V circuit operation. Among these are the desire to increase battery operating life, while at the same time decreasing battery weight, improving performance and adding features to notebook and

# **TEMIC** Matra MHS

sub-notebook personal computers. Another is the heat dissipation in ever-denser and faster VLSI semiconductors such as the latest generation of high-performance microprocessor. Despite a growing requirement, a complete complement of 3.3-V system components has been slow to become available.

#### Moving from 5 V to 3.3 V

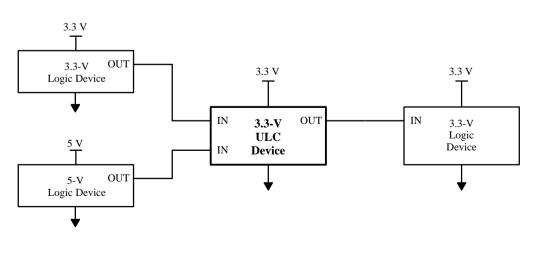

In a design such as a notebook PC which typically would not have to accept standard add-in cards, designing for 3.3 V is relatively easy, if all of the desired components are available at 3.3 V. A tougher case would be the design of a desktop machine which must accept existing 5-V add-in cards and in which the mixing of 5-V parts (plentiful, and cheap) and 3.3-V parts (power consumption and noise issues) is desired. Most 3.3-V devices can't stand more than  $V_{DD}$  + 0.3 V, creating a problem when interfacing with 5-V parts. Interface logic is required for voltage level translation between 5-V and 3.3-V parts. This interface is a unique capability that the UD Series offers.

#### A unique CMOS I/O structure

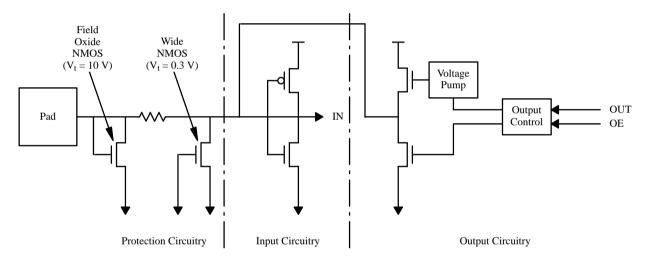

The UD Series I/O structure (Figure 1) has been specifically designed using transistors for input protection instead of the traditional CMOS clamping diodes. Also, the output structure uses an NMOS transistor as a pull-up, instead of the more common PMOS transistor. This allows input signals typically in the 0- to 5-V voltage level range (normal TTL levels are guaranteed), independent of supply voltage with no clamping occurring before the 7-V minimum (Figure 2).

Figure 1. 3-V/5-V Input Compatible I/O Structure

Figure 2. Simple Example of Mixed Power Supply Circuitry

## **Absolute Maximum Ratings**

| Supply Voltage (V_DD) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots -0.3$ V to 7.0 V  |  |

|----------------------------------------------------------------------------------------------------------------|--|

| Input Voltage (V_{IN}) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots -0.3$ V to 7.0 V |  |

| Storage Temperature $\dots -65$ to $150^{\circ}C$                                                              |  |

| $V_{DD}$              |

|-----------------------|

| Operating Temperature |

| Commercial0 to 70°C   |

| Industrial40 to 85°C  |

| Military              |

## **DC Characteristics**

| Parameter                    | Symbol             | <b>Base Part</b><br>T <sub>A</sub> = Commercia         | Min        | Тур  | Max   | Unit |                         |

|------------------------------|--------------------|--------------------------------------------------------|------------|------|-------|------|-------------------------|

|                              |                    | $V_{DD} = 5 \text{ V}, \text{ I}_{OH} \text{ (See N)}$ | Note a)    | 2.4  |       |      |                         |

| Output Voltage               | V <sub>OH</sub>    | V <sub>DD</sub> = 3.3 V, I <sub>OH</sub> (See          | Note b)    | 2.4  |       |      | 1                       |

|                              | V <sub>OL</sub>    | I <sub>OL</sub> (See Note c)                           | )          |      |       | 0.5  | v                       |

| Innut Valtage                | V <sub>IH</sub>    |                                                        |            | 2.0  |       |      | 1                       |

| Input Voltage                | V <sub>IL</sub>    |                                                        |            |      |       | 0.8  | 1                       |

| Input Leakage Current        | I <sub>IX</sub>    | $V_{SS} < V_{IN} < V_{DI}$                             | D          | -10  |       | 10   | mA                      |

| Output Leakage Current       | I <sub>OX</sub>    | $V_{SS} < V_{OUT} < V_{I}$                             | DD         | -10  |       | 10   | IIIA                    |

| Output Short Circuit Current |                    |                                                        | 6 mA       | -75  |       | 75   |                         |

|                              | I <sub>OS</sub>    | Buffer Type<br>V <sub>DD</sub> = 5.25 V                | 12 mA      | -150 |       | 150  | mA<br>mA/<br>MHz/<br>pF |

| Output Short Circuit Current |                    |                                                        | 16 mA      | -200 |       | 200  |                         |

|                              |                    |                                                        | 24 mA      | -300 |       | 300  |                         |

|                              |                    |                                                        | 6 mA       |      | 0.005 |      |                         |

| Dynamic Output Current       | т                  |                                                        | 12 mA      |      | 0.01  |      |                         |

| Dynamic Output Current       | I <sub>OD</sub>    |                                                        | 16 mA      |      | 0.015 |      |                         |

|                              |                    |                                                        | 24 mA      |      | 0.02  |      |                         |

| Stern Iber Comment           | т                  | $V_{DD} = 5.25 \text{ V}, V_{IN} = V_{SS}$             | UD02/03/09 |      | 1     | 8    |                         |

| Standby Current              | I <sub>CSB</sub>   | Outputs Open                                           | UD10–27    |      | 3     | 20   | mA                      |

| Operating Current            | I <sub>DDINT</sub> | •                                                      |            |      | 2     | 5    | mA/<br>Gate/<br>MHz     |

| Input Capacitance            | C <sub>IN</sub>    | $V_{DD} = 5.0 \text{ V}, V_{IN} = 2$                   | 2.0 V      |      |       | 5    | pF                      |

| Output Capacitance           | C <sub>OUT</sub>   | V <sub>OUT</sub> = 2.0 V                               |            |      |       | 4    |                         |

Notes

a.

$I_{OH}$  = -rated limit of selected buffer. Selection determined by FPGA or PLD data sheet requirements.  $I_{OH}$  = -rated limit of selected buffer. Selection determined by FPGA or PLD data sheet requirements. 3.3-V operation not valid for UD10 and b. UD16.

c. I<sub>OH</sub> = rated limit of selected buffer. Selection determined by FPGA or PLD data sheet requirements.

## **Internal Timing Characteristics**

These timing parameters for selected macro cells are provided for information only. Only pin-to-pin timing characteristics are guaranteed for ULCs, and the actual

specification is determined by the original FPGA or PLD data sheet plus any specific parameters that are agreed-to separately by MHS.

$V_{DD}$  = 5 V, typical Process, Statistical Wire Length. All delays measured at  $V_{IN}/V_{OUT}$  = 2.5 V. **Conditions:**

| Масто Туре                 | Parameter | Symbol           | Min | Max (1) <sup>a</sup> | Max (4) <sup>a</sup> | Units |    |

|----------------------------|-----------|------------------|-----|----------------------|----------------------|-------|----|

| 2-Input NAND               | NAND2     |                  | _   |                      | 0.4                  | 0.7   |    |

| 8-Input NAND               | NAND8     |                  |     |                      | 1.0                  | 1.3   |    |

| Inverter                   | INV1      | Propagation Time | tpD |                      | 0.5                  | 0.7   | ns |

| Inverting Tri-State Buffer | TRISTAN   |                  |     |                      | 0.5                  | 1.0   |    |

### Matra MHS

### **Internal Timing Characteristics (Cont'd)**

| Масго Туре                  | Масго Туре |                  | Symbol           | Min | Max (1) <sup>a</sup> | Max (4) <sup>a</sup> | Units |

|-----------------------------|------------|------------------|------------------|-----|----------------------|----------------------|-------|

|                             |            | Setup Time       | t <sub>SU</sub>  | 1.5 |                      |                      |       |

|                             |            | Hold Time        | t <sub>H</sub>   | 0.0 |                      |                      |       |

| Resetable Latch             | LATCHRN    | Pulse Width      | t <sub>PW</sub>  | 2.4 |                      |                      |       |

| Resetable Laten             | LAICHINN   | Propagation Time | t <sub>DQ</sub>  |     | 0.6                  | 0.7                  |       |

|                             |            | Enable Time      | t <sub>EN</sub>  |     | 0.8                  | 1.3                  |       |

|                             |            | Reset Time       | t <sub>RN</sub>  |     | 0.3                  | 0.5                  |       |

|                             |            | Setup Time       | t <sub>SU</sub>  | 1.5 |                      |                      |       |

|                             |            | Hold Time        | t <sub>H</sub>   | 0.0 |                      |                      |       |

| D Flip-Flop with Reset      | DFFRN      | Pulse Width      | t <sub>PW</sub>  | 2.4 |                      |                      |       |

|                             |            | Clock Delay Time | t <sub>CQ</sub>  |     | 0.7                  | 1.1                  |       |

|                             |            | Reset Time       | t <sub>RN</sub>  |     | 0.7                  | 1.1                  |       |

| TTL Compatible Input Buffer | BUFINTTL   |                  | t <sub>PLH</sub> |     | 0.4                  | 0.6                  | ns    |

| TTL Companyie input Burler  | BUFINTIL   |                  | tPHL             |     | 1.0                  | 1.2                  |       |

| TTL Compatible I/O Buffer   | BIOTN4     |                  | t <sub>PLH</sub> |     | 0.4                  | 0.6                  |       |

| Input Mode                  | BIOTIN4    |                  | tPHL             |     | 1.0                  | 1.2                  |       |

| Output Buffer               | BON4       | Propagation Time | t <sub>PLH</sub> |     | 3.2                  | 8.3                  |       |

| Output Buner                | BOIN4      | Tiopagation Time | t <sub>PHL</sub> |     | 1.8                  | 2.6                  |       |

| TTL Compatible I/O Buffer   | BIONTN4    |                  | t <sub>PLH</sub> |     | 3.2                  | 8.3                  |       |

| 1 1L Companyie 1/O Burler   | BION IN4   |                  | tPHL             |     | 1.8                  | 2.6                  |       |

|                             |            | 1                | t <sub>PLH</sub> |     | 3.2                  | 8.3                  |       |

| Tri State Output Duffer     | BIO3N4     |                  | t <sub>PHL</sub> |     | 1.8                  | 2.6                  |       |

| Tri-State Output Buffer     | BI051N4    | Enable Time      | t <sub>PZH</sub> |     | 3.2                  | 8.3                  |       |

|                             |            | Enable Time      | t <sub>PZL</sub> |     | 1.8                  | 2.6                  |       |

Notes

a. Fan-outs for internal connection are: F01 = 1 internal load, F04 = 4 internal loads. Fanouts for output buffers are: F01 = 25 pF, F04 = 100 pF. Max values are provided for worst case of  $T_{HL}$  pr  $T_{LH}$  for internal cells.

#### **Derating Factors:** $t_P = K_P x K_t x K_V x t_{NOMINAL}$

| Process                |                |      |      |     |                     |      |           |       |      |       |      |      |      |

|------------------------|----------------|------|------|-----|---------------------|------|-----------|-------|------|-------|------|------|------|

| Pro                    | cess           |      | В    | est |                     |      | Non       | ninal |      | Worst |      |      |      |

| K                      | SP             | 0.75 |      |     |                     |      | 1.00      |       |      |       | 1.33 |      |      |

| Ambient Temperature °C |                |      |      |     |                     |      |           |       |      |       |      |      |      |

| T <sub>A</sub>         | -55            | _4   | 10   | (   | )                   | 2    | 5         | 7     | 0    | 8     | 85   |      | 25   |

| K <sub>T</sub>         | 0.71           | 0.1  | 76   | 0.9 | 0.91 1.00 1.16 1.22 |      | 1.00 1.16 |       | 22   | 1.36  |      |      |      |

| Supply Voltage         | Supply Voltage |      |      |     |                     |      |           |       |      |       |      |      |      |

| V                      | DD             | 3    | 3.13 | 3.3 | 3.47                | 3.63 | 4         | 4.5   | 4.75 | 5     | 5.25 | 5.5  | 6    |

| K                      | ζv             | 1.67 | 1.59 | 1.5 | 1.42                | 1.36 | 1.22      | 1.08  | 1.03 | 1     | 0.97 | 0.96 | 0.95 |

# **External Timing Characteristics**

#### (Over the Operating Range)

These timing parameters are provided for information only. Actual pin-to-pin timing characteristics guaranteed for ULCs are determined by the original FPGA or PLD data sheet plus any specific parameters that are agreed to separately by MHS.

|                    |                 |                  |      | M    | [ax  |      |

|--------------------|-----------------|------------------|------|------|------|------|

| Parameter          | Symbol          | <b>Base Part</b> | Min  | Тур  | Max  | Unit |

|                    |                 | UD02             |      | 7.0  | 11.5 |      |

|                    |                 | UD03             |      | 7.0  | 11.5 |      |

|                    |                 | UD09             |      | 8.0  | 13.0 |      |

| Propagation Time   | tpD             | UD10             |      | 8.0  | 13.0 |      |

|                    |                 | UD14             |      | 9.0  | 14.5 |      |

|                    |                 | UD16             |      | 9.0  | 14.5 | 1    |

|                    |                 | UD27             |      | 10.0 | 16.0 |      |

|                    |                 | UD02             |      | 8.0  | 13.0 |      |

|                    |                 | UD03             |      | 8.0  | 13.0 | 1    |

|                    |                 | UD09             |      | 10.0 | 16.0 |      |

| Clock Delay Time   | t <sub>CO</sub> | UD10             |      | 10.0 | 16.0 |      |

|                    |                 | UD14             |      | 12.0 | 19.5 | ns   |

|                    |                 | UD16             |      | 12.0 | 19.5 |      |

|                    |                 | UD27             |      | 14.0 | 22.5 |      |

| Hold Time          | t <sub>H</sub>  |                  | 0.0  |      |      |      |

|                    |                 | UD02             |      | 8.0  | 13.0 |      |

|                    |                 | UD03             |      | 8.0  | 13.0 |      |

|                    |                 | UD09             | UD09 | 10.0 | 16.0 |      |

| Output Enable Time | t <sub>EN</sub> | UD10             |      | 10.0 | 16.0 |      |

|                    |                 | UD14             |      | 12.0 | 19.5 |      |

|                    |                 | UD16             |      | 12.0 | 19.5 |      |

|                    |                 | UD27             |      | 14.0 | 22.5 |      |

Matra MHS

### **Power Consumption**

#### **Dynamic Power Consumption for UD Series ULCs**

There are four main factors to consider:

1. Static power dissipation of the core is negligible compared to the internal backbias generator pump, so:

$P_{CSB} = I_{CSB} * V_{DD}$

2. Static power dissipation in I/O buffers:

$\begin{aligned} P_1 = V_{OL} * S_n \left( I_{OLn} * N_{BUFn} \right) + V_{OH} * S_n (I_{OHn} * N_{BUFn}) \end{aligned}$

where:

$N_n$  is the number of outputs of type n being driven to  $V_{OL} \label{eq:Vol}$

$M_n$  is the number of outputs of type n being driven to  $V_{\mbox{OH}}$

3. Dynamic power dissipation for the internal gates:

$$\label{eq:P2} \begin{split} P_2 = V_{DD} * I_{DDINT} * S_g \left(N_f * f_g\right) \\ \text{where:} \end{split}$$

$N_f$  = number of gates toggling at frequency f

$f_g = Clock$  frequency of internal logic in MHz

Note: A usual rule of thumb is to assume that the average used gate is toggling 1/2-input clock.

4. Dynamic power dissipation in the outputs:

### **Typical ULC Test Conditions**

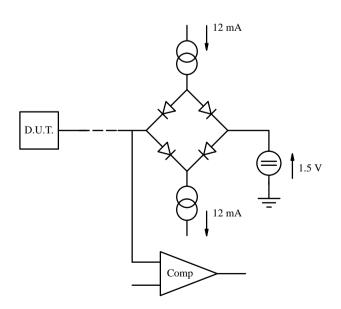

For ac specification purposes, an improved output loading scheme has been defined for MHS high-drive (24 mA), high-speed ULC devices. The schematic below (Figure 1) describes the typical conditions for testing these ULC devices, using the standard loading scheme commonly available on high-end ATE.

Compared to a no-load condition, this provides the following advantages:

- Output load is more representative of "real life" conditions during transitions.

- Transient energy is absorbed at the end of the line to prevent reflections which would lead to inaccurate ATE measurements.

$P_3 = V_{DD} * S_n (f_n * I_{ODn} * C_n)$

where:

$f_n = Clocking frequency in MHz of output n$

$C_n$  = Output load capacitance in pF of output n

Global Formula:

$\mathbf{P} = \mathbf{P}_{CSB} + \mathbf{P}_1 + \mathbf{P}_2 + \mathbf{P}_3$

Example:

We take a 16-bit resettable ripple counter which is approximately 100 gates, operating at a clock frequency of 33 MHz, which gives an average clock frequency of 33 MHz/16 for each bit and each output. There are no static output on this device. Operation is at 5 V, and 6-mA outputs are used and loaded at 25 pF. The output buffers are driving TTL logic, i.e. sinking 24 mA and sourcing a few hundred mA. This is implemented with the UD03 base

$$P_{CSB} = 8 * 5 = 40 \text{ mW}$$

$P_1 = 0.4 * 6 * 2 = 0$

$P_2 = 5 * 0.005 * 100 * 33/16 = 5 \text{ mW}$

$P_3 = 5 * 16 * 33/16 * 0.02 * 25 = 83 \text{ mW}$

P = 40 + 0 + 5 + 83 = 128 mW

Figure 3. Typical ULC Test Conditions

# **TEMIC** Matra MHS

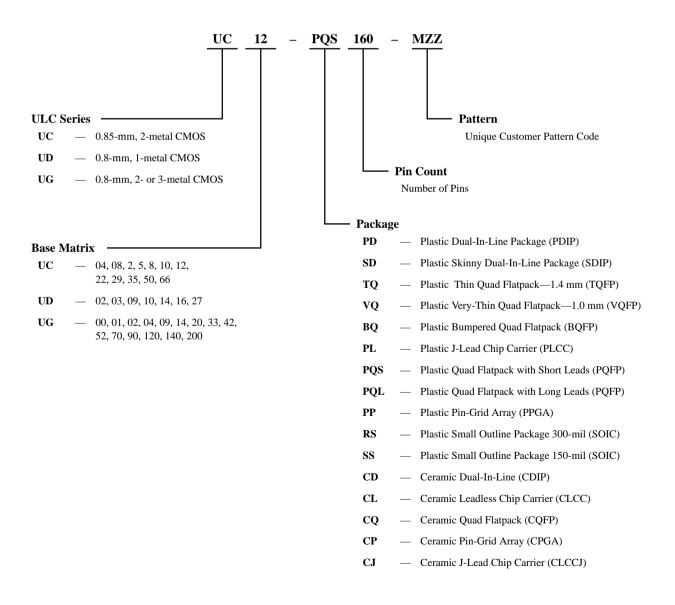

Prior to conversion, ULCs are referred to by a generic ULC part number and separate package designation plus an optional temperature range formed as follows:

ULC/ base PLD or FPGA pins-package

where base PLD or FPGA refers to 22 V, 10 or EPM7128 or XC3030

#### Example:

ULC part number for XC3030A-5PL84C would be: ULC/XC3030, 84-PLCC

After conversion, a specific ULC code is ordered as follows: