# **Time Code Receiver**

#### Description

The U4223B is a bipolar integrated straight through receiver circuit in the frequency range of 40 to 80 kHz. The device is designed for radio controlled clock applications.

#### Features

- Very low power consumption

- Very high sensitivity

- High selectivity by using two crystal filters

- Power down mode available

- Only a few external components necessary

- 4 bit digital output

- AGC hold mode

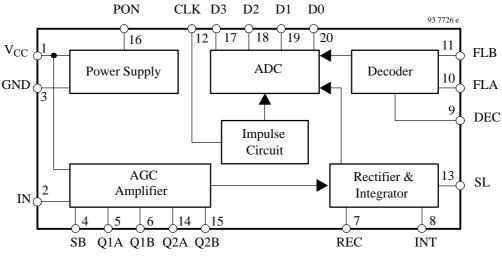

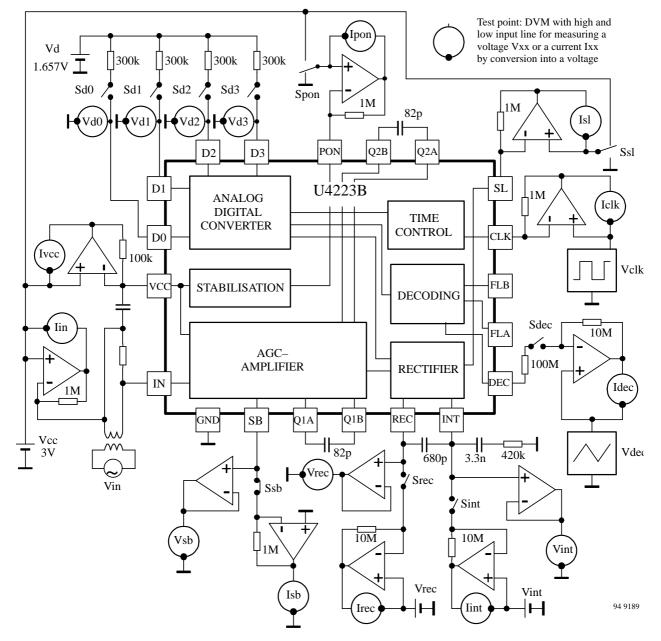

#### **Block Diagram**

Figure 1.

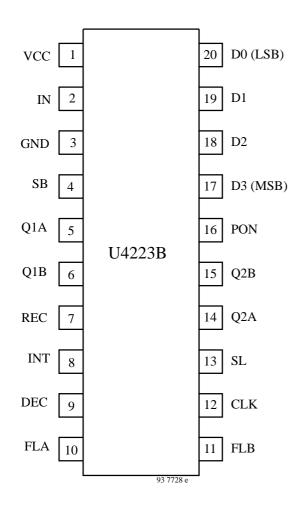

#### **Pin Description**

| Pin   | Pin   | Symbol          | Function             |

|-------|-------|-----------------|----------------------|

| SO20L | SSO20 |                 |                      |

| 1     | 1     | V <sub>CC</sub> | Supply voltage       |

| 2     | 2     | IN              | Amplifier – Input    |

| 3     | 3     | GND             | Ground               |

| 4     | 4     | SB              | Bandwidth control    |

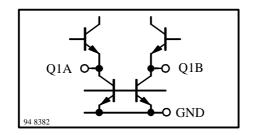

| 5     | 5     | Q1A             | Crystal filter 1     |

| 6     | 6     | Q1B             | Crystal filter 1     |

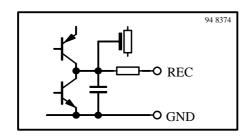

| 7     | 7     | REC             | Rectifier output     |

| 8     | 8     | INT             | Integrator output    |

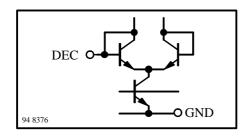

| 9     | 9     | DEC             | Decoder input        |

| 10    | 10    | FLA             | Low pass filter      |

| 11    | 11    | FLB             | Low pass filter      |

| 12    | 12    | CLK             | Clock input for ADC  |

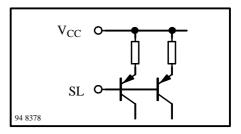

| 13    | 13    | SL              | AGC hold mode        |

| 14    | 14    | Q2A             | Crystal filter 2     |

| 15    | 15    | Q2B             | Crystal filter 2     |

| 16    | 16    | PON             | Power ON/OFF control |

| 17    | 17    | D3              | Data out MSB         |

| 18    | 18    | D2              | Data out             |

| 19    | 19    | D1              | Data out             |

| 20    | 20    | D0              | Data out LSB         |

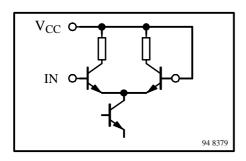

#### IN

A ferrite antenna is connected between IN and  $V_{CC}$ . For high sensitivity the Q of the antenna circuit should be as high as possible, but a high Q often requires temperature compensation of the resonant frequency. Specifications are valid for Q>30. An optimal signal to noise ratio will be achieved by a resonant resistance of 50 to 200 k $\Omega$ .

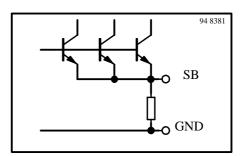

#### SB

A resistor  $R_{SB}$  is connected between SB and GND. It controls the bandwidth of the crystal filters. It is recommended:  $R_{SB}$  = 0  $\Omega$  for DCF 77.5 kHz,  $R_{SB}$  = 10 k $\Omega$  for 60 kHz WWVB and  $R_{SB}$  = open for JG2AS 40 kHz.

### Q1A, Q1B

In order to achieve a high selectivity, a crystal is connected between the pins Q1A and Q1B. It is used with the serial resonance frequency of the time code transmitter (e.g. 60 kHz WWVB, 77.5 kHz DCF or 40kHz JG2AS).

The equivalent parallel capacitor of the filter crystal is internally compensated. The compensated value is about 0.7 pF. If the full sensitivity and selectivity is not needed, the crystal filter can be substituted by a capacitor of 82 pF.

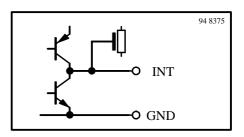

#### REC

Rectifier output and integrator input: The capacitor C1 between REC and INT is the lowpass filter of the rectifier and at the same time a damping element of the gain control.

#### DEC

Decoder input: Senses the current through the integration capacitor C2. The dynamic input resistance has a value of about  $420k\Omega$  and is low compared to the impedance of C2.

**TELEFUNKEN Semiconductors** Rev. A3, 02-Apr-96

#### SL

AGC hold mode: SL high ( $V_{SL} = V_{CC}$ ) sets normal function, SL low ( $V_{SL} = 0$ ) disconnects the rectifier and holds the voltage  $V_{INT}$  at the integrator output and also the AGC amplifier gain.

#### INT

Integrator output: The voltage  $V_{INT}$  is the control voltage for the AGC. The capacitor C2 between INT and DEC defines the time constant of the integrator. The current through the capacitor is the input signal of the decoder.

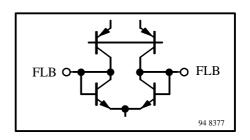

#### FLA, FLB

Lowpass filter: A capacitor C3 connected between FLA and FLB supresses higher frequencies at the trigger circuit of the decoder.

# U4223B

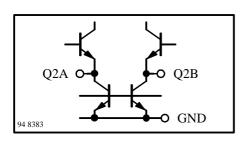

## Q2A, Q2B

According to Q1A, Q1B a crystal is connected between the pins Q2A and Q2B. It is used with the serial resonance frequency of the time code transmitter (e.g. 60 kHz WWVB, 77.5 kHz DCF or 40 kHz JG2AS). The equivalent parallel capacitor of the filter crystal is internally compensated. The value of the compensation is about 0.7 pF.

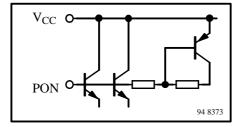

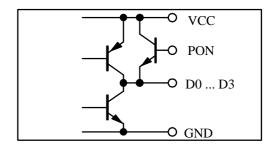

### PON

If PON is connected to GND, the U 4224 B receiver IC will be activated. The set-up time is typical 0.5s after applying GND at this pin. If PON is connected to  $V_{CC}$ , the receiver will go into power down mode.

#### D0, D1, D2, D3

The outputs of the ADC consist of pnp-npn push-pull stages and can be directly connected to a microcomputer. In order to avoid any interference of the output into the antenna circuit we recommend terminating each digital output with a capacitor of 10 nF. The digitalized signal of the ADC is Gray coded (see table). It should be taken into account that in the power down mode (PON = high) D0, D1, D2 and D3 will be high.

| Decimal | Gray |

|---------|------|

| 0       | 0000 |

| 1       | 0001 |

| 2       | 0011 |

| 3       | 0010 |

| 4       | 0110 |

| 5       | 0111 |

| 6       | 0101 |

| 7       | 0100 |

| 8       | 1100 |

| 9       | 1101 |

| 10      | 1111 |

| 11      | 1110 |

| 12      | 1010 |

| 13      | 1011 |

| 14      | 1001 |

| 15      | 1000 |

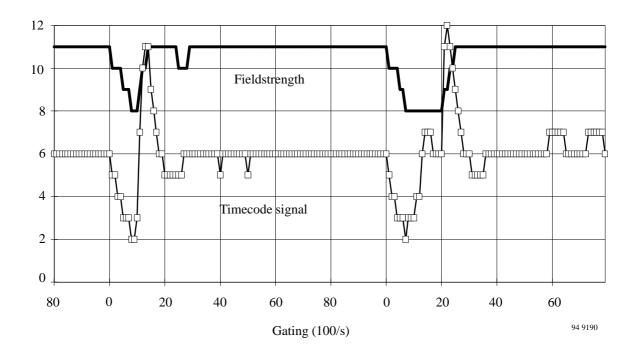

A sequence of the digitalized time code signal can be ana-

lysed by a special noise suppressing algorithm in order to increase the sensitivity and the signal to noise ratio (more

than 10 dB compared to a conventional decoding). De-

tails about the time code format are described separately.

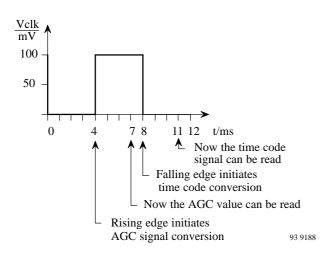

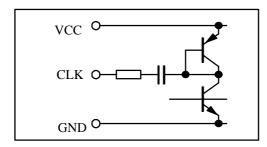

#### CLK

The input of the ADC is switched to the AGC voltage by the rising edge of the clock. After the conversion time (about 1.8 ms at 25°C) the digitalized field strength signal is stored in the output registers D0 to D3 as long as the clock is high and can be read by a microcomputer. The falling edge of the clock switches the input of the ADC to the time code signal. After the conversion time the digitalized time code signal is stored in the output registers D0 to D3 as long as the clock is low (see figure below).

## TEMIC Semiconductors

In order to minimize interferences we recommend a voltage swing of about 100 mV. A full supply voltage swing is possible but it reduces the sensitivity.

#### Please note:

The signals and voltages at the pins REC, INT, FLA, FLB, Q1A, Q1B, Q2A and Q2B cannot be measured by standard measurement equipment due to very high internal impedances. For the same reason the PCB should be protected against surface humidity.

#### **Design Hints for the Ferrite Antenna**

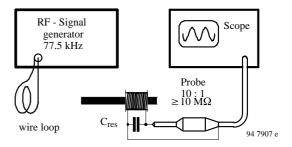

The bar antenna is a very critical device of the complete clock receiver. But by observing some basic RF design knowledge, no problem should arise with this part. The IC requires a resonance resistance of 50 k $\Omega$  to 200 k $\Omega$ . This can be achieved by a variation of the L/C-relation in the antenna circuit. But it is not easy to measure such high resistances in the RF region. It is much more convenient to distinguish the bandwidth of the antenna circuit and afterwards to calculate the resonance resistance.

Thus the first step in designing the antenna circuit is to measure the bandwidth. Figure 4 shows an example for the test circuit. The RF signal is coupled into the bar antenna by inductive means, e.g. a wire loop. It can be measured by a simple oscilloscope using the 10:1 probe. The input capacitance of the probe, typically about 10 pF, should be taken into consideration. By varying the frequency of the signal generator, the resonance frequency can be determined.

Afterwards, the two frequencies where the voltage of the rf signal at the probe drops 3 dB down can be measured. The difference between these two frequencies is called the bandwidth  $BW_A$  of the antenna circuit. As the value of the capacitor  $C_{res}$  in the antenna circuit is well known, it is easy to compute the resonance resistance according to the following formula:

$$\mathbf{R}_{\mathrm{res}} = \frac{1}{2 \cdot \pi \cdot \mathbf{B} \mathbf{W}_{\mathrm{A}} \cdot \mathbf{C}_{\mathrm{res}}}$$

whereas

R<sub>res</sub> is the resonance resistance,

$BW_{\!A}$  is the measured bandwidth (in Hz)

$C_{res}\xspace$  is the value of the capacitor in the antenna circuit (in Farad)

If high inductance values and low capacitor values are used, the additional parasitic capacitances of the coil must be considered. It may reach up to about 20 pF. The Q-value of the capacitor should be no problem if a high Q-type is used. The Q-value of the coil is more or less distinguished by the simple DC-resistance of the wire. Skin effects can be observed but do not dominate.

Therefore it shouldn't be a problem to achieve the recommended values of resonance resistance. The use of thicker wire increases Q and accordingly reduces bandwidth. This is advantageous in order to improve reception in noisy areas. On the other hand, temperature compensation of the resonance frequency might become a problem if the bandwidth of the antenna circuit is low compared to the temperature variation of the resonance frequency. Of course, Q can also be reduced by a parallel resistor. Temperature compensation of the resonance frequency is a must if the clock is used at different temperatures. Please ask your dealer of bar antenna material and of capacitors for specified values of temperature coefficient.

Furthermore some critical parasitics have to be considered. These are shortened loops (e.g. in the ground line of the PCB board) close to the antenna and undesired loops in the antenna circuit. Shortened loops decrease Q of the circuit. They have the same effect like conducting plates close to the antenna. To avoid undesired loops in the antenna circuit it is recommended to mount the capacitor  $C_{res}$  as close as possible to the antenna coil or to use a

twisted wire for the antenna coil connection. This twisted line is also necessary to reduce feedback of noise from the microprocessor to the IC input. Long connection lines must be shielded.

A final adjustment of the time code receiver can be done by pushing the coil along the bar antenna. The maximum of the integrator output voltage  $V_{INT}$  at pin INT indicates the resonant point. But attention: The load current should not exceed 1 nA, that means an input resistance  $\geq 1 \text{ G}\Omega$ of the measuring device is required. Therefore a special DVM or an isolation amplifier is necessary.

#### **Absolute Maximum Ratings**

| Parameters                                                                    | Symbol           | Value      | Unit |

|-------------------------------------------------------------------------------|------------------|------------|------|

| Supply voltage                                                                | V <sub>CC</sub>  | 5.25       | V    |

| Ambient temperature range                                                     | T <sub>amb</sub> | -25 to +75 | °C   |

| Storage temperature range                                                     | R <sub>stg</sub> | -40 to +85 | °C   |

| Junction temperature                                                          | Tj               | 125        | °C   |

| Electrostatic handling<br>(MIL Standard 883 D), excepted pins 5, 6, 14 and 15 | $\pm V_{ESD}$    | 2000       | V    |

#### **Thermal Resistance**

| Parameters         | Symbol            | Maximum | Unit |

|--------------------|-------------------|---------|------|

| Thermal resistance | R <sub>thJA</sub> | 70      | K/W  |

### **Electrical Characteristics**

$V_{CC}$  = 3 V, reference point pin 3, input signal frequency 80 kHz,  $T_{amb}$  = 25 °C, unless otherwise specified

| Parameters                              | Test Conditions / Pin                                                                                                              | Symbol                                   | Min                  | Тур             | Max                  | Unit           |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------|-----------------|----------------------|----------------|

| Supply voltage range                    | pin 1                                                                                                                              | V <sub>CC</sub>                          | 1.2                  |                 | 5.25                 | V              |

| Supply current                          | pin 1<br>without reception signal<br>with reception signal = 200µV<br>OFF-mode                                                     | I <sub>CC</sub>                          |                      | 15              | 30<br>25<br>0.1      | μΑ<br>μΑ<br>μΑ |

| Set-up time after<br>V <sub>CC</sub> ON | $V_{\rm CC} = 1.5 \text{ V}$                                                                                                       | t                                        |                      | 2               |                      | s              |

| AGC AMPLIFIER INPUT;                    | IN pin 2                                                                                                                           |                                          |                      |                 |                      |                |

| Reception frequency range               |                                                                                                                                    | f <sub>in</sub>                          | 40                   |                 | 80                   | kHz            |

| Minimum input voltage                   | $R_{res} = 100 \text{ k}\Omega, \ Q_{res} > 30$                                                                                    | V <sub>in</sub>                          |                      | 1               | 1.5                  | μV             |

| Maximum input voltage                   |                                                                                                                                    | Vin                                      | 40                   | 80              |                      | mV             |

| Input capacitance to ground             |                                                                                                                                    | C <sub>in</sub>                          |                      | 1.5             |                      | pF             |

| ADC; <b>D0, D1, D2, D3</b>              | pin 17, 18, 19, 20                                                                                                                 |                                          |                      |                 |                      |                |

| Output voltage<br>HIGH<br>LOW           | $\label{eq:RLOAD} \begin{split} R_{LOAD} &= 870 \; k\Omega \; to \; GND \\ R_{LOAD} &= 650 \; k\Omega \; to \; V_{CC} \end{split}$ | V <sub>OH</sub><br>V <sub>OL</sub>       | V <sub>CC</sub> -0.4 |                 | 0.4                  | V<br>V         |

| Output current<br>HIGH<br>LOW           | $V_{TCO} = V_{CC}/2$<br>$V_{TCO} = V_{CC}/2$                                                                                       | I <sub>SOURCE</sub><br>I <sub>SINK</sub> | 3<br>4               | 10<br>12        |                      | μΑ<br>μΑ       |

| Input current into DEC (first bit)      | falling edge of CLK                                                                                                                | I <sub>decs</sub>                        | -32                  | -25             | -18                  | nA             |

| Input current into DEC (last bit)       | falling edge of CLK                                                                                                                | I <sub>dece</sub>                        | 28                   | 35              | 42                   | nA             |

| Input current into DEC (step range)     | falling edge of CLK                                                                                                                | I <sub>decst</sub>                       | 1.75                 | 4               | 7                    | nA             |

| Input voltage at IN<br>(first bit)      | RF generator at IN, without<br>modulation<br>rising edge of CLK                                                                    | V <sub>min</sub>                         |                      | -10             |                      | dBμV           |

| Input voltage at IN<br>(last bit)       | RF generator at IN, without<br>modulation<br>rising edge of CLK                                                                    | V <sub>max</sub>                         |                      | 60              |                      | dBμV           |

| Input voltage at IN<br>(step range)     | RF generator at IN, without<br>modulation<br>rising edge of CLK                                                                    | V <sub>step</sub>                        |                      | 4.7             |                      | dBμV           |

| CLOCK INPUT; CLK                        | pin 12                                                                                                                             |                                          |                      |                 |                      |                |

| Input voltage swing                     |                                                                                                                                    | V <sub>swing</sub>                       | 50                   | 100             | V <sub>CC</sub>      | mV             |

| Clock frequency                         |                                                                                                                                    | f <sub>clk</sub>                         |                      | 100             | 125                  | Hz             |

| Dynamical input resistance              |                                                                                                                                    | R <sub>dyn.</sub>                        |                      | 100             |                      | kΩ             |

| POWER ON/OFF CONTRO                     | , <u>1</u>                                                                                                                         | 1                                        | ,                    |                 | 1                    |                |

| Input voltage<br>HIGH<br>LOW            | Required I <sub>IN</sub> $\geq 0.5 \mu\text{A}$                                                                                    |                                          | V <sub>CC</sub> -0.2 |                 | V <sub>CC</sub> -1.2 | V<br>V         |

| Input current                           | $V_{CC} = 3V$ $V_{CC} = 1.5 V$ $V_{CC} = 5 V$                                                                                      | I <sub>IN</sub>                          | 1.4                  | 1.7<br>0.7<br>3 | 2                    | μΑ<br>μΑ<br>μΑ |

| Set-up time after PON                   |                                                                                                                                    | t                                        |                      | 0.5             | 2                    | S              |

# U4223B

| Parameters                        | Test Conditions / Pin                           | Symbol                           | Min                  | Тур      | Max                  | Unit     |

|-----------------------------------|-------------------------------------------------|----------------------------------|----------------------|----------|----------------------|----------|

| AGC HOLD MODE; SL                 | pin 13                                          |                                  |                      |          |                      |          |

| Input voltage<br>HIGH<br>LOW      | Required I <sub>IN</sub> $\geq 0.5 \mu\text{A}$ |                                  | V <sub>CC</sub> -0.2 |          | V <sub>CC</sub> -1.2 | V<br>V   |

| Input current                     | $Vin = V_{CC}$<br>Vin = GND                     |                                  |                      | 2.5      | 0.1                  | μΑ<br>μΑ |

| Rejection of interference signals |                                                 | a <sub>f</sub><br>a <sub>f</sub> |                      | 43<br>22 |                      | dB<br>dB |

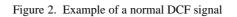

**Test Circuit (for Fundamental Function)**

Figure 3. Example of a disturbed DCF signal

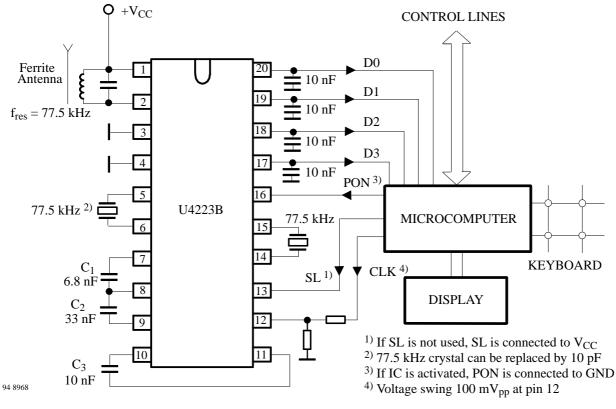

#### **Application Circuit for DCF 77.5 kHz**

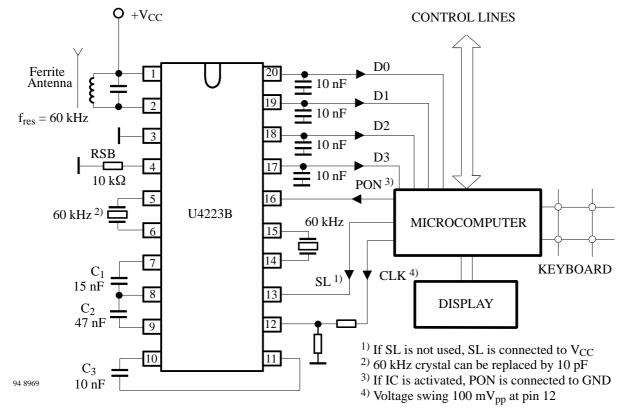

#### Application Circuit for WWVB 60 kHz

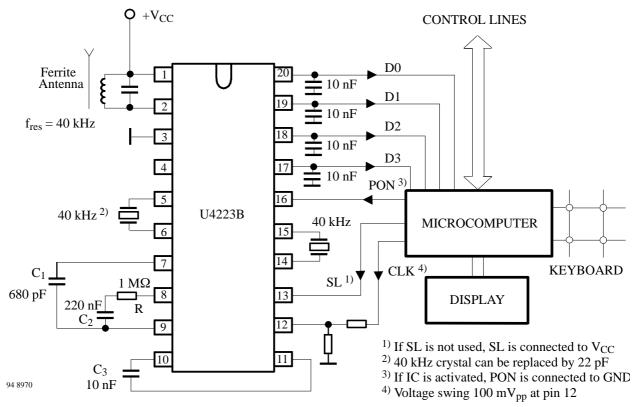

#### Application Circuit for JG2AS 40 kHz

U4223B

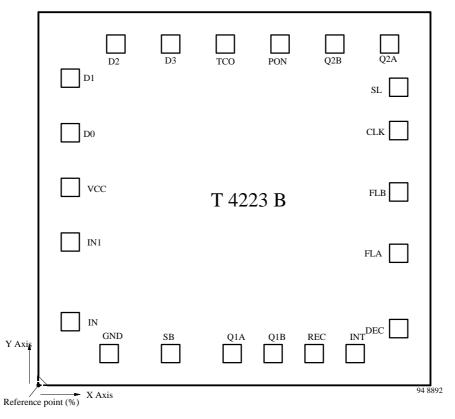

#### **PAD Coordinates**

The T 4223 B is also available as die for "Chip on board" mounting.

DIE size: 2.26 x 2.09 mm

PAD size:  $100 \times 100 \mu m$  (contact window 88 x 88  $\mu m$ ) Thickness:  $300 \mu m \pm 20 \mu m$

| SYMBOL | X-Axis/µm | Y-Axis/µm |

|--------|-----------|-----------|

| IN1    | 128       | 758       |

| IN     | 128       | 310       |

| GND    | 354       | 124       |

| SB     | 698       | 128       |

| Q1A    | 1040      | 128       |

| Q1B    | 1290      | 128       |

| REC    | 1528      | 128       |

| INT    | 1766      | 128       |

| DEC    | 2044      | 268       |

| FLA    | 2044      | 676       |

| FLB    | 2044      | 1012      |

| SYMBOL | X-Axis/µm | Y-Axis/µm |

|--------|-----------|-----------|

| CLK    | 2044      | 1372      |

| SL     | 2044      | 1624      |

| Q2A    | 1980      | 1876      |

| Q2B    | 1634      | 1876      |

| PON    | 1322      | 1876      |

| ТСО    | 1008      | 1876      |

| D3     | 696       | 1876      |

| D2     | 384       | 1876      |

| D1     | 128       | 1682      |

| D0     | 128       | 1368      |

| VCC    | 128       | 1098      |

The PAD coordinates are referred to the left bottom point of the contact window.

#### **PAD Layout**

#### **Information Regarding German Transmitter**

Station: DCF 77, Frequency 77.5 kHz, Transmitting power 50 kW Location: Mainflingen/Germany, Geographical coordinates: 50° 0.1'N, 09° 00'E Time of transmission: permanent

#### **Modulation:**

The carrier amplitude is reduced to 25 % at the beginning of each second for 100 ms (binary zero) or 200 ms (binary one) duration, excepting the 59th second.

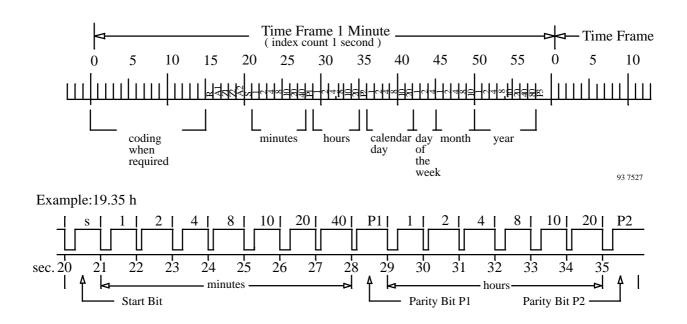

#### **Time Code Format: (based on Information of Deutsche Bundespost)**

It consists of 1 minute time frames. No modulation at the beginning of the 59th second to recognize the switch over

to the next 1 minute time frame. A time frame contains BCD–coded information of minutes, hours, calendar day, day of the week, month and year between the 20th second and 58th second of the time frame, including the start bit S (200 ms) and parity bits P1, P2 and P3. Further there are 5 additional bits R (transmission by reserve antenna), A1 (announcement of change–over to the summer time), Z1 (during the summer time 200 ms, otherwise 100 ms), Z2 (during standard time 200 ms otherwise 100 ms) and A2 (announcement of leap second) transmitted between the 15th second and 19th second of the time frame.

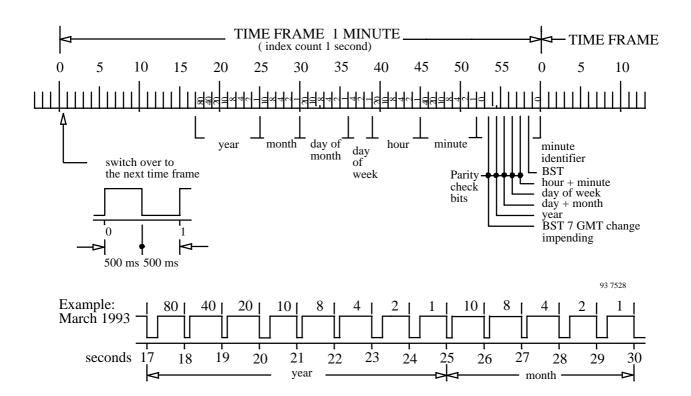

#### **Information Regarding British Transmitter**

Station: MSF Frequency 60 kHz Transmitting power 50 kW Location: Teddington, Middlesex Geographical coordinates:  $52^{\circ}$  22'N,  $01^{\circ}$  11'W Time of transmission: permanent, excepting the first tuesday of each month from 10.00 h to 14.00 h.

#### Modulation:

The carrier amplitude is switched off at the beginning of each second for the time of 100 ms (binary zero) or 200 ms (binary one).

#### **Time Code Format:**

It consists of 1 minute time frames. A time frame contains BCD–coded information of year, month, calendar day, day of the week, hours and minutes. At the switch–over to the next time frame, the carrier amplitude is reduced for 500 ms duration.

The prescence of the fast code during the first 500 ms at the beginning of the minute in not guaranteed. The transmission rate is 100 bits/s and the code contains information of hour, minute, day and month.

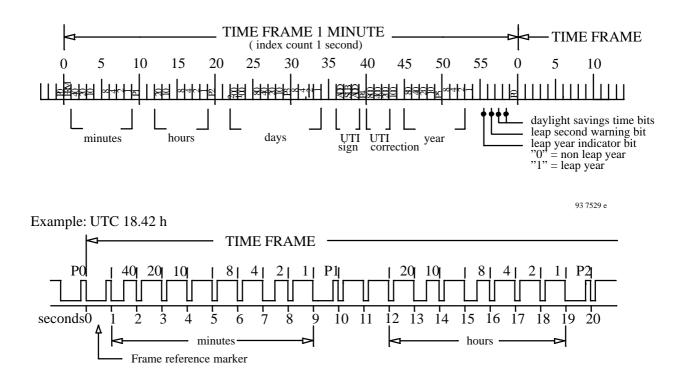

#### **Information Regarding US Transmitter**

Station: WWVB Frequency 60 kHz Transmitting power 10 kW Location: Fort Collins Geographical coordinates:  $40^{\circ}$  40'N,  $105^{\circ}$  03'W Time of transmission: permanent.

#### **Modulation:**

The carrier amplitude is reduced 10 dB at the beginning of each second and is restored in 500 ms (binary one) or in 200 ms (binary zero).

#### **Time Code Format:**

It consists of 1 minute time frames. A time frame contains BCD–coded information of minutes, hours, days and year. In addition there are 6 position identifier markers (P0 thru P5) and 1 frame reference marker with reduced carrier amplitude of 800 ms duration.

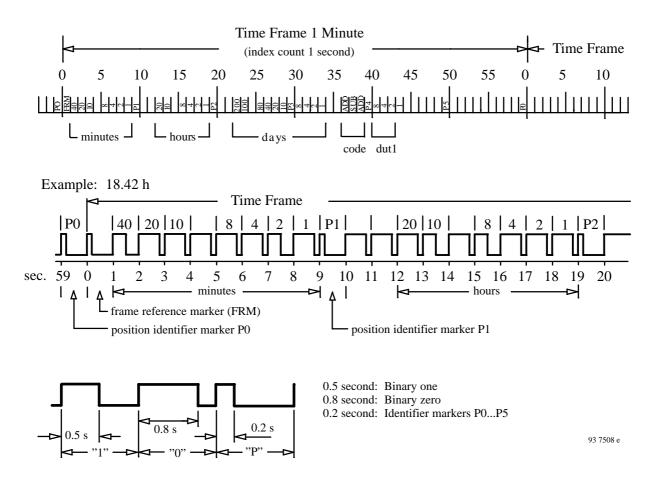

#### **Information Regarding Japanese Transmitter**

Station: JG2AS Frequency 40 kHz Transmitting power 10 kW Location: Sanwa, Ibaraki Geographical coordinates: 36° 11' N, 139° 51' E Time of transmission: permanent

#### **Modulation:**

The carrier amplitude is 100% at the beginning of each second and is switched off after 500 ms (binary one) or after 800 ms (binary zero).

#### **Time Code Format:**

It consists of one minute time frame. A time frame contains BCD–coded information of minutes, hours and days. In addition there are 6 position identifier markers (P0 thruP5) and one frame reference markers (FRM) with reduced carrier amplitude of 800 ms duration.

#### **Ordering and Package Information**

| Extended type number | Package        | Remarks                       |

|----------------------|----------------|-------------------------------|

| U4223B-CFL           | SO 20 plastic  |                               |

| U4223B-CFLG3         | SO 20 plastic  | Taping according to IEC–286–3 |

| U4223B-CFS           | SSO 20 plastic |                               |

| U4223B-CFSG3         | SSO 20 plastic | Taping according to IEC-286-3 |

| T4223B-CF            | no             | die on foil                   |

| T4223B-CC            | no             | die on carrier                |

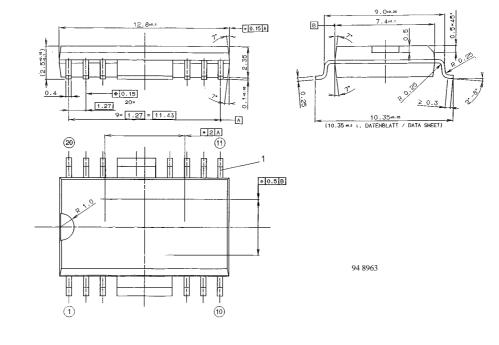

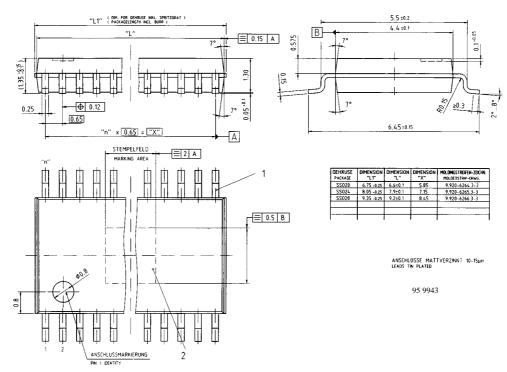

#### **Dimensions in mm**

#### Package: SO20

Package: SSO20

### **Ozone Depleting Substances Policy Statement**

#### It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423