## **Low-Power Audio Amplifier for Telephone Applications**

### **Description**

The integrated circuit, U4083B, is a low power audio amplifier for a telephone loudspeaker. It has differential speaker outputs to maximize the output swing at low supply voltages. There is no need for coupler capacitors.

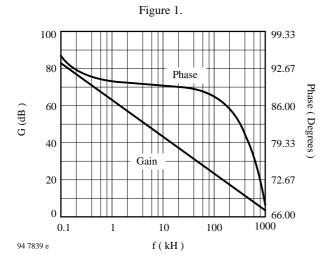

The U4083B has an open loop gain of 80 dB whereas the closed loop gain is adjusted with two external resistors. A chip disable pin permits powering down and/or muting the input signal.

#### **Features**

- Wide operating voltage range: 2 to 16 V

- Battery powered application due to low quiescent supply current: 2.7 mA typical

- Chip disable input to power down the integrated circuit

- Low power down quiescent current

- Drives a wide range of speaker loads

- Output Power,  $P_0 = 250 \text{ mW} @ R_L = 32 \Omega \text{ (speaker)}$

- Low harmonic distortion (0.5% typical)

- Wide range gain adjustable: 0 dB to 46 dB

#### **Benefits**

- Low number of external components

- Low current consumption

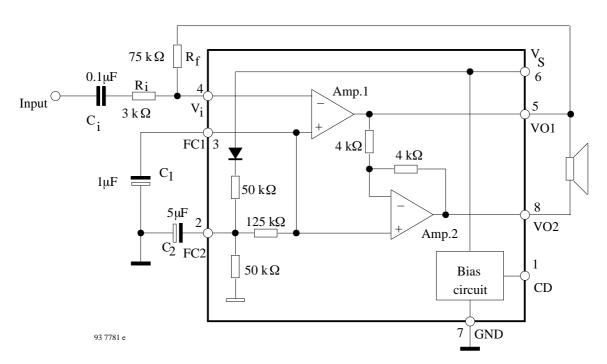

## **Block Diagram / Application Circuit**

Rev. A1: 22.07.1996

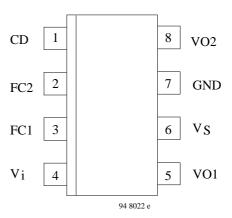

## **Pin Description**

| Pin | Symbol  | Function                          |

|-----|---------|-----------------------------------|

| 1   | CD      | Chip disable                      |

| 2   | FC2     | Filtering, power supply rejection |

| 3   | FC1     | Filtering, power supply rejection |

| 4   | Vi      | Amplifier input                   |

| 5   | VO1     | Amplifier output 1                |

| 6   | $V_{S}$ | Voltage supply                    |

| 7   | GND     | Ground                            |

| 8   | VO2     | Amplifier output 2                |

## Functional Description Including External Circuitry

#### Pin 1: Chip disable - digital input (CD)

Pin 1 (chip disable) is used to power down the IC to conserve power or muting or both.

Input impedance at pin 1 is typically 90 k $\Omega$ .

Logic 0 < 0.8 V IC enabled (normal

operation)

Logic 1 > 2 V IC disabled

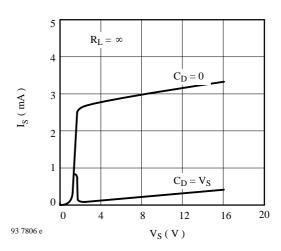

Figure 15 shows power supply current diagram. The change in differential gain from normal operation to muted operation (muting) is more than 70 dB.

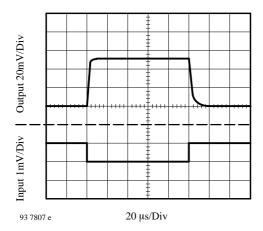

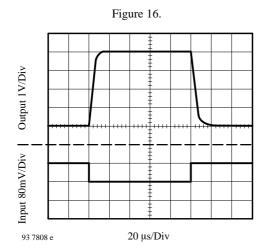

Switching characteristics are as follows:

turn-on time  $t_{on} = 12 \text{ to } 15 \text{ ms}$ turn-off time  $t_{off} \le 2 \text{ } \mu \text{s}$

They are independent of C<sub>1</sub>, C<sub>2</sub> and V<sub>S</sub>.

Voltages at Pins 2 and 3 are supplied from  $V_S$  and therefore do not change when the U4083B is disabled. Outputs— $V_{O1}$  (Pin 5) and  $V_{O2}$  (Pin 8) –turn to a high impedance condition by removing the signal from the speaker.

When signals are applied from an external source to the outputs (disabled), they must not exceed the range between the supply voltage,  $V_s$ , and Ground.

#### Pins 2 and 3: Filtering, power supply rejection

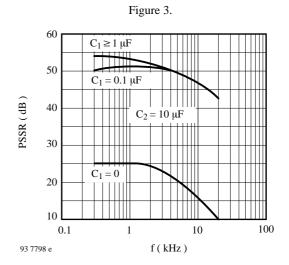

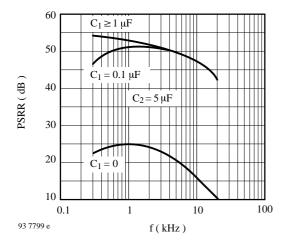

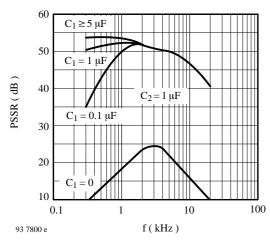

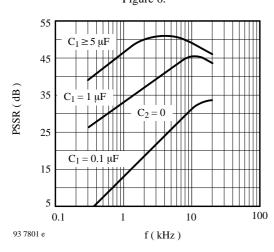

Power supply rejection is provided by capacitors  $C_1$  and  $C_2$  at Pin 3 and Pin 2, respectively.  $C_1$  is dominant at high frequencies whereas  $C_2$  is dominant at low frequencies (figures 4 to 7). Values of  $C_1$  and  $C_2$  depend on the conditions of each application. For example, a line powered speakerphone (telephone amplifier) will require more filtering than a system powered by regulated power supply.

The amount of rejection is a function of the capacitors and the equivalent impedance looking into Pin 3 and Pin 2 (see electrical characteristic equivalent resistance, R).

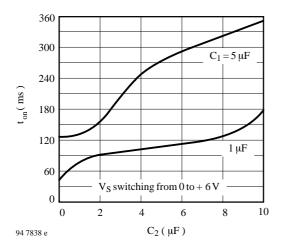

Apart from filtering, capacitors  $C_1$  and  $C_2$  also influence the turn-on time of the circuit at power-up since capacitors are charged up through the internal resistors (50 k $\Omega$  and 125 k $\Omega$ ) as shown in the block diagram.

Figure 1 shows turn-on time versus  $C_2$  at  $V_S = 6$  V, for two different  $C_1$  values.

Turn-on time is 60% longer when  $V_S = 3\ V$  and 20% shorter when  $V_S = 9\ V$ .

Turn-off time is less than 10 µs

$\begin{array}{ll} \mbox{Pin 4: Amplifier input} & V_i \\ \mbox{Pin 5: Amplifier output 1} & V_{O1} \\ \mbox{Pin 8: Amplifier output 2} & V_{O2} \end{array}$

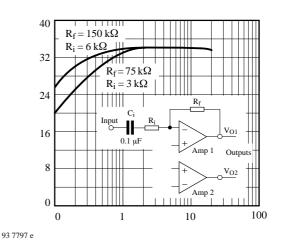

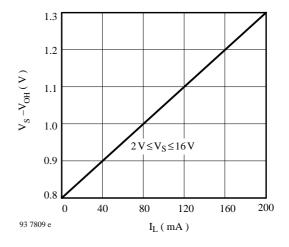

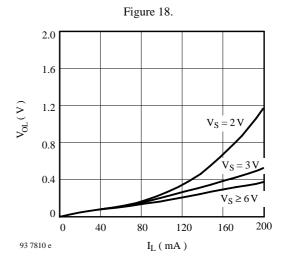

There are two identical operational amplifiers. Amp.1 has an open loop gain  $\geq 80$  dB at 100 Hz (figure 2), whereas the closed loop gain is set by external resistors, Rf and Ri (figure 3). The amplifier is unity gain stable, and has a unity gain frequency of approximately 1.5 MHz. A closed loop gain of 46 dB is recommended for a frequency range of 300 to 3400 Hz (voice band). Amp.2 is internally set to a gain of -1.0 (0 dB). The outputs of both amplifiers are capable of sourcing and sinking a peak current of 200 mA. Output voltage swing is between 0.4 V and  $V_s-1.3$  V at maximum current (figures 18 and 19).

The output dc offset voltage between Pins 5 and 8 ( $V_{O1}$  –  $V_{O2}$ ) is mainly a function of the feedback resistor,  $R_{\rm f}$ , because the input offset voltage of the two amplifiers generally neutralize each other.

Bias current of Amp. 1 which is constant with respect to  $V_s$ , however flows out of Pin 4 ( $V_i$ ) and through  $R_f$ , forcing  $V_{01}$  to shift negative by an amount equal to  $R_f \, I_{IB}$  and  $V_{O2}$  positive to an equal amount.

The output offset voltage specified in the electrical characteristics is measured with the feedback resistor ( $R_f = 75~k\Omega$ ) shown in typical application circuit. It takes into account bias current as well as internal offset voltages of the amplifiers.

#### **TELEFUNKEN Semiconductors**

#### Pin 6: Supply and power dissipation

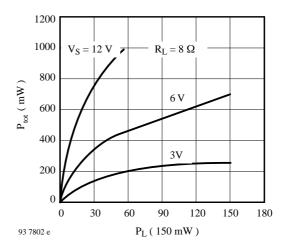

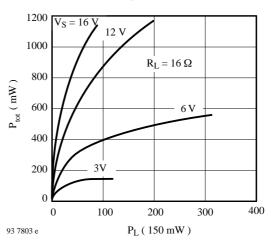

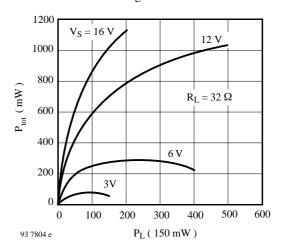

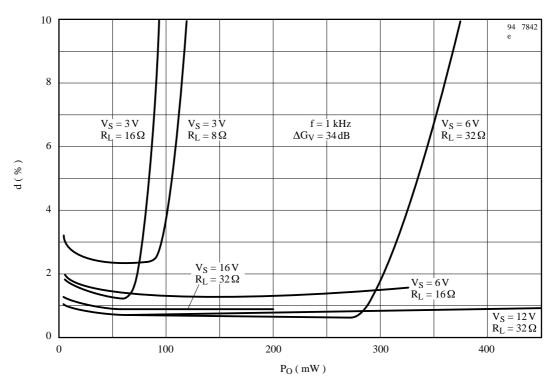

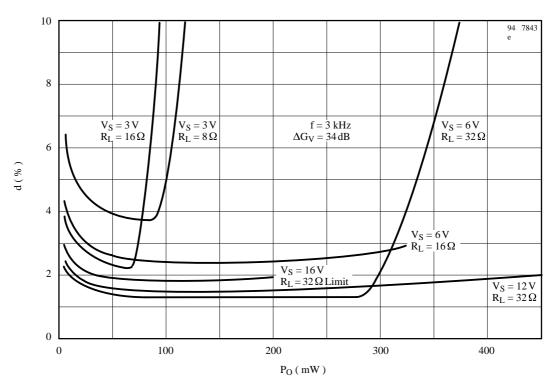

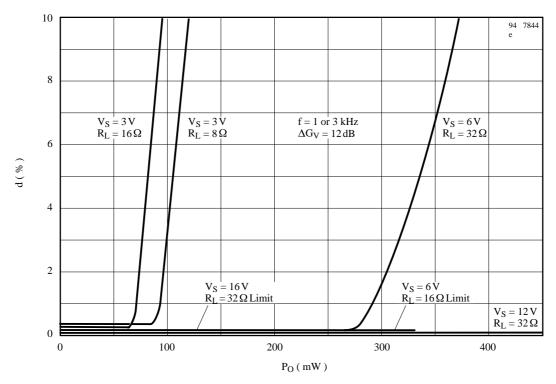

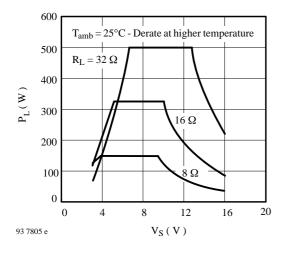

Power dissipation is shown in figures 8 to 10 for different loads. Distortion characteristics are given in figures 11 to 13

$$P_{totmax} = \frac{T_{jmax} - T_{amb}}{R_{thJA}}$$

where

$T_{imax}$  = Junction temperature = 140°C

$T_{amb} = Ambient temperature$

$R_{thJA}$  = Thermal resistance, junction-ambient

Power dissipated within the IC in a given application is found from the following equation:

$$P_{tot} = (V_S \cdot I_S) + (I_{RMS} \cdot V_S) - (R_L \cdot I_{RMS}^2)$$

I<sub>S</sub> is obtained from figures 15

I<sub>RMS</sub> is the RMS current at the load R<sub>L</sub>.

Operating range of the integrated circuit is defined with a peak operating load current of  $\pm 200$  mA (figures 8 to 13). It is further specified with respect to different loads in figure 14. The left (ascending) portion of each of the three curves is defined by the power level at which 10% distortion occurs. The center flat portion of each curve is defined by the maximum output current capability of the integrated circuit. The right (descending) portion of each curve is defined by the maximum internal power dissipation of the IC at 25°C. At higher ambient temperatures, the maximum load power must be reduced according to the above mentioned equation.

#### **Layout Considerations**

Normally a snubber is not needed at the output of the IC, unlike many other audio amplifiers. However, the PC board layout, stray capacitances, and the manner in which the speaker wires are configured, may dictate otherwise. Generally the speaker wires should be twisted tightly, and be not more than a few cm (or inches) in length.

## **Absolute Maximum Ratings**

Reference point Pin 7, T<sub>amb</sub> = 25°C unless otherwise specified.

| Parameters                                 |                                    | Symbol                               | Value                                  | Unit     |

|--------------------------------------------|------------------------------------|--------------------------------------|----------------------------------------|----------|

| Supply voltage                             | Pin 6                              | $V_{S}$                              | -1.0  to  +18                          | V        |

| Voltages<br>Disabled                       | Pins 1, 2, 3 and 4<br>Pins 5 and 8 |                                      | -1.0 to (VS +1.0)<br>-1.0 to (VS +1.0) | V<br>V   |

| Output current                             | Pins 5 and 8                       |                                      | ±250                                   | mA       |

| Junction temperature                       |                                    | $T_j$                                | +140                                   | °C       |

| Storage temperature range                  |                                    | T <sub>stg</sub>                     | -55 to +150                            | °C       |

| Ambient temperature range                  |                                    | T <sub>amb</sub>                     | -20 to +70                             | °C       |

| Power dissipation: $T_{amb} = 60^{\circ}C$ | SO 8<br>DIP8                       | P <sub>tot</sub><br>P <sub>tot</sub> | 440<br>720                             | mW<br>mW |

#### **Thermal Resistance**

| P                | arameters | Symbol     | Value | Unit |

|------------------|-----------|------------|-------|------|

| Junction ambient | SO 8      | $R_{thJA}$ | 180   | K/W  |

|                  | DIP 8     | $R_{thJA}$ | 110   | K/W  |

#### **Operation Recommendation**

| Parameters                            |             | Symbol            | Value      | Unit |

|---------------------------------------|-------------|-------------------|------------|------|

| Supply voltage                        | Pin 6       | $V_{S}$           | 2 to 16    | V    |

| Load impedance                        | Pins 5 to 8 | $R_{L}$           | 8.0 to 100 | Ω    |

| Load current                          |             | $I_{L}$           | ± 200      | mA   |

| Differential gain (5.0 kHz bandwidth) |             | ΔG                | 0 to 46    | dB   |

| Voltage @ CD Pin 1                    |             | $V_{\mathrm{CD}}$ | VS         | V    |

| Ambient temperature range             |             | T <sub>amb</sub>  | -20 to +70 | °C   |

Rev. A1: 22.07.1996

## **Electrical Characteristics**

$T_{amb}$  = +25°C, reference point Pin 7, unless otherwise specified

| Parameters                                                        | Test Conditions / Pins                                                                                                                                                                          | Symbol                                             | Min.             | Тур.                 | Max.              | Unit           |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|----------------------|-------------------|----------------|

| Amplifiers (AC Characteri                                         | stics)                                                                                                                                                                                          |                                                    |                  |                      |                   |                |

| Open gain loop<br>(Amp. 1, f < 100 Hz)                            |                                                                                                                                                                                                 | G <sub>VOL1</sub>                                  | 80               |                      |                   | dB             |

| Closed gain loop (Amp. 2)                                         | $V_S = 6.0 \text{ V}, \text{ f} = 1.0 \text{ kHz}, R_L = 32 \Omega$                                                                                                                             | G <sub>V2</sub>                                    | -0.35            | 0                    | +0.35             | dB             |

| Gain bandwidth product                                            |                                                                                                                                                                                                 | G <sub>BW</sub>                                    |                  | 1.5                  |                   | MHz            |

| Output power                                                      | $\begin{aligned} &V_S = 3.0 \text{ V},  R_L = 16  \Omega,  d < 10\% \\ &V_S = 6.0 \text{ V},  R_L = 32  \Omega,  d < 10\% \\ &V_S = 12  \text{ V},  R_L = 100  \Omega,  d < 10\% \end{aligned}$ | Po<br>Po<br>Po                                     | 55<br>250<br>400 |                      |                   | mW             |

| Total harmonic distortion (f = 1.0 kHz)                           | $V_S = 6.0 \text{ V}, R_L = 32 \Omega,$<br>$P_o = 125 \text{ mW}$<br>$V_S > 3.0 \text{ V}, R_L = 8 \Omega,$                                                                                     | d                                                  |                  | 0.5                  | 1.0               |                |

|                                                                   | $P_{o} = 20 \text{ mW}$<br>$V_{S} > 12 \text{ V}, R_{L} = 32 \Omega,$<br>$P_{o} = 200 \text{ mW}$                                                                                               | d<br>d                                             |                  | 0.5                  |                   | %              |

| Power supply rejection ratio                                      | $\begin{aligned} &V_S = 6.0 \text{ V}, \Delta V_S = 3.0 \text{ V} \\ &C_1 =        $                                                                                                            | PSRR<br>PSRR<br>PSRR                               | 50               | 12                   |                   | dB             |

| Muting                                                            | $V_S = 6.0 \text{ V}, 1.0 \text{ kHz} < f < 20 \text{ kHz},$<br>CD = 2.0  V                                                                                                                     | G <sub>MUTE</sub>                                  |                  | >70                  |                   | dB             |

| Amplifiers (DC Characteri                                         | stics)                                                                                                                                                                                          | nie i E                                            |                  |                      |                   |                |

| Output dc level at $V_{O1}$ , $V_{O2}$ $R_f = 75 \text{ kW}$      | $V_S = 3.0 \text{ V}, R_L = 16 \Omega$<br>$V_S = 6.0 \text{ V}$<br>$V_S = 12 \text{ V}$                                                                                                         | V <sub>O</sub><br>V <sub>O</sub><br>V <sub>O</sub> | 1.0              | 1.15<br>2.65<br>5.65 | 1.25              | V              |

| Output high level                                                 | $I_O = -75 \text{ mA},$<br>2.0 V < V <sub>S</sub> < 16 V                                                                                                                                        | V <sub>OH</sub>                                    |                  | $V_{S}-1$            |                   | V              |

| Output low level                                                  | $I_{O} = 75 \text{ mA},$<br>2.0 V < V <sub>S</sub> < 16 V                                                                                                                                       | V <sub>OL</sub>                                    |                  | 0.16                 |                   | V              |

| Output dc offset voltage $(V_{O1} - V_{O2})$                      | $\begin{aligned} V_S &= 6.0 \text{ V},  R_f = 75 \text{ k}\Omega, \\ R_L &= 32  \Omega \end{aligned}$                                                                                           | $\Delta V_{\mathrm{O}}$                            | -30              | 0                    | +30               | mV             |

| Input bias current at V <sub>i</sub>                              | $V_S = 6.0 \text{ V}$                                                                                                                                                                           | $-I_{IB}$                                          |                  | 100                  | 200               | nA             |

| Equivalent resistance at Pin 3                                    | $V_S = 6.0 \text{ V}$                                                                                                                                                                           | R                                                  | 100              | 150                  | 220               | kΩ             |

| Equivalent resistance at Pin 2                                    | $V_S = 6.0 \text{ V}$                                                                                                                                                                           | R                                                  | 18               | 25                   | 40                | kΩ             |

| Chip disable Pin 1<br>Input voltage — low<br>Input voltage — high |                                                                                                                                                                                                 | V <sub>IL</sub><br>V <sub>IH</sub>                 | 2.0              |                      | 0.8               | V<br>V         |

| Input resistance                                                  | $V_S = V_{CD} = 16 \text{ V}$                                                                                                                                                                   | R <sub>CD</sub>                                    | 50               | 90                   | 175               | kW             |

| Power supply current                                              | $V_S = 3.0 \text{ V}, R_L = \alpha, CD = 0.8 \text{ V}$<br>$V_S = 16 \text{ V}, R_L = \alpha, CD = 0.8 \text{ V}$<br>$V_S = 3.0 \text{ V}, R_L = \alpha, CD = 2.0 \text{ V}$                    | $egin{array}{c} I_{ m S} \ I_{ m S} \end{array}$   |                  | 65                   | 4.0<br>5.0<br>100 | mA<br>mA<br>μA |

# **TEMIC**

## **Typical Temperature Performance**

$T_{amb} = -20 \text{ to } +70^{\circ}\text{C}$

| Function                                                                                                                                                                                  | Typical Change  | Units            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|

| Input bias current at Vi                                                                                                                                                                  | ±40             | pA/°C            |

| Total harmonic distortion $V_S = 6.0 \text{ V}, R_L = 32 \Omega, P_o = 125 \text{ mW}, f = 1.0 \text{ kHz}$                                                                               | + 0.003         | %/ °C            |

| $\label{eq:power supply current} \begin{split} &Power \ supply \ current \\ &V_S = 3.0 \ V, \ R_L = \ ^\sim, \ CD = 0 \ V \\ &V_S = 3.0 \ V, \ R_L = \ ^\sim, \ CD = 2.0 \ V \end{split}$ | - 2.5<br>- 0.03 | μΑ/ °C<br>μΑ/ °C |

Figure 2. Figure 4.

Rev. A1: 22.07.1996 5 (11)

Figure 6.

Figure 9.

Figure 7.

Figure 10.

## **TELEFUNKEN Semiconductors**

Figure 11.

Figure 12.

Rev. A1: 22.07.1996 7 (11)

Figure 13.

Figure 14. Figure 15.

Figure 17. Figure 19.

Rev. A1: 22.07.1996 9 (11)

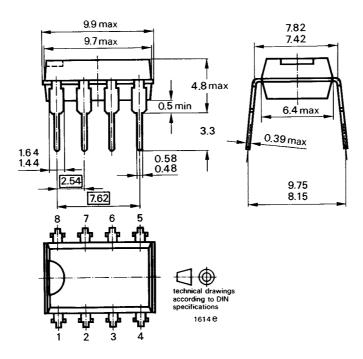

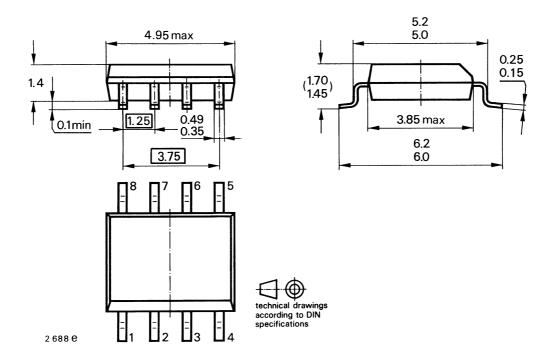

## **Dimensions in mm**

Package: DIP8

Package: SO8

#### **TELEFUNKEN Semiconductors**

#### **Ozone Depleting Substances Policy Statement**

It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423

Rev. A1: 22.07.1996