CMOS IC

# LC74401E, 74402, 74402E

# **PIP Controllers**

## **Overview**

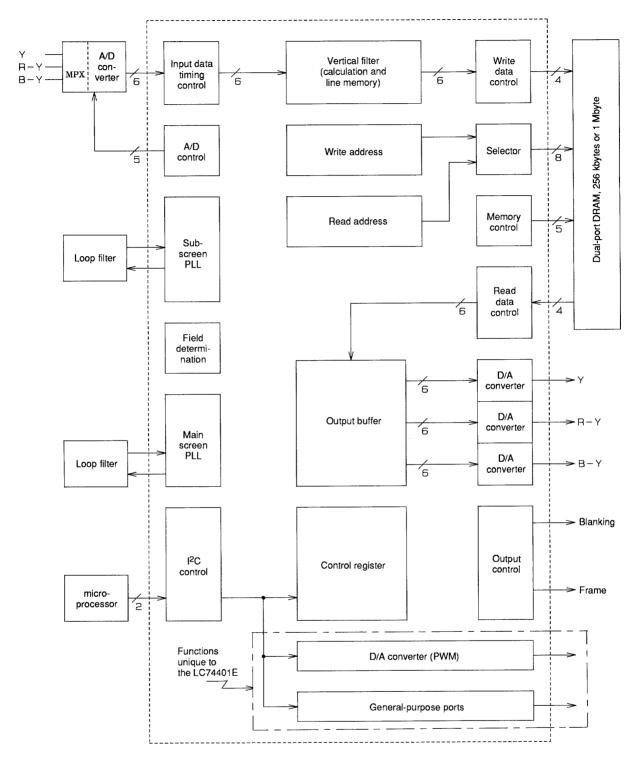

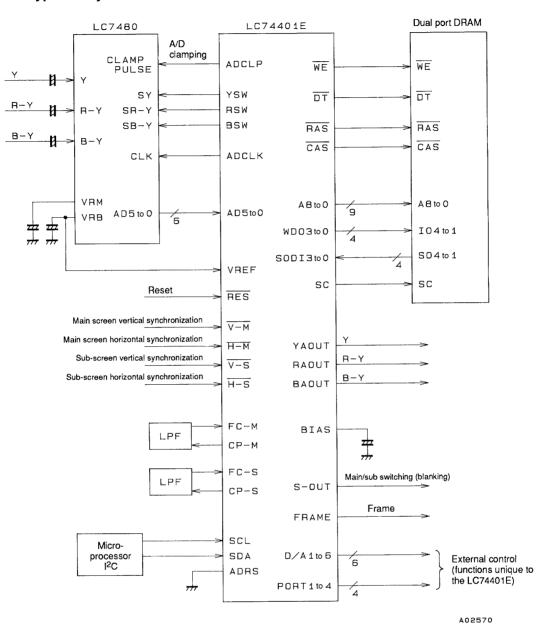

The LC74401E, LC74402, and LC74402E are memory controllers for TV set and VCR PIP (picture in picture) systems. Since these LSIs include three D/A converter circuits, a component PIP system can be constructed by combining one of these LSIs with memory and an A/D converter such as the LC7480.

## **Features**

- Horizontal resolution: 600 TV lines<sup>\*1</sup>

- Three D/A converters (for the Y, R-Y, and B-Y signals) are incorporated in the PIP memory controller block.

- High image quality is supported by vertical filter function frame memory processing<sup>\*2</sup>.

- I<sup>2</sup>C bus controlled.

- Built-in PLL circuit (requires an external LPF)

- Supports NTSC, PAL, and multiple (NTSC-PAL) formats

- External control functions (only provided by the LC74401E)

- 8-bit D/A converter (PWM): Six pins

- General-purpose ports: Four pins

- Sub-screen specifications

- Number of sub-screens:  $1-8^{*2}$

- Display on/off and frame on/off/color switching, wipe function

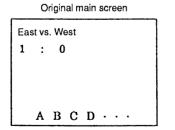

- Supports switching between fixed (4 corners) and arbitrary (8-bit specification of vertical and horizontal position) display positions.

- Size: Area: 1/4, 1/9, 1/16, Vertical compression: 1/2, 1/3, 1/4; Horizontal compression: 2/3, 1/3, 1/6

- Note: Horizontal compression can be adjusted by changing the PLL divisor.

The display area can be changed independently in the vertical and horizontal directions.

- Horizontal resolution (Y signal): About 250 dots

- Gradation (quantization): 64 (6 bits)

- Operating supply voltage: 5 V  $\pm$  10%

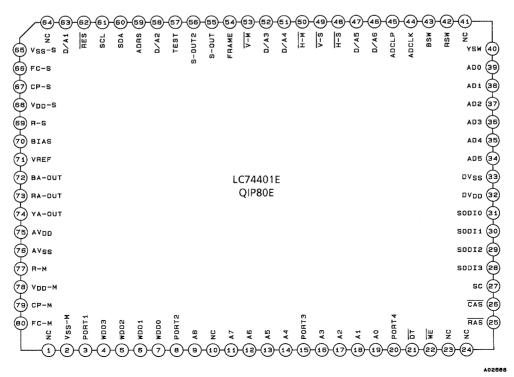

- QFP80E: LC74401E

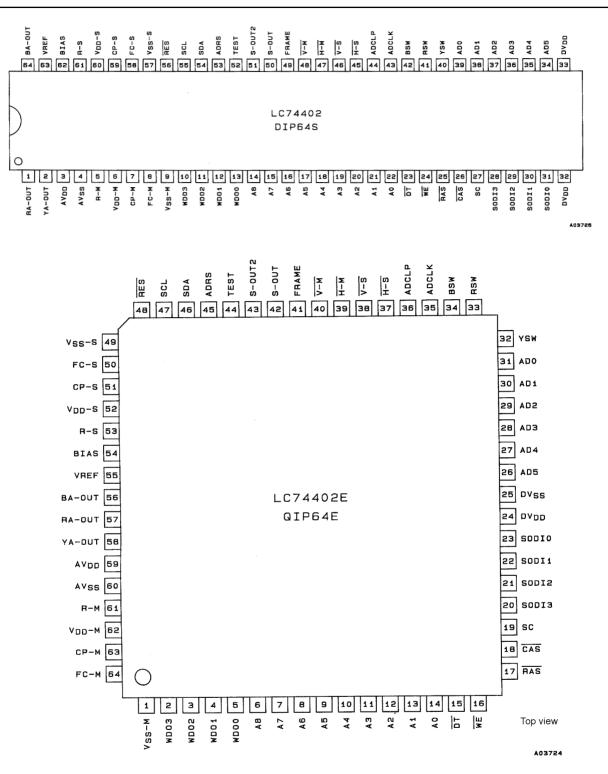

- DIP64S: LC74402-Pin assignment identical to the LC7442 (except for the serial control pins)

- QFP64E: LC74402E-Pin assignment identical to the LC7442E (except for the serial control pins) Note 1

|     | D/A Clock |  |  |

|-----|-----------|--|--|

| Y   | 15.00 MHz |  |  |

| R-Y | 3.75 MHz  |  |  |

| B-Y | 3.75 MHz  |  |  |

When the main screen synchronization PLL has the standard value (PLL7 to PLL3 = 10011)

| Note 2: | The specifications depend on the amount of    |

|---------|-----------------------------------------------|

|         | external memory as listed in the table below. |

| Display memory | 256 K | 1 M       |

|----------------|-------|-----------|

| One screen     |       | 0         |

| Two screens    | ×     | 0         |

| Three screens  | ×     | $\square$ |

| Four screens   | ×     | $\square$ |

O: Frame display of both dynamic and static images supported. (Frame memory processing)

∠: Frame display of dynamic images only supported.

X: Not supported.

Note: The number of sub-screens listed in the table above are doubled in split mode. (However, image quality is reduced.)

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

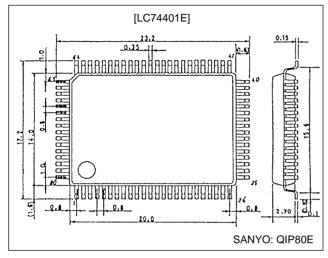

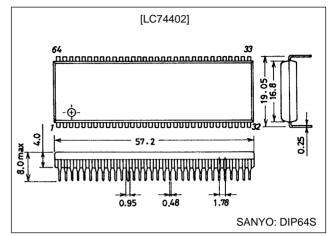

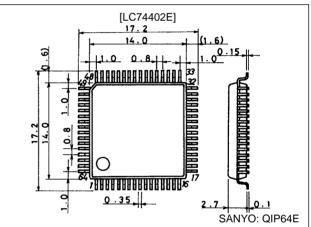

# **Package Dimensions**

unit: mm

#### 3074-QFP80E

unit: mm

#### 3071-DIP64S

## unit: mm

#### **Pin Assignments**

#### **Block Diagram**

A02569

#### Component-Type PIP System Structure Based on the LC74401E/2/2E and the LC7480

No. 4872-5/19

## **Functional Overview**

1. Reduction options

Vertical: Selectable 1/2, 1/3 and 1/4 reduction vertical filter coefficients. Horizontal: (1/1) to 2/3 to (1/2) to 1/3 to (1/4) to 1/6. Intermediate values are implemented using the aspect correction function.

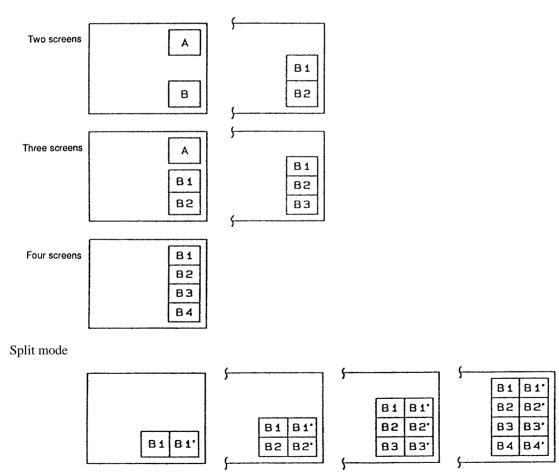

2. Number of sub-screens

With 1 Mb of memory: 1 to 4 or (8). \* Values in parentheses are for SPLIT mode, where the image quality is reduced.

With 256 kb of memory: 1 or (2).

3. Static images

With 1 Mb of memory: Frame static image (supported with 2 or fewer screens) or field static images With 256 kb of memory: Field static image

4. Display position

Screen A: Fixed positions in the four corners Screen B: Free positioning (Specified by 8 bits in each of the vertical and horizontal directions.)

- 5. Frame

- On/off selectable

- Two types that differ by insertion method

- Pin frame: The frame position is specified by a high level pin output. (application frame insertion)

- D/A frame: A 50% white or arbitrary color overlapped on the Y, R-Y, and B-Y video signals.

- 6. Wipe

Twelve types

7. Blanking size

The vertical and horizontal directions can be specified independently (6 bits each) Sixteen forms can be specified.

- 8. Blue background The sub-screen can be set to all blue or all black.

- 9. Memory clear

Sets the data written to video memory to a fixed value corresponding to a 25% white color.

- 10. Wide-screen TV support

- Aspect correction function

- Subtitle shifting

The subtitle area can be trimmed and displayed as a sub-screen.

The vertical reduction ratio can be set independently to 1/4, 1/3, or 1/2. The horizontal reduction can be set to values up to 1/1 using mode 2E.

- 11. Support for NTSC, PAL, and multi-mode (NTSC-PAL) products

- 12. External control functions using an I<sup>2</sup>C interface (LC74401E only)

- Six 8-bit D/A converter circuits built-in (PWM)

- Four general-purpose ports built-in

- 13. Setting adjustments

Fine adjustment of various settings, including sub-screen position displacement and color shift is supported.

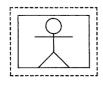

## Sub-screen Size

The vertical and horizontal directions are controlled independently.

- 1. Vertical size

- 1/3 to (3) scan lines are compressed to a single scan line

- 1/4 to (4) scan lines are compressed to a single scan line

- 2. Horizontal size

- 1/3 to A/D clock: D/A clock = 1:3

- 1/6 to A/D clock: D/A clock = 1:6

- The data required for 1/6 reduction is one half that for 1/3 reduction.

- Aspect correction function

The horizontal direction size is adjusted by changing the VCO oscillator frequency (system clock). This can be adjusted from -30% to +30%.

However, care is required when using this function. See the Application Manual for details.

• 2E mode

If 2E mode is used when 1/3 size is selected, the horizontal direction is expanded by a factor of two. This is normally used only for special functions such as split mode.

#### Number of Sub-screens

Between one and eight sub-screens can be specified (when 1 Mb of VRAM is used).

Refer to the Application Manual for details on using these modes.

A08571

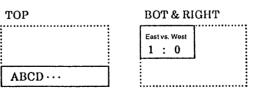

## Wipe Function

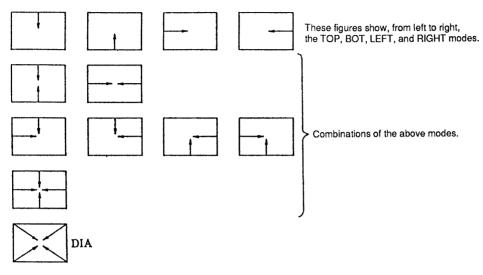

Wipe operation can be set in the top, bottom, left, and right directions, and in the diagonal direction independently.

A02572

After a wipe mode has been set up, it operates automatically each time a sub-screen is switched on or off.

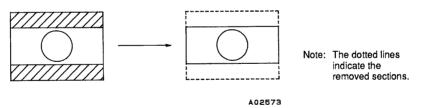

#### **Display Area Function**

This function controls the blanking area.

The vertical direction and horizontal direction can be set up independently.

The operating mode is set by setting the wipe function TOP, BOT, LEFT, or RIGHT mode.

#### **Application Example**

1. Excluding the masked portion of the letter box screen

2. Subtitle display

#### 3. Small display

Reduces the portion of the main screen that is hidden.

Example: 70% display

#### Multi-mode

- 1. When 1 Mb of VRAM is used

- Frame memory processing (FRM = high)

Dynamic images: Frame display (MUL = high, overrun phenomenon occurs)

Static images: Frame display

- Field memory processing (FRM = low, FILD = high) Dynamic images: Field display (overrun phenomenon occurs) Static images: Field display

NTSC/PAL (= main/sub)

The sub-screen size ratio (V) will be:

$a:b:c:d{:}=1:0.8:0.77:0.58$

If b and c are used, the size change can be held to 5%.

When 256 kb of VRAM are used Field memory processing (FRM = low, FILD = high) Dynamic images: Field display (overrun phenomenon occurs) Static images: Field display Only one screen can be displayed.

# **Control Register Table**

| Address<br>(HEX) | MSB<br>7 | 6       | 5      | 4      | 3      | 2      | 1      | LSB<br>0 |                                |

|------------------|----------|---------|--------|--------|--------|--------|--------|----------|--------------------------------|

| 01               | SBY      | STL     | NT/PAL | MUL    | FILD   | FRM    | P-NUM1 | P-NUM0   | Operating mode 1               |

| 02               | WRT2     | WRT1    | WRT0   | D-FIX  | POUT-B | POUT-A | FVP    | FHP      | Operating mode 2               |

| 03               | VP7      | VP6     | VP5    | VP4    | VP3    | VP2    | VP1    | VP0      | Screen B display position (V)  |

| 04               | HP7      | HP6     | HP5    | HP4    | HP3    | HP2    | HP1    | HP0      | Screen B display position (H)  |

| 05               | FRM-B    | FRM-A   | FRC-B  | FRC-A  | YFC5   | YFC4   | YFC3   | YFC2     | Frame setting, frame color (Y) |

| 06               | RFC5     | RFC4    | RFC3   | RFC2   | BFC5   | BFC4   | BFC3   | BFC2     | Frame color (R-Y, B-Y)         |

| 07               | VDF-CO   | HDF. 2E | CL-AJ1 | CL-AJ0 | FM-AJ1 | FM-AJ0 | YC-AJ1 | YC-AJ0   | Filter setting, adjustment 1   |

| 08               | SIZE-V   | SIZE-H  | SPLIT  | PLL7   | PLL6   | PLL5   | PLL4   | PLL3     | Sub-screen size, PLL           |

| 09               | WPE-B    | WPE-A   | TOP    | BOT    | LEFT   | RIGHT  | DIA    | WP-MOD   | Wipe setting                   |

| 0A               | PHP-M    | PHP-S   | VBS5   | VBS4   | VBS3   | VBS2   | VBS1   | VBS0     | Display area (V)               |

| 0B               | DT-AJ1   | DT-AJ0  | HBS5   | HBS4   | HBS3   | HBS2   | HBS1   | HBS0     | Display area (H)               |

| 0C               | TEXT     | UPPER   | M-BLUE | M-LVL  | YL5    | YL4    | YL3    | YL2      | Subtitle display setting       |

| 0D               | WV-AJ1   | WV-AJ0  | WH-AJ1 | WH-AJ0 | VP-AJ1 | VP-AJ0 | HP-AJ1 | HP-AJ0   | Display adjustment 2           |

| 0E               | DAC1-7   | DAC1-6  | DAC1-5 | DAC1-4 | DAC1-3 | DAC1-2 | DAC1-1 | DAC1-0   | 8-bit D/A converter 1 data     |

| 0F               | DAC2-7   | DAC2-6  | DAC2-5 | DAC2-4 | DAC2-3 | DAC2-2 | DAC2-1 | DAC2-0   | 8-bit D/A converter 2 data     |

| 10               | DAC3-7   | DAC3-6  | DAC3-5 | DAC3-4 | DAC3-3 | DAC3-2 | DAC3-1 | DAC3-0   | 8-bit D/A converter 3 data     |

| 11               | DAC4-7   | DAC4-6  | DAC4-5 | DAC4-4 | DAC4-3 | DAC4-2 | DAC4-1 | DAC4-0   | 8-bit D/A converter 4 data     |

| 12               | DAC5-7   | DAC5-6  | DAC5-5 | DAC5-4 | DAC5-3 | DAC5-2 | DAC5-1 | DAC5-0   | 8-bit D/A converter 5 data     |

| 13               | DAC6-7   | DAC6-6  | DAC6-5 | DAC6-4 | DAC6-3 | DAC6-2 | DAC6-1 | DAC6-0   | 8-bit D/A converter 6 data     |

| 14               | 0        | 0       | 0      | 0      | PORT-4 | PORT-3 | PORT-2 | PORT-1   | General-purpose port           |

| 15               | V-1/2    | 0       | 0      | 0      | 0      | 0      | 0      | 0        | Test data                      |

Note:

1. "0" indicates that the register value is set to 0.

2. When designing an application, be sure to read the Application Manual and check any relevant notes.

3. Addresses 0E to 14 are only valid for the LC74401E.

# **Register Data Overview**

| Address | Symbol      | Description                                                                           |

|---------|-------------|---------------------------------------------------------------------------------------|

|         | SBY         | Standby mode (PLL circuit operating)                                                  |

|         | STL         | Static image (All writing stopped)                                                    |

| 01      | NT/PAL      | Format selection (high: NTSC, low: PAL)                                               |

|         | MUL         | Multi-mode                                                                            |

|         | FILD        | Field display selection                                                               |

|         | FRM         | Frame memory processing selection                                                     |

| -       | P-NUM1, 0   | Number of screen B screens displayed (one to four screens)                            |

|         | WRT2 to 0   | Dynamic image setting (write screen specification)                                    |

|         | D-FIX       | Memory clear (fixes the memory write data)                                            |

| 02      | POUT-B, A   | Sub-screen display on/off                                                             |

|         | FVP, FHP    | Four corner fixed position (screen A) specification                                   |

| 03      | VP7 to 0    | Screen B vertical position data                                                       |

| 04      | HP7 to 0    | Screen B horizontal position data                                                     |

| -       | FRM-B, A    | D/A converter frame on/off                                                            |

| 05      | FRC-B, A    | D/A converter frame color register value specification                                |

|         | YFC5 to 2   | D/A converter frame color (Y)                                                         |

|         | RFC5 to 2   | D/A converter frame color (R-Y)                                                       |

| 06      | BFC5 to 2   | D/A converter frame color (B-Y)                                                       |

|         | VDF-CO      | Vertical filter coefficient specification                                             |

| -       |             | HDF (horizontal filter on/off when SIZE-H = 1)                                        |

|         | HDF, 2E     | 2E mode (horizontal 2x expansion) on/off when SIZE-H = 0                              |

| 07      | CL-AJ1, 0   | A/D converter clamping position adjustment                                            |

| F       |             |                                                                                       |

| F       | FM-AJ1, 0   | D/A converter frame left/right thickness adjustment                                   |

|         | YC-AJ1, 0   | Position adjustment for C (R-Y, B-Y) with respect to Y                                |

| -       | SIZE-V      | Vertical reduction specification H: 1/4 L: 1/3                                        |

| 08      | SIZE-H      | Horizontal reduction specification H: 1/6 L: 1/3                                      |

| _       | SPLIT       | Split mode (Doubles the number of screens by splitting the sub-screens horizontally.) |

|         | PLL7 to 3   | PLL divisor value (10011 is the standard value)                                       |

| -       | WPE-B, A    | Wipe or display area function enable                                                  |

| 09      | TOP to DIA  | Wipe or display area function shape specification                                     |

|         | WP-MOD      | Wipe or display area function selection (high: wipe)                                  |

| 0A      | PHP-M, S    | Inversion or non-inversion of the field determination result                          |

|         | VBS5 to 0   | Display area value setting (vertical direction)                                       |

| 0В -    | DT-AJ1, 0   | Memory control signal (DT) adjustment                                                 |

| -       | HBS5 to 0   | Display area value setting (horizontal direction)                                     |

|         | TEXT        | Partial display of an image reduced 1/2 in the vertical direction                     |

|         | UPPER       | Section specification for partial display in TEXT mode                                |

| 0C      | M-BLUE      | Blue specification in masking mode                                                    |

|         | M-LVL       | Y level specification for the masked section                                          |

|         | YL-5 to 2   | Masking level (data compared to the Y level)                                          |

|         | WV-AJ1, 0   | Write vertical direction adjustment                                                   |

| 0D -    | WH-AJ1, 0   | Write horizontal direction adjustment                                                 |

| 00      | VP-AJ1, 0   | Display position vertical direction adjustment                                        |

|         | HP-AJ1, 0   | Display position horizontal direction adjustment                                      |

| 0E      | DAC1-7 to 0 |                                                                                       |

| 0F      | DAC2-7 to 0 |                                                                                       |

| 10      | DAC3-7 to 0 | Evidence I control D/A converter (A bit DIAMA) dot-                                   |

| 11      | DAC4-7 to 0 | External control D/A converter (8-bit PWM) data                                       |

| 12      | DAC5-7 to 0 |                                                                                       |

| 13      | DAC6-7 to 0 |                                                                                       |

| 14      | PORT-4 to 1 | General-purpose port data                                                             |

| 15      | V-1/2       | Vertical reduction specification 1/2                                                  |

Note: The register functions at register addresses 0E to 14 can only be used with the LC74401E.

## **Pin Functions**

Pin No. 80E: LC74401E, 64S: LC74402, 64E: LC74402E

|     | Pin No.  |     |        |      |                        |                        | <b>–</b>                                        |              |

|-----|----------|-----|--------|------|------------------------|------------------------|-------------------------------------------------|--------------|

| 64S | 64E      | 80E | Symbol | I/O  | Connection             |                        | Functions                                       | Circuit type |

| 48  | 40       | 53  | V-M    | I    |                        | Main scre<br>(negative | een vertical synchronization signal polarity)   |              |

| 47  | 39       | 50  | H-M    | I    | LA7403 or a sync       | Main scre<br>(negative | een horizontal synchronization signal polarity) |              |

| 46  | 38       | 49  | V-S    | I    | separator IC           | Sub-scre<br>(negative  | en vertical synchronization signal polarity)    |              |

| 45  | 37       | 48  | H-S    | I    |                        | Sub-scre<br>(negative  | en horizontal synchronization signal polarity)  |              |

| 55  | 47       | 61  | SCL    | I    | Microprocessor         | Serial clo             | ck l <sup>2</sup> C                             |              |

| 54  | 46       | 60  | SDA    | I/O  | Microprocessor         | Serial da              | ta                                              | 400570       |

| 53  | 45       | 59  | ADRS   | I    | V <sub>SS</sub>        |                        |                                                 | A02576       |

| 56  | 48       | 62  | RES    | I    | Initialization circuit | Reset                  |                                                 |              |

| 52  | 44       | 57  | TEST   | I    | V <sub>SS</sub>        | Test (Tie              | d to $V_{SS}$ in normal operation.)             | A02577       |

| _   |          | 3   | PORT1  | 0    |                        |                        |                                                 |              |

| _   |          | 8   | PORT2  | 0    |                        | General                | ourpose ports                                   |              |

|     | —        | 15  | PORT3  | 0    |                        | General                | bulpose ports                                   |              |

|     | —        | 20  | PORT4  | 0    |                        |                        |                                                 |              |

| 10  | 2        | 4   | WDO3   | 0    |                        |                        |                                                 |              |

| 11  | 3        | 5   | WDO2   | 0    | Memory                 | Memory                 | write data outputs                              |              |

| 12  | 4        | 6   | WDO1   | 0    |                        |                        |                                                 |              |

| 13  | 5        | 7   | WDO0   | 0    |                        |                        |                                                 |              |

| 14  | 6        | 9   | A8     | 0    |                        | MSB                    |                                                 |              |

| 15  | 7        | 11  | A7     | 0    | _                      |                        |                                                 |              |

| 16  | 8        | 12  | A6     | 0    | _                      |                        |                                                 |              |

| 17  | 9        | 13  | A5     | 0    | _                      |                        | Address                                         |              |

| 18  | 10       | 14  | A4     | 0    | Memory                 |                        | (A8 is left open when<br>a 256 kbyte external   |              |

| 19  | 11       | 16  | A3     | 0    | _                      |                        | memory is used.)                                |              |

| 20  | 12       | 17  | A2     | 0    | _                      |                        |                                                 |              |

| 21  | 13       | 18  | A1     | 0    | _                      |                        |                                                 |              |

| 22  | 14       | 19  | A0     | 0    |                        | LSB                    |                                                 |              |

| 23  | 15       | 21  | DT     | 0    | -                      |                        |                                                 |              |

| 24  | 16       | 22  | WE     | 0    | -                      |                        |                                                 |              |

| 25  | 17       | 25  | RAS    | 0    | Memory                 | Control s              | ignals                                          |              |

| 26  | 18       | 26  | CAS    | 0    | -                      |                        |                                                 | A02578       |

| 27  | 19       | 27  | SC     | 0    |                        |                        |                                                 |              |

| 28  | 20       | 28  | SODI3  | <br> | -                      |                        |                                                 |              |

| 29  | 21       | 29  | SODI2  | 1    | Memory                 | Memory                 | read data inputs                                |              |

| 30  | 22       | 30  | SODI1  | 1    | + -                    |                        |                                                 | TTL level    |

| 31  | 23       | 31  | SODIO  |      |                        |                        |                                                 | A02579       |

|     | <u> </u> | 63  | D/A1   | 0    | +                      |                        |                                                 |              |

|     | <u> </u> | 58  | D/A2   | 0    | +                      |                        |                                                 |              |

|     |          | 52  | D/A3   | 0    | +                      | PWM D/                 | A converter output                              |              |

|     |          | 51  | D/A4   | 0    | +                      |                        |                                                 | h            |

|     | <u> </u> | 47  | D/A5   | 0    | +                      |                        |                                                 | A02580       |

| —   | -        | 46  | D/A6   | 0    |                        |                        |                                                 |              |

## LC74401E, 74402, 74402E

Continued from preceding page.

Pin No. 80E: LC74401E, 64S: LC74402, 64E: LC74402E

|     | Pin No. |     |                    |     |            |                          | Functions                                       |                          | 0'     |

|-----|---------|-----|--------------------|-----|------------|--------------------------|-------------------------------------------------|--------------------------|--------|

| 64S | 64E     | 80E | Symbol             | I/O | Connection |                          | Func                                            | Circuit type             |        |

| 34  | 26      | 34  | AD5                | I   |            | MSB                      |                                                 |                          |        |

| 35  | 27      | 35  | AD4                | I   |            |                          |                                                 |                          |        |

| 36  | 28      | 36  | AD3                | I   | 1.07400    |                          | La monta fam A //                               |                          |        |

| 37  | 29      | 37  | AD2                | I   | LC7480     |                          | Inputs for A/L                                  | D converted digital data |        |

| 38  | 30      | 38  | AD1                | I   |            |                          |                                                 |                          | A02577 |

| 39  | 31      | 39  | AD0                | I   |            | LSB                      |                                                 |                          |        |

| 40  | 32      | 40  | YSW                | 0   |            | Y signal s               | election                                        |                          |        |

| 41  | 33      | 42  | RSW                | 0   | LC7480     | R-Y signa                | l selection                                     | MPX switching signals    |        |

| 42  | 34      | 43  | BSW                | 0   |            | B-Y signa                | l selection                                     |                          |        |

| 43  | 35      | 44  | ADCLK              | 0   | LC7480     | Sampling                 | clock                                           |                          |        |

| 44  | 36      | 45  | ADCLP              | 0   | LC7480     | Clamping                 | pulse                                           |                          |        |

| 49  | 41      | 54  | FRAME              | 0   | LA7403     | Frame pu                 | lse output                                      |                          |        |

| 50  | 42      | 55  | S-OUT              | 0   | LA7403     | Main/sub                 | switching sig                                   | nal                      |        |

| 51  | 43      | 56  | S-OUT2             | 0   | _          | Control si               | Control signal                                  |                          | A02578 |

| 32  | 24      | 32  | DV <sub>DD</sub>   |     |            | Digital po               | wer supply                                      |                          |        |

| 33  | 25      | 33  | DV <sub>SS</sub>   |     |            | (for logic of            | (for logic circuits and line memory)            |                          |        |

| 2   | 58      | 74  | YA-OUT             | 0   |            | Y signal                 | r signal                                        |                          |        |

| 1   | 57      | 73  | RA-OUT             | 0   | LA7403     | R-Y signa                | I D/A cor                                       | nverter outputs          |        |

| 64  | 56      | 72  | BA-OUT             | 0   | -          | B-Y signa                | 1                                               |                          |        |

| 63  | 55      | 71  | VREF               | I   | LC7480     |                          |                                                 | waters eattings          |        |

| 62  | 54      | 70  | BIAS               | —   | Capacitor  | D/A conve                | enter analog s                                  | system settings          |        |

| 3   | 59      | 75  | AV <sub>DD</sub>   |     |            |                          | rtor opolog o                                   | waters new ar europhy    |        |

| 4   | 60      | 76  | AV <sub>SS</sub>   |     | -          | D/A CONVE                | enter analog s                                  | system power supply      |        |

| 7   | 63      | 79  | CP-M               | 0   | LPF        | Charge p                 | ump output                                      |                          |        |

| 8   | 64      | 80  | FC-M               | I   | LPF        | Oscillator<br>voltage in |                                                 | Main screen              |        |

| 5   | 61      | 77  | R-M                | _   | Resistor   | Oscillator               | range resisto                                   | or synchronization       |        |

| 6   | 62      | 78  | V <sub>DD</sub> -M |     |            | D                        |                                                 | VCO                      |        |

| 9   | 1       | 2   | V <sub>SS</sub> -M |     |            | Power su                 | рріу                                            |                          |        |

| 59  | 51      | 67  | CP-S               | 0   | LPF        | Charge p                 | ump output                                      |                          |        |

| 58  | 50      | 66  | FC-S               | I   | LPF        |                          | Oscillator control<br>voltage input Main screen |                          |        |

| 61  | 53      | 69  | R-S                | -   | Resistor   | Oscillator               | range resisto                                   | or synchronization       |        |

| 60  | 52      | 68  | V <sub>DD</sub> -S |     |            | Dowor ou                 | oply                                            | - vco                    |        |

| 57  | 49      | 65  | V <sub>SS</sub> -S |     | ]          | Power su                 | рру                                             |                          |        |

# Specifications

# Absolute Maximum Ratings at Ta = $25 \pm 8^{\circ}$ C, V<sub>SS</sub> = 0 V

| Parameter                   | Symbol              | Conditions | Ratings                       | Unit |

|-----------------------------|---------------------|------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |            | -0.3 to +7.0                  | V    |

| Input voltage               | V <sub>IN</sub>     |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage              | V <sub>OUT</sub>    |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max              |            | 350                           | mW   |

| Operating temperature       | Topr                |            | -10 to +70                    | °C   |

| Storage temperature         | Tstg                |            | -55 to +125                   | °C   |

| Parameter                | Symbol            | Conditions | Ratings             |                     |                     | Unit |

|--------------------------|-------------------|------------|---------------------|---------------------|---------------------|------|

| Falanleter               | Symbol            | min        | typ                 | max                 | Offic               |      |

| Supply voltage           | V <sub>DD</sub>   |            | 4.5                 | 5.0                 | 5.5                 | V    |

| Input high level voltage | V <sub>IH</sub> 1 | CMOS level | 0.7 V <sub>DD</sub> |                     |                     | V    |

| input high level voltage | V <sub>IH</sub> 2 | TTL level  | 2.2                 |                     |                     | V    |

| Input low level voltage  | V <sub>IL</sub> 1 | CMOS level |                     |                     | 0.3 V <sub>DD</sub> | V    |

| input low level voltage  | V <sub>IL</sub> 2 | TTL level  |                     |                     | 0.8                 | V    |

| Reference voltage        | V <sub>REF</sub>  |            | 3.4                 | 0.8 V <sub>DD</sub> | V <sub>DD</sub>     | V    |

# Allowable Operating Ranges at Ta = -10 to $+70^{\circ}$ C, V<sub>SS</sub> = 0 V

# Electrical Characteristics at Ta = 25 $\pm$ 2°C, V\_{DD} = 5 V $\pm$ 10%, V\_{SS} = 0 V

| Parameter                             | Quarter           | Symbol Conditions                                                             |                     | Ratings |     |      |  |

|---------------------------------------|-------------------|-------------------------------------------------------------------------------|---------------------|---------|-----|------|--|

| Parameter                             | Symbol            | Conditions                                                                    | min                 | typ max |     | Unit |  |

| Output high level voltage             | V <sub>OH</sub> 1 | Pins CP-M and CP-S: $I_{OH} = -1 \text{ mA}$                                  | V <sub>DD</sub> – 1 |         |     | V    |  |

| Output high level voltage             | V <sub>OH</sub> 2 | Pins other than CP-M and CP-S: $I_{OH} = -1 \text{ mA}$                       | V <sub>DD</sub> – 1 |         |     | V    |  |

|                                       | V <sub>OL</sub> 1 | Pins CP-M and CP-S: I <sub>OL</sub> = 1 mA                                    |                     |         | 1.0 | V    |  |

| Output low level voltage              | V <sub>OL</sub> 2 | Pins other than CP-M and CP-S: I <sub>OL</sub> = 2 mA                         |                     |         | 0.4 | V    |  |

|                                       | V <sub>OL</sub> 3 | With the SDA pin output active: I <sub>OL</sub> = 3 mA                        |                     |         | 0.4 | V    |  |

|                                       | I <sub>DD</sub> D | The DV <sub>SS</sub> pin                                                      |                     | 25      |     | mA   |  |

| Operating oursent drain*1             | I <sub>DD</sub> A | The AV <sub>SS</sub> pin                                                      |                     | 21      |     | mA   |  |

| Operating current drain <sup>*1</sup> | I <sub>DD</sub> M | The V <sub>SS</sub> -M pin                                                    |                     | 2       |     | mA   |  |

|                                       | I <sub>DD</sub> S | The V <sub>SS</sub> -S pin                                                    |                     | 2       |     | mA   |  |

| Quiescent current                     | I <sub>DD</sub> S | RES: V <sub>SS</sub><br>with DC signals on the input pins and no output load. |                     |         | 10  | μA   |  |

| Input leakage current                 | I <sub>LK</sub>   | $V_{I} = V_{DD}, V_{SS}$                                                      | -1                  |         | +1  | μA   |  |

| Output leakage current                | I <sub>OZ</sub>   | Pins CP-M and CP-S; $V_I = V_{DD}$ , $V_{SS}$                                 | -1                  |         | +1  | μA   |  |

| D/A converter output resistance       | R <sub>DA</sub>   |                                                                               |                     | 150     |     | Ω    |  |

Note: 1. Test conditions as follows: RES: V<sub>DD</sub>, V-M, V-S: 60 Hz, H-M, H-S: 15 kHz A/D converter data: 1010..., No output load 2. There are four power supply pin systems. The supply voltages must all be equal, i.e., DV<sub>DD</sub> = AV<sub>DD</sub> = V<sub>DD</sub>-M = V<sub>DD</sub>-S. Descriptions are in terms of V<sub>DD</sub>. The grounds must all be equal, i.e., DV<sub>SS</sub> = AV<sub>SS</sub> = V<sub>SS</sub>-M = V<sub>SS</sub>-S. Descriptions are in terms of V<sub>SS</sub>.

# Switching Characteristics at Ta = 25 $\pm$ 2°C, V\_{DD} = 5 V $\pm$ 10%, V\_{SS} = 0 V

| Parameter                         | Symbol Conditions     |            | Unit |     |      |     |

|-----------------------------------|-----------------------|------------|------|-----|------|-----|

| Parameter                         | Symbol                | Conditions | min  | typ | max  |     |

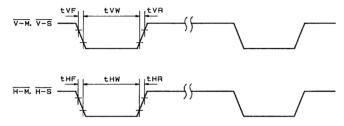

| Vertical synchronization signal   |                       |            |      |     |      |     |

| Pulse width                       | t <sub>VW</sub>       |            | 1    |     |      | μs  |

| Rise time                         | t <sub>VR</sub>       |            |      |     | 50   | ns  |

| Fall time                         | t <sub>VF</sub>       |            |      |     | 50   | ns  |

| Horizontal synchronization signal |                       |            |      |     |      |     |

| Pulse width                       | t <sub>HW</sub>       |            | 1    |     |      | μs  |

| Rise time                         | t <sub>HR</sub>       |            |      |     | 50   | ns  |

| Fall time                         | t <sub>HF</sub>       |            |      |     | 50   | ns  |

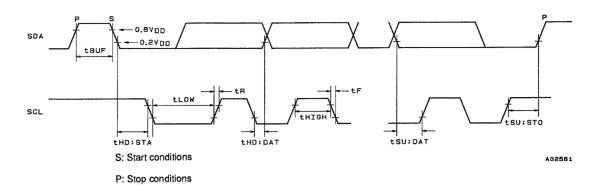

| I <sup>2</sup> C timing           |                       |            |      |     |      |     |

| SCL frequency                     | t <sub>SCL</sub>      |            |      |     | 100  | kHz |

| Bus release time                  | t <sub>BUF</sub>      |            | 4.7  |     |      | μs  |

| Start hold time                   | t <sub>HD</sub> ; STA |            | 4.0  |     |      | μs  |

| SCL low period                    | t <sub>LOW</sub>      |            | 4.7  |     |      | μs  |

| SCL high period                   | tHIGH                 |            | 4.0  |     |      | μs  |

| Data hold time                    | t <sub>HD</sub> ; DAT |            | 0    |     |      | μs  |

| Data setup time                   | t <sub>SU</sub> ; DAT |            | 250  |     |      | ns  |

| Rise time                         | t <sub>R</sub>        |            |      |     | 1000 | ns  |

| Fall time                         | t <sub>F</sub>        |            |      |     | 300  | ns  |

| Stop setup time                   | t <sub>SU</sub> ; STO |            | 4.0  |     |      | μs  |

#### **Synchronization Signal**

#### A02582

## **Sub-Screen Digital Processing Specifications**

|                                | Item                 | NTSC (f <sub>H</sub> = 15734 Hz) | PAL (f <sub>H</sub> = 15625 Hz) |  |  |

|--------------------------------|----------------------|----------------------------------|---------------------------------|--|--|

|                                | Sequence             | Y, R-Y, Y, B-Y                   | , Y, -, Y, -,                   |  |  |

|                                | Frequency            | 640                              | f <sub>H</sub>                  |  |  |

|                                | f <sub>T</sub> (MHz) | 10.070                           | 10.000                          |  |  |

|                                | Y only               | 320                              | <sup>I</sup> f <sub>H</sub>     |  |  |

| Sampling                       | f <sub>TY</sub>      | 5.035                            | 5.000                           |  |  |

|                                | R-Y only             | 80                               | f <sub>H</sub>                  |  |  |

|                                | f <sub>TR</sub>      | 1.258                            | 1.250                           |  |  |

|                                | B-Y only             | 80                               | f <sub>H</sub>                  |  |  |

|                                | f <sub>TB</sub>      | 1.258                            | 1.250                           |  |  |

| Quantization bits              | · · ·                | 6 b                              | its                             |  |  |

|                                | Y signal             | 960 f <sub>H</sub>               |                                 |  |  |

|                                | f <sub>CY</sub>      | 15.105                           | 15.000                          |  |  |

| D/A converter cleak (MUT)*1    | R-Y signal           | 240                              | 240 f <sub>H</sub>              |  |  |

| D/A converter clock (MHz)*1    | f <sub>CR</sub>      | 3.776                            | 3.750                           |  |  |

|                                | B-Y signal           | 240 f <sub>H</sub>               |                                 |  |  |

|                                | f <sub>CB</sub>      | 3.776                            | 3.750                           |  |  |

|                                | Horizontal dots      | 384                              |                                 |  |  |

|                                | Y only               | 256                              |                                 |  |  |

| Write                          | R-Y only             | 6                                | 4                               |  |  |

|                                | B-Y only             | 6                                | 4                               |  |  |

|                                | Vertical H count     | 80                               | 84                              |  |  |

|                                | Horizontal dots      | 37                               | 0                               |  |  |

|                                | Y only               | 25                               | 60                              |  |  |

| Read and display <sup>*2</sup> | R-Y only             | 6                                | 0                               |  |  |

|                                | B-Y only             | 6                                | 0                               |  |  |

|                                | Vertical H count     | 77                               | 83                              |  |  |

Note: 1. When the PLL divisor has the standard value, i.e., PLL7 to PLL3 = 10011.

2. Approximate values.

(The number of horizontal dots depends on the frame width adjustment, and the vertical H count depends on address correction.)

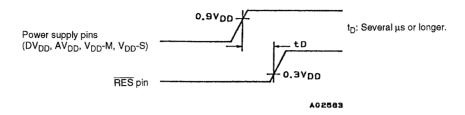

#### Initialization

1. RES pin: Reset

The  $\overline{\text{RES}}$  pin must be set low when power is first applied.

#### 2. Internal control registers

These LSIs go to the standby state (SBY = high) after a reset. When developing microprocessor software, be sure to send data to all registers. Also be sure to send zero data to the zero registers at addresses 14H and 15H.

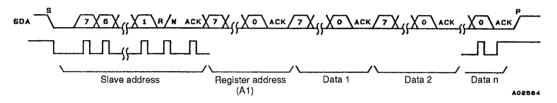

#### I<sup>2</sup>C Control

Data format

Data 1 is stored at register address A1. For data 2, A1 is incremented and data 2 is stored at A1 + 1.

Slave Address

|   | A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W |

|---|----|----|----|----|----|----|----|-----|

| ſ | 0  | 0  | 1  | 0  | 0  | 1  | 1  |     |

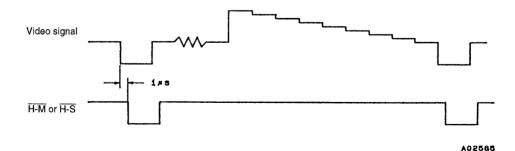

#### **Synchronization Signal Input**

1. Sync separator

The LC74401E requires sync separated (including AFC processing) V and H signals for both the main and subscreens. Since V is used for frame determination and H is used as the PLL reference signal, these signals must be input reliably.

• The standard values are set up assuming that the  $\overline{\text{H-M}}$  and  $\overline{\text{H-S}}$  inputs are delayed about 1 µs from the video signal horizontal synchronization signal.

- Equalizing pulses must be removed.

- Since noise in the synchronization signal will disrupt the screen image, care must be used in the layout of these lines.

- We recommend turning off sub-screen display when the synchronization signals are unstable, since such instability can disrupt the sub-screen image.

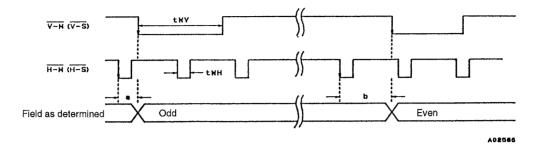

#### 2. Field determination circuit

Since the field is determined by the phase difference between the falling edges of the V and H signals, these signals must be input with the timing shown in the figure.

Here, a and b must be: a = 0.02 to 0.40 H, b = 0.60 to 0.98 H. The synchronization signal pulse widths are:  $t_{WV}$  > 1 µs,  $t_{WH}$  > 1 µs.

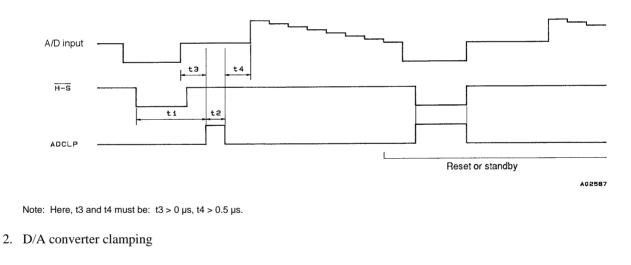

#### **Clamping Pulses**

1. A/D converter clamping

Since clamping pulses are output with the timing shown in the figure, they must set to fall in the pedestal range. On a reset or during standby mode, the  $\overline{\text{H-S}}$  input signal becomes a positive polarity signal, and is output as such.

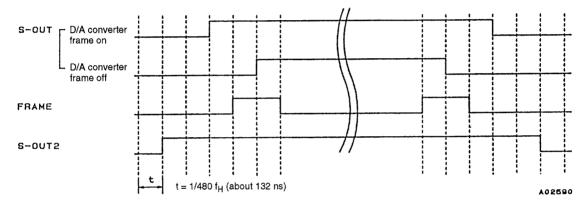

## **External Control Output Timing**

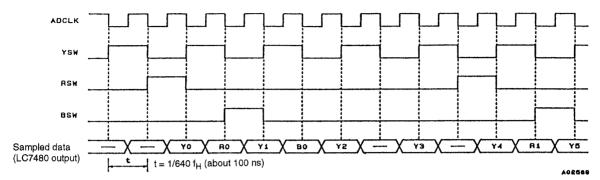

1. A/D converter (LC7480) related signals

Note: Since these are high speed signals, care must be taken to keep their lines as short as possible.

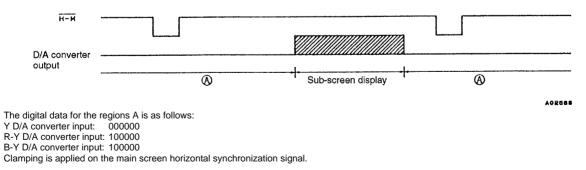

#### 2. Clamping related signals

Note: The FRAME signal is only output in D/A converter frame off mode.

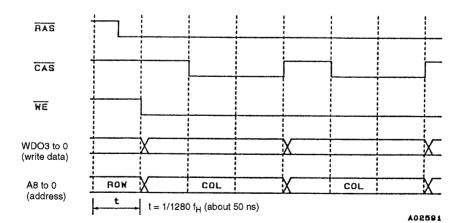

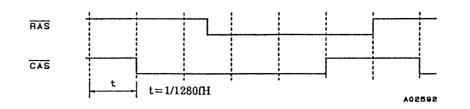

- 3. Video memory related signals

- Data write signals (page mode)

• Refresh signals (CAS before RAS)

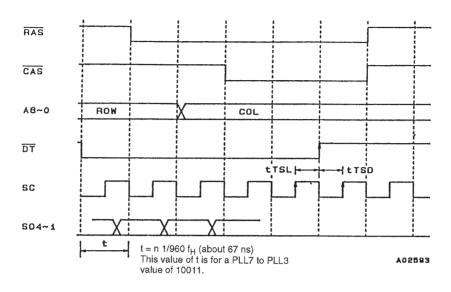

#### 3. Data transfer $\rightarrow$ serial read

Note: 1. Since these are high speed signals, care must be taken to keep their lines as short as possible.2. Contact your Sanyo representative when determining the memory to use.

| ■ Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design. |

| ■ In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.                                                                                                                                                                                                                                                                                                  |

| ■ No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.                                                                                                                                                                                                                                                                                                                                                   |

| Any and all information described or contained herein are subject to change without notice due to<br>product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification"<br>for the SANYO product that you intend to use.                                                                                                                                                                                                                                                                                                                                                                                   |

| ■ Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.                                                                                                                                                                                                                                                                                         |

| This catalog provides information as of September, 1998. Specifications and information herein are ubject to change without notice.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |