# SUBSCRIBER LINE INTERFACE CODEC FILTER, COFISLIC

PRELIMINARY DATA

- Single chip CODEC and FILTER including all LOW-VOLTAGE SLIC functions.

- Advanced 12V BJT, 5V CMOS 0.8um technology.

- Low external component count.

- Over-sampling A/D and D/A conversion.

- No functional trimming or adjustments required.

- Serves a wide range of specifications; i.e. ITU-T, LSSGR.

- $\blacksquare$  A-law, and  $\mu\text{-law}$  PCM and Linear voice coding, sw selectable

- GCI compatible interface.

- Programmable Digital-Filters for impedancematching, hybrid-balance, frequency-response and gain.

- Programmable Feeding-Resistance (2 x 50Ω to 2 x 400Ω) and current-limiting (0-69.3mA).

- Programmable voltage-drop according to transmission needs.

- 12kHz/16kHz Teletax Generation with Programmable Level 0-10 Vrms in 40mV steps including shaping and filtering.

- Integrated Ring-Generator with Zero-Crossing. Programmable frequency from 16.6Hz to 60Hz, programmable level up to 85Vrms, Integrated auto ring-trip.

- Signalling functions ON/OFF Hook, Gnd-key with filter and Programmable persistence check.

- Advanced test capabilities:

On-board line tests and circuit tests.

Signalling tests for meterpulse TTX and Ringing.

- Tone generator for circuit test.

- 3 Loop-back paths.

- Three operating conditions: Power Down, Active, Ringing. Off-hook programmable threshold-level in each of these conditions.

- Interface to High-Voltage SLIC to select modes, provide hard or soft Polarity-Reversal and sense HV (L3000N, L3000S, STLC3170) High Thermal condition.

- On-hook transmission capability.

- Selectable 2/4MHz backplane clock.

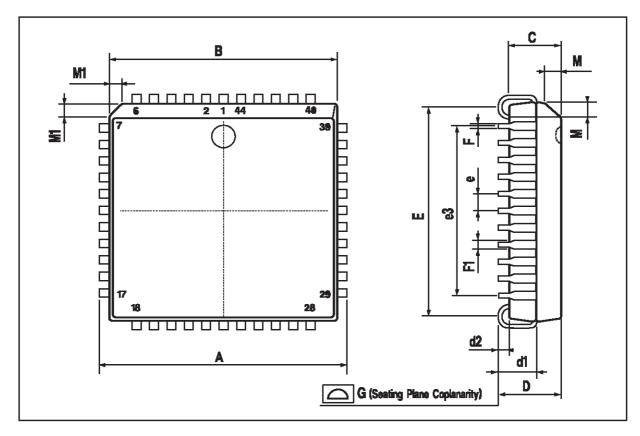

- Standard PLCC 44 package.

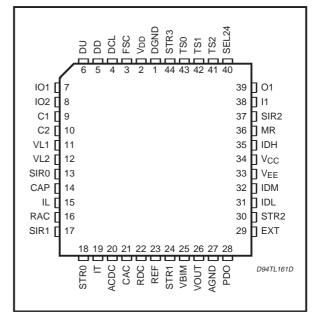

Figure 1: Pin Connection (Top view)

On chip Line-card identification.

## **DESCRIPTION**

The subscriber line codec-filter, STLC3040, is fabricated in BiCMOS (12V bipolar / 5V CMOS) technology. It uses Digital-Signal-Processing(DSP) to implement central-office telephone interface features: DC-feed, Supervision, PCM-Codec-Filter, Ring, Teletax metering (TTX) and Test functions. The STLC3040 is fully programmable and needs few external resistors and capacitors.

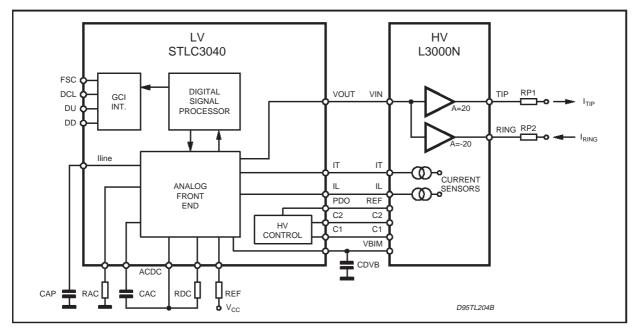

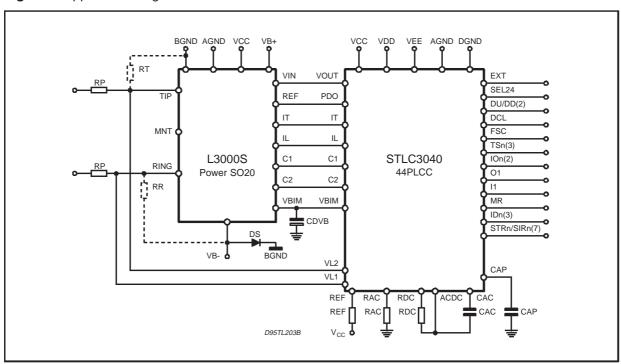

The STLC3040 interfaces the subscriber's line via the High-Voltage (HV) (L3000N, L3000S, STLC3170) device and the central-office back-

November 1998 1/49

#### **DESCRIPTION** (continued)

plane via a GCI compatible interface (see fig.2). The GCI handles all STLC3040 control and voice channel.

The STLC3040 processes the transversal line-current sensed by the ST HV (L3000N, L3000S, STLC3170) Line Driver Circuit and generates voltage-drive to the line via the HV (L3000N, L3000S, STLC3170), thus synthetizing the impedances required by various world administrations.

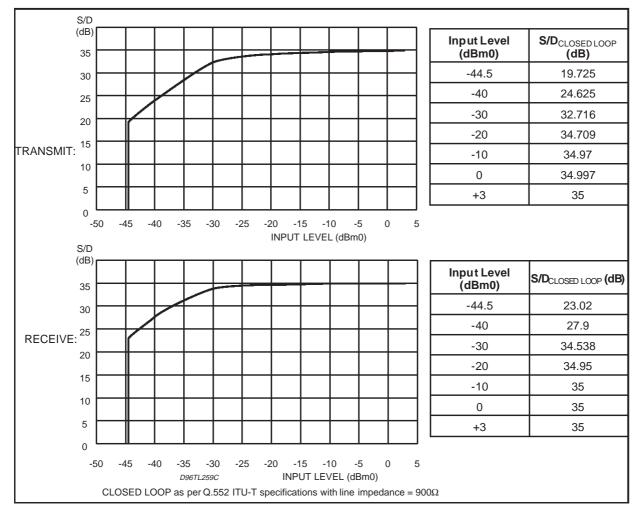

Line impedances as well as the two-to-four wire conversion synthesis are software programmable. Also Transmit (Tx) and Receive(Rx) AC frequency–response, determined by DSP-filters, guarantee voice-band flat-response. Tx and Rx Gains are programmable as well. Digitized voice can be encoded on A-law or u-law.

The DC characteristic is obtained by selecting limit-current value, DC-feed resistance (2 X  $50\Omega$  steps) and Drop-voltage. It also permits On-hook transmission and TTX pulse injection with filtering and shaping. TTX metering pulse generation (12 or 16kHz) has programmable amplitude up to 10 Vrms.

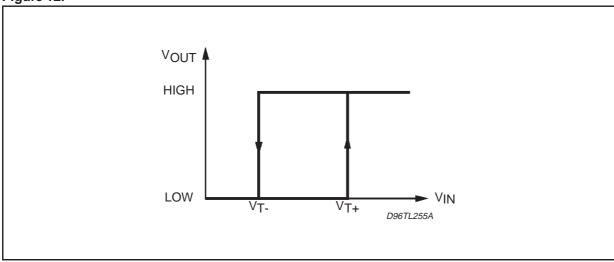

Off-hook detection with programmable thresholds

Figure 2: Functional Diagram.

is possible in all operating modes as described in section 4.

Ring-signal with zero-crossing start/stop injection is generated on chip with programmable frequency and amplitude. In addition, when Ringtrip is detected, the Ring-signal is automatically disconnected at the next zero-crossing.

Power consumption is kept low by providing a "Power-Down" mode where the HV-SLIC is switched off (Power Denial). A set of internal resistors connected to the line allows Off-hook detection in this mode. Overall power dissipation is around 50mW (max.) in Power Down mode.

Several testing features are included in the STLC3040, both for self-test and to test line leakage, capacitance ..etc, thus saving on test equipment and relays. Measured DC quantities are digitized and sent via the B1 voice channel to the backplane. With proper software selection each signal can be modulated by a 1KHz carrier before being sent to B1 voice channel. Programmable linear code, software selectable, boosts the calculation resolution.

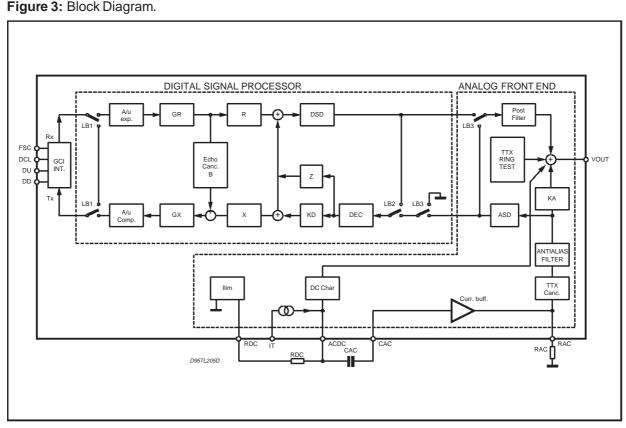

Sigma-Delta converters (ASD: Analog, DSD: Digital) make the conversion independent of technology parameters (fig. 3).

STLC3040 PIN DESCRIPTION (This list is grouped according to Function)

| N.           | Symbol | Type (*) | Description               |  |  |  |

|--------------|--------|----------|---------------------------|--|--|--|

| POWER SUPPLY |        |          |                           |  |  |  |

| 1            | DGND   | PS       | Digital Ground            |  |  |  |

| 2            | VDD    | PS       | 5V Digital Supply Voltage |  |  |  |

| 27           | AGND   | PS       | nalog Ground              |  |  |  |

| 33           | VEE    | PS       | Analog Supply Voltage     |  |  |  |

| 34           | VCC    | PS       | +5V Analog Supply Voltage |  |  |  |

# STLC3040 PIN DESCRIPTION (continued)

| N.   Symbol   Type (*)   Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | / this      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| (2Mbit/s) If SEL24 = 0, Clock Frequency = 2048KHz If SEL24 = 1, Clock Frequency = 4096KHz  43,42, TS0,TS1, DI GCI Select Time Slot Identifier Pins  3 FSC DI Frame Sync 8kHz GCI Interface 4 DCL DI Master Data Clock GCI Interface 5 DD DI Data Down link GCI Interface 6 DU OD Data Up link GCI Interface (Open Drain Driver)  INTERFACE TO HV SLIC  9 C1 Al/O State Control Signal 1. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode. Current sense for thermal indication.  10 C2 AO State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode.  28 PDO AO Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) in. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (hig impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.  11,12 VL1, VL2 AI Comparator Input. These are inputs of the comparator that senses the line voltage                                                                             | y this      |

| if SEL24 = 0, Clock Frequency = 2048KHz If SEL24 = 1, Clock Frequency = 4096KHz  43,42, TS0,TS1, 41 TS2  3 FSC DI Frame Sync 8kHz GCI Interface  4 DCL DI Master Data Clock GCI Interface  5 DD DI Data Down link GCI Interface  6 DU OD Data Up link GCI Interface (Open Drain Driver)  INTERFACE TO HV SLIC  9 C1 Al/O State Control Signal 1. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode. Current sense for thermal indication.  10 C2 AO State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode.  28 PDO AO Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) in When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.  11,12 VL1, VL2 AI Comparator Input. These are inputs of the comparator that senses the line voltage                                                                                                                     | y this      |

| If SEL24 = 1, Clock Frequency = 4096KHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | y this      |

| 43,42, TS0,TS1, TS2       DI       GCI Select Time Slot Identifier Pins         3       FSC       DI       Frame Sync 8kHz GCI Interface         4       DCL       DI       Master Data Clock GCI Interface         5       DD       DI       Data Down link GCI Interface (Open Drain Driver)         INTERFACE TO HV SLIC         9       C1       Al/O       State Control Signal 1. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode. Current sense for thermal indication.         10       C2       AO       State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode.         28       PDO       AO       Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) pin. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.         11,12       VL1, VL2       AI       Comparator Input. These are inputs of the comparator that senses the line voltage | y this      |

| 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | / this      |

| 3 FSC DI Frame Sync 8kHz GCI Interface 4 DCL DI Master Data Clock GCI Interface 5 DD DI Data Down link GCI Interface 6 DU OD Data Up link GCI Interface (Open Drain Driver)  INTERFACE TO HV SLIC 9 C1 Al/O State Control Signal 1. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode. Current sense for thermal indication. 10 C2 AO State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode. 28 PDO AO Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) in. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.  11,12 VL1, VL2 AI Comparator Input. These are inputs of the comparator that senses the line voltage                                                                                                                                                                                                                                   | / this      |

| 5       DD       DI       Data Down link GCI Interface         6       DU       OD       Data Up link GCI Interface (Open Drain Driver)         INTERFACE TO HV SLIC         9       C1       AI/O       State Control Signal 1. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode. Current sense for thermal indication.         10       C2       AO       State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode.         28       PDO       AO       Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) pin. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.         11,12       VL1, VL2       AI       Comparator Input. These are inputs of the comparator that senses the line voltage.                                                                                                                                                       | y this      |

| Box   DU   OD   Data Up link GCI Interface (Open Drain Driver)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | / this      |

| INTERFACE TO HV SLIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | / this      |

| 9 C1 AI/O State Control Signal 1. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode. Current sense for thermal indication.  10 C2 AO State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode.  28 PDO AO Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) pin. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.  11,12 VL1, VL2 AI Comparator Input. These are inputs of the comparator that senses the line voltage                                                                                                                                                                                                                                                                                                                                                                                                                                  | / this      |

| STLC3170) operating mode. Current sense for thermal indication.  10 C2 AO State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode.  28 PDO AO Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) bin. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.  11,12 VL1, VL2 AI Comparator Input. These are inputs of the comparator that senses the line voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | y this      |

| 10   C2   AO   State Control Signal 2. Combination of C1 and C2 defines HV (L3000N, L3000S, STLC3170) operating mode.    28   PDO   AO   Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) by pin. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.    11,12   VL1, VL2   AI   Comparator Input. These are inputs of the comparator that senses the line voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | y this      |

| 28 PDO AO Power down output. Proper bias current is provided to HV (L3000N, L3000S, STLC3170) by pin. When the current is 0 the HV (L3000N, L3000S, STLC3170) goes in Power Denial (high impedance). Proper combinations of PDO with C1, C2 set additional operating modes for STLC3170 High Voltage Interface.  11,12 VL1, VL2 AI Comparator Input. These are inputs of the comparator that senses the line voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | y this      |

| 11,12 VL1, VL2 Al Comparator Input. These are inputs of the comparator that senses the line voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| Power Denial allowing Off/Hook detection in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | in          |

| 15 IL AI Longitudinal Line-Current input IL = (I <sub>TIP</sub> - I <sub>RING</sub> )/100.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\neg$      |

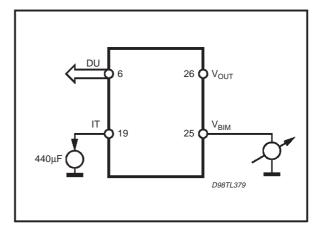

| 19 IT AI Transversal Line-Current input IT=(I <sub>TIP</sub> + I <sub>RING</sub> )/100.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\neg$      |

| 25 VBIM AI Battery image monitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\neg$      |

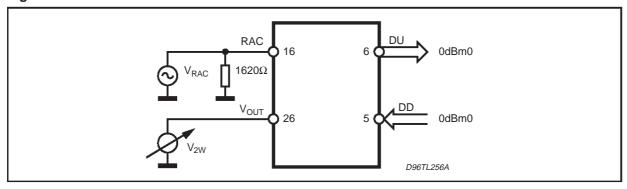

| 26 VOUT AO Output feeding the line voltage (DC, AC, RING, TTX) through H.V. HV (L3000N, L3000S, STLC3170).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\neg$      |

| 7, 8 IO1, IO2 DI/O Programmable GCI controlled I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\neg$      |

| 39 O1 DO Digital output written via GCI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\neg$      |

| 38 I1 DI Digital input read via GCI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\neg \neg$ |

| MISCELLANEOUS FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\neg$      |

| 29 EXT DI External Ring Sync. Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\neg$      |

| 36 MR DI Master Reset Input. Active High. The STLC3040 is forced in Loop-open and interr registers are preset to default values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | al          |

| 31,32 IDL, IDM AI Identification Code Signals, M+L ternary digits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 35 IDH DI H most significant bit, L least significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| 14 CAP AI/O Capacitor must be connected to this pin. Its value defines the Soft Battery Reversal slop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e.          |

| 16 RAC AI/O AC-Synthesis Reference Resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\neg$      |

| 20 ACDC AI/O AC/DC Line Split. Scaled line-current output, DC feedback input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\neg \neg$ |

| 21 CAC Al Splitter Capacitor. Scaled AC line-current input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| 22 RDC AI DC-Synthesis Reference Resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| 23 REF AI/O Reference Voltage Output. A resistor on this pin sets the internal reference curren                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| UNUSED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| 18,24 STR0,STR1 DI/O Reserved for testing, must be shorted to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| 30,44 STR2,STR3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| 13,17 SIR0, SIR1 DI/O Must be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| 37 SIR2 DI/O Can be left open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| (*) | Type | Description         | Type | Description          | Type | Description       |

|-----|------|---------------------|------|----------------------|------|-------------------|

|     | Al   | Analog Input        | DI   | Digital Input        | DO   | Digital Output    |

|     | AO   | Analog Output       | PS   | Chip Power/Ground    | OD   | Open Drain Output |

|     | AI/O | Analog Input/Output | DI/O | Digital Input/Output |      |                   |

#### **4 FUNCTIONAL DESCRIPTION**

The STLC3040 is implemented by a combination of analog and digital circuits, merging the best available analog and digital processing performances of the BiCMOS technology. In particular two main blocks of the STLC3040 can be identified: an analog front end interfacing the HV (L3000N, L3000S, STLC3170) and a programmable DSP. (See fig. 3)

#### 4.1 - Signal processing.

The line-current signal received in pin IT from the HV (L3000N, L3000S, STLC3170) is mirrored out of pin ACDC. On its way, its value is sensed to determine Off-Hook signalling. While in active conversation this istantaneous sensing is used for fast Hook signalling such as numbering. Then line-current AC and DC parts are splitted by RDC and CAC. The signal is processed to realize AC and DC impedance synthesis. Indeed IT pin carries the AC current due to voice signals present at line terminals and the DC current related to the specific V-I operating point.

During Stand-By mode signal is created by the DC current after AC part has been removed. This filtered Hook produces robust signalling in Standby mode or pause-period during reduced-power Ring mode.

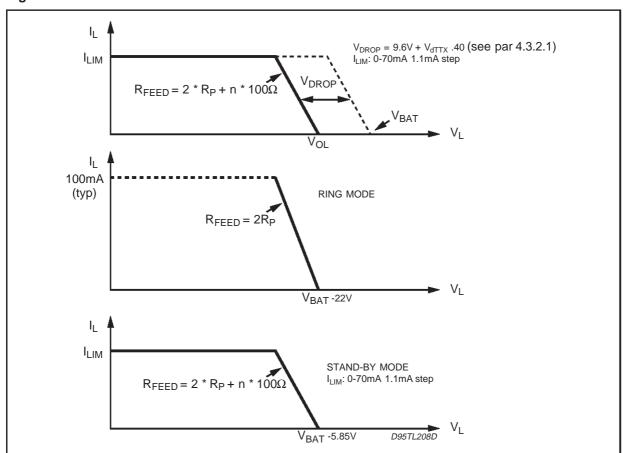

As far as the DC characteristic is concerned, two

different conditions are present and depend on loop resistance.

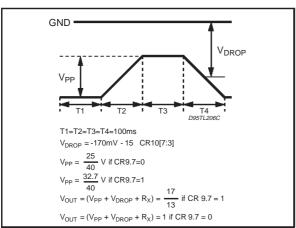

- a) Resistive Feed Region: the SLIC kit operates as a voltage source with a series resistance equal to  $(2Rp+n \cdot 2 \cdot 50\Omega)$ , where n can be programmed from 1 to 8 via CR8 register. Various values of voltage drops are possible as shown in Fig. 4.

- b) Constant current region: when IL reaches the programmed limiting current value (from 0 to 69.3mA; 1.1mA step via CR6 register), the Kit operates as a proper constant current source. (see Fig. 4).

Concerning AC Processing the AC current-signal is converted to voltage on the reference resistor RAC ( $1620\Omega$ ).

Line impedance (real or complex) synthesis is carried out thanks to programmable filters. All the filters are integrated in the digital side of COFIS-LIC except the so called KA filter that is in the Analog Front End.

KD and Z (in digital side) filters allow to match the line impedance if properly programmed. Furthermore KA ensures stability to impedance synthesis loop.

In the Receive direction (Rx), the Analog Front End (AFE) receives a 1-bit modulated composite signal, which represents part of the voltage to be forced into the line. It performs DAC and filtering

Figure 4.

functions. This voltage is then combined with the AC and DC analog impedance signals, plus a TTX pulse, in a summing buffer that feeds the Vin pin of the HV (L3000N, L3000S, STLC3170).

The architecture of the digital section is based on Digital Signal Processor which synthetises 7 digital filters (B, Z, X, R, KD, GX, GR). KA uses the some register value as KD. In Table 1 you can find the number of coefficients and their bit width for each filter.

Table 1:

| FILTER | NUMBER OF COEFFICIENTS | COEFFICIENT<br>WIDTH |

|--------|------------------------|----------------------|

| В      | 8                      | 14 BITS              |

| R      | 4                      | 14 BITS              |

| X      | 4                      | 14 BITS              |

| GR     | 1                      | 8 BITS               |

| GX     | 1                      | 8 BITS               |

| KA, KD | 1                      | 8, 14 BITS (*)       |

| Z      | 3                      | 14 BITS              |

<sup>(\*)</sup> KA is a subset of KD = most significant bits, (5-12) but sign bit, of KD register.

Filter coefficients can be programmed by 14 bits

deep registers. These internal filters can be enabled setting the most significant 5 bits of CR4 register and CR11 (1). PCM encoding and ITU-T high/lowpass-filtering are done by dedicated state machines. Setting the bit 0 of CR4 register A-law or  $\mu\text{--law}$  can be selected.

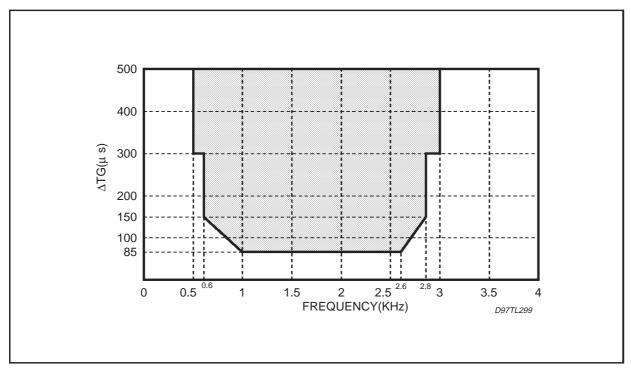

In order to match the complex line impedance, both amplitude and phase can be programmed using Filter Z.

The two to four wires echo cancellation is implemented thanks to programmable echo canceler (B Filter) with Gain and Group-delay equalizer.

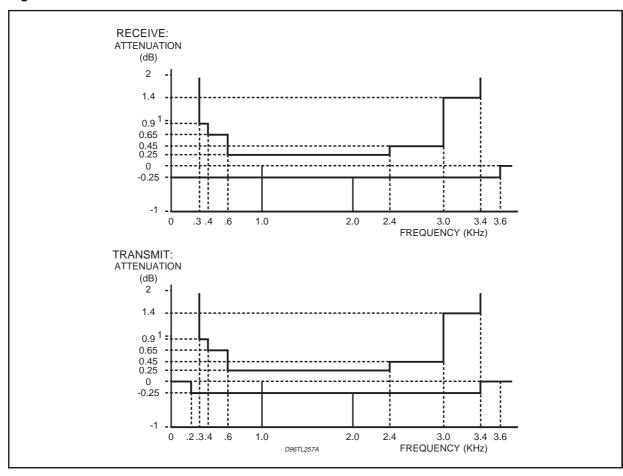

Two programmable FIR filters X and R, can be set in order to guarantee the best overall line frequency response in the frequency domain, according to the local specifications. In this way the signal distorsion can be reduced with 14-bits resolution.

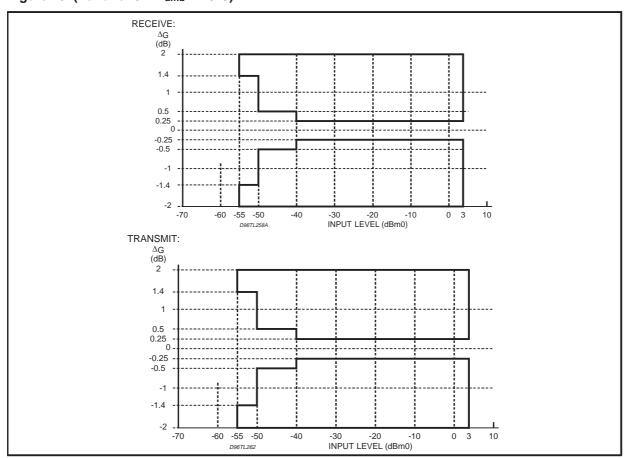

Gain Setting, both in transmission and in receive, is done by two FIR filters (GX for transmission, GR for Receive).

A coefficient optimization software let the users calculate GX and GR filters coefficients.

In transmission the maximum achievable gain without distortion is 3dB.

In receive the maximum programmable gain is 0dB.

Gain step resolution in both sides (Rx and Tx) depends on the value of the gains. See table below to gain/step accuracy.

Table 2.

| Tx & Rx Gain       | Step accuracy |

|--------------------|---------------|

| Xmax - 6dB (1/128) | 0.070dB       |

| Xmax - 12dB (1/64) | 0.14dB        |

| Xmax - 18dB (1/32) | 0.27dB        |

| Xmax - 24dB (1/16) | 0.56dB        |

| Xmax - 30dB (1/8)  | 1.16dB        |

| Xmax - 36dB (1/4)  | 2.5dB         |

| Xmax - 42dB (1/2)  | 6.0dB         |

Tx: Xmax = 3dB; Rx: Xmax = 0dB

The Voice Signal Processing is shown in Block diagram in Fig.3.

In the RX direction, after being decoded, the voice sample passes through a set of interpolator and correction filters. The signal is finally oversampled to a high-rate of 256kHz before being summed to the feed-back impedance synthesis signal.

Analog circuits performs Off-Hook sense and allows On-Hook Signaling.

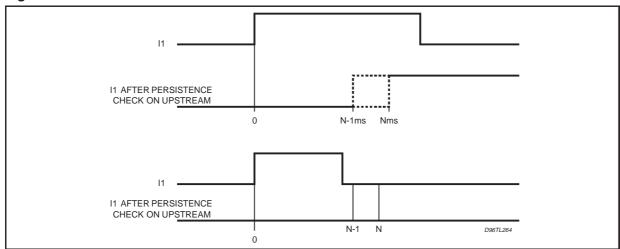

The longitudinal line current provided by the HV (L3000N, L3000S, STLC3170) is sensed at pin IL; Ground Key signalling is activated when the absolute longitudinal current on IL pin exceeds threshold. A low pass filter and programmable persistance filter (register CR3) elaborates the detection.

The Vbim pin receives from the HV (L3000N, L3000S, STLC3170) an information on the actual battery voltage (Vbim = Vbat/40), this voltage is then compared with the line voltage and one bit is set in the upstream data flow if Vline < ( $V_{OL}/2$ ). This allows the system to be tailored for different line requirements.

Line and circuit-test functions are discussed in detail in the appendix.

The HV (L3000N, L3000S, STLC3170) is driven by the STLC3040 through two ternary pins C1 and C2 (pin 9 & 10 of STLC3040) that define the operating state of the HV (L3000N, L3000S, STLC3170) (Table 3).

C1 and C2 are set according to the content of the bytes received by STLC3040 at DD pin (pin 5) of the GCI Interface. C1 pin is internally tied to a current-sensing circuit. It senses an extra current that the HV (L3000N, L3000S, STLC3170) issues when in thermal overload conditions.

Table 3: PDO = 50μA

|                |                    | pin 9 (C1)                            |          |           |  |  |

|----------------|--------------------|---------------------------------------|----------|-----------|--|--|

|                |                    | (*)V <sub>hv</sub> (*)V <sub>mv</sub> |          | (*)VIv    |  |  |

| nin 10         | (*)Vhv             | ST-BY                                 | TIP OPEN | RING OPEN |  |  |

| pin 10<br>(C2) | (*)V <sub>mv</sub> | CONV.NP                               | BB.NP    | RING NP   |  |  |

| (- /           | (*)V <sub>IV</sub> | CONV.RP                               | BB.RP    | RING RP   |  |  |

$PDO = 0\mu A$

|           |                    | pin 9 (C1)         |                    |                                                       |  |  |  |

|-----------|--------------------|--------------------|--------------------|-------------------------------------------------------|--|--|--|

|           |                    | (*)V <sub>hv</sub> | (*)V <sub>mv</sub> | (*)VIv                                                |  |  |  |

|           | (*)V <sub>hv</sub> | Ext. Indication    | Ext. Indication    | Ext.<br>Indication                                    |  |  |  |

| pin<br>10 | (*)Vmv             | Ext. Indication    | Ext.<br>Indication | Ext.<br>Indication                                    |  |  |  |

| (C2)      | (*)VIv             | Ext. Indication    | Ext.<br>Indication | Loop Open<br>(HV Internal<br>Resistors<br>disconnect) |  |  |  |

(\*) Vhv, Vmv, Vlv see digital interface electrical characteristics.

Through PDO pin (pin 28) the STLC3040 forces the HV (L3000N, L3000S, STLC3170) in Power Denial if the current at this pin is 0. When the STLC3040 sinks  $50\mu\text{A}$  the HV (L3000N, L3000S, STLC3170) will be turned on. In Power Denial, TIP and RING wires are disconnected from the HV (L3000N, L3000S, STLC3170) driver (Power Denial). Table 3 related to PDO =  $0\mu\text{A}$  is valid only for STLC3170.

VL1, VL2 pins sense, the Off-Hook when HV (L3000N, L3000S, STLC3170) is in power denial, allowing very low power consumption in On-Hook condition.

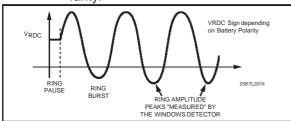

Other important features, which usually require external circuitry, like Test Tones, Ringing, Metering Impulse Injection are programmable via software. Ring signals can be programmed both in Amplitude and Frequency via CR9 register.

The Metering Pulse Injection Level can be set by the CR10 register. Ring-Trip detection is performed by a dedicated internal circuitry.

## 4.3 Slic Kit Operating Modes

STLC3040/HV (L3000N, L3000S, STLC3170) kit can work in three main modes:

- POWER DOWN

- ACTIVE

- RING

Each mode is selected by Command-Indicate (C/I) and Monitor GCI channels. Line State changes are signalled through either upstream C/I or SR register. During the switching between any two modes the indication is frozen for 10msec in addition to the programmed persis-

tance.

All operating modes with related C/I command bits and CR register bits are shown in table 13 pag 45.

#### 4.3.1 POWER DOWN

In this condition SLIC Kit reduces strongly its power consumption allowing Off-Hook detection. Only the internal circuitry dedicated to the Off-Hook detection is switched on.

C/I and CR1 register configuration (programmed by Monitor) defining Power Down Submodes are here below shown:

Table 4: Power Down Submodes

| SLIC KIT MODE       | C/I<br>(7) | C/I<br>(6) | C/I<br>(5) | CR1<br>(7) | CR1<br>(3) | CR1<br>(2) |

|---------------------|------------|------------|------------|------------|------------|------------|

| EXTERNAL INDICATION | 0          | 0          | 0          | 0          | Х          | Х          |

| LOOP OPEN           | 0          | 0          | 1          | Х          | Χ          | Χ          |

| STAND BY            | 0          | 0          | 0          | 1          | 0          | 0          |

| GROUND START        | 0          | 0          | 0          | 1          | 1          | 1          |

#### 4.3.1.1 - External Indication

When this mode is selected both STLC3040 and HV (L3000N, L3000S, STLC3170) are set in Power Denial. STLC3040 cuts the bias current, sunk by the HV (L3000N, L3000S, STLC3170) via the PDO pin. In this mode the HV (L3000N, L3000S) shows a high impedance on TIP and

RING pins; theHV shows on TIP pin the RT impedance and on RING pin the RR impedance if it integrates the 2 external resistors RT and RR (STLC3170). This mode is used to get a low power consumption obtaining supervision only via the STLC3040 and a resistive sensing network. The total power consumption of the SLIC Kit in this mode is under to 50mW (being almost 0 the consumption from battery).

#### 4.3.1.2 - Loop Open

This mode can be selected only if the High Voltage integrates the two external resistors (RR, RT see fig. 5) of the feeding and sensing circuitry. This is implemented on the STLC3170 high voltage device.

#### 4.3.1.3 - Stand-By

SLIC behaves like a constant current source with typical 7mA feeding current. Open loop voltage is equal to (V<sub>bat</sub> - 5.85V). COFISLIC power consumption is reduced to 150mW typical. Current limit and Off-Hook threshold are programmable by register CR7. Both off-hook and ground-key detectors are operating.

#### 4.3.1.4 - Ground Start

The SLIC is set in Stand-By with the TIP wire (the most positive wire) in high impedance.

The current feeding is equal to Stand-By mode current feeding.

Figure 5: Application Diagram.

#### 4.3.2 - ACTIVE

This operating mode is selected by the card processor after an Off-Hook detection in order to allow signal transmission on the line. Both Off-Hook and ground-key detectors are operating.

GCI Command - Indicate channel and CR1 register configuration (programmed by GCI Monitor) defining Active modes are herebelow shown:

Table 5:

| SLIC MODE    | C/I<br>(7) | C/I<br>(6) | C/I<br>(5) | CR1<br>(7) | (*)CR1<br>(3) | (*)CR1<br>(2) |

|--------------|------------|------------|------------|------------|---------------|---------------|

| ACTIVE       | 0          | 1          | 0          | Χ          | 1/0           | 1/0           |

| ACTIVE + TTX | 0          | 1          | 1          | Х          | 1/0           | 1/0           |

(\*) This condition refers to STLC3040 only. If CR1.3 and CR1.2 are equal (either 0 or 1) both STLC3040 and HV (L3000N, L3000S, STLC3170) are in Active State. If CR1.3 and CR1.2 are different, one of two line wires will be set in high impedance, while the STLC3040 will still be in Active mode.

Current Limit and Off-Hook threshold are programmable by CR6 register. If the fifth bit of the Command-Indicate channel is set to 1 the Teletax Signal is superimposed to the voice signal.

#### 4.3.2.1 - DC feeding

As far as DC characteristic is concerned, SLIC is basically working as a constant current device. It turns automatically into a resistive feeding when the programmed current limitation value cannot be held due to high line resistance. In active mode the constant current value is programmable

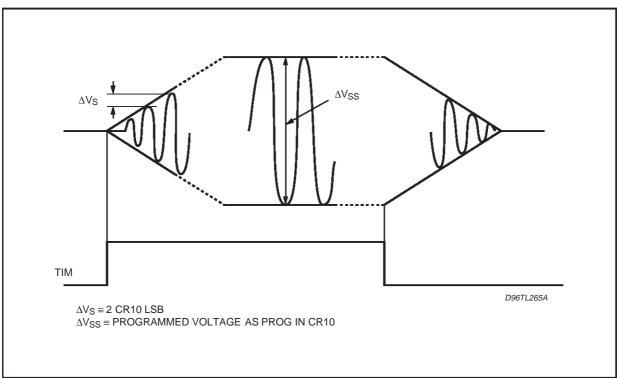

Figure 6: TTX Shaping

in 1.1mA steps ranging from 0mA to 69.3mA. In resistive feeding region SLIC kit operates like a constant voltage source with a series impedance Rfeed =  $2\text{Rp+n} \cdot 2 \cdot 50\Omega$  (being Rp the external protection resistor and n a value set from 1 to 8 via CR8 register).

Voltage drop (Fig. 4) can be programmed in order to optimize voltage feeding characteristic, according to AC signal swing requested (ex: voice, voice + 2Vrms TTX, voice + 5Vrms TTX):

$V_{DROP} = Vd3000 + 40 (VdAC + VdTTX)$

Vd3000 = drop due to internal HV (L3000N, L3000S, STLC3170) architecture (2.8V typ.)

VdAC = AC headroom on Vout (170mV typ.)

VdTTX = TTX headroom on Vout (from 0 to 465mV (15x31) typ. depending on programmed TTX level).

At HV (L3000N, L3000S, STLC3170) two wires the following equation must be used:

$VDROP(TIP/RING) = 9.6V + CR10 [7..3] \cdot 15mV \cdot 40.$

#### 4.3.2.2 - Metering Generation

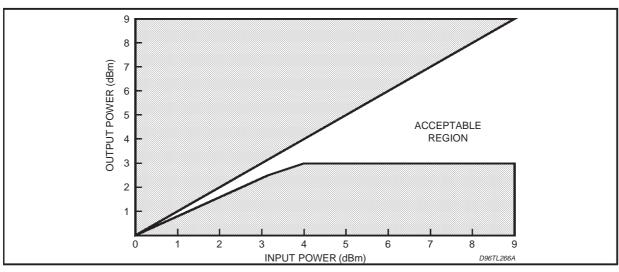

TTX signal is internally generated, filtered and shaped. Shaping is carried out by a gradual increase of metering pulse level of a level step (see CR10 register) per signal half period (please see Fig. 6). TTX can be programmed both in frequency (12 or 16 KHz ) and open loop amplitude (from 0 to 10Vrms in 255 steps). The output impedance at TTX frequency is just 2 x  $R_p$ ; therefore the proper value should consider the drops

8/49

across the 2Rp. Filtering is performed inside the device without external circuitry.

Feeding voltage polarity can be reversed in both soft and hard ways under software command.

#### 4.3.2.3 - Boost Battery

To supply very long lines (high loop resistance), the SLIC can be set in "Boost battery" mode. In this mode the line is fed with a total battery voltage equal to |Vb+| + |Vb-|, keeping the same current limiting values as in active mode. The Vb+ battery is the same positive supply voltage needed for ringing generation.

#### 4.3.3 - RING

In this mode COFISLIC provides ringing signal equivalent to a maximum 85Vrms ring line voltage. HV L3000N and L3000S handle a maximum 65Vrms balanced ring signal; HV STLC3170 handles a maximum 85Vrms. It is possible to reduce power consumption if Power Reduced Ring mode is chosen. The output impedance is represented only by the two Rp protection resistors and the current is limited to 100mA.

C/I and CR1 register configuration (programmed by GCI monitor channel) define Ring conditions as herebelow shown:

Table 6:

| SLIC MODE             | C/I<br>(7) | C/I<br>(6) | C/I<br>(5) | CR1<br>(7) | CR1(*)<br>(3) | CR1(*)<br>(2) |

|-----------------------|------------|------------|------------|------------|---------------|---------------|

| RING                  | 1          | 1          | Χ          | Χ          | 1/0           | 1/0           |

| Reduced Power<br>Ring | 1          | 0          | Х          | Х          | 1/0           | 1/0           |

(\*) CR1.3 has to be equal to CR1.2: 0 or 1

If unbalanced ringing is requested, SLIC can support also external ringing injection configuration, providing both logic command for relay driver and ringing detection circuitry.

#### 4.3.3.1 - Ring Generation

When the ringing function is selected, a low level ringing signal (1.5Vrms typ.) is generated inside the STLC3040 and provided on the VOUT pin. This signal is then amplified and injected in balanced mode into the line through the HV (L3000N, L3000S, STLC3170), with superimposed DC voltage of 24V typical. Both ringing frequency and amplitude are software programmable.

The first and the last ring cycles are synchronized by the STLC3040 so that the ringing signal always starts and stops with zero phase.

In Ring mode the Off Hook indication is asserted whenever during two consecutive ring periods ( or an equivalent time in pause) the mean value of the IT current exceedes the programmed threshold. After the persistance time the Off Hook is

sent to C/I upstream.

## 4.3.3.2 - Power Reduced Ring

The modes in Table 6 differ only during the ringpause phase.

During the pause of reduced-power-ring mode the SLIC Kit is set in Stand-By.

The pause state is forced by stop ring command (C/I.5 downstream = 0) or by the detection of Off-Hook

#### 4.3.3.3 - Unbalanced Ringing

The device allows an unbalanced Ring application. This application requires an external ringing generator. A digital I/O pin can be used to drive the external relay driver.

An external ring sync. signal synchronised on the Vring zero crossing, must be provided on pin 29 of STLC3040. The external ring frequency must be the same as the value programmed in the internal register.

## **4.4 - TESTING FEATURES**

STLC3040/HV (L3000N, L3000S, STLC3170) kit allows to perform up to 11 tests. They are aimed at covering the following issues.

- Line and Battery Characteristics AC, DC Leakage.

- 2. SLIC Kit block testing.

- Signal Path Behavior

Every test is set by internal registers, which are written through GCI data down Monitor.

Test results are typically digitalized, codified and dropped in the first PCM channel (byte B1) of GCI interface. For four go/nogo tests (Analog Loopback, Ring Generator, TTX Generator and TTX filter) the result of the test is also written in one bit of CR5 register that is readable through Monitor. Test functions are carried out with SLIC Kit in a mode set automatically by COFISLIC. For detailed explanation about tests see chapter 6.

## 4.4.2 - Loop Backs

LOOP1 and LOOP2 bits of CR4 register set up some internal loop backs. This feature is typically used for COFISLIC tests (see fig. 3). Any Loopback is enabled by CR1.5 bit. Loopback

Any Loopback is enabled by CR1.5 bit. Loopback type is selected by register CR4.

There are three types of loopback.

Loopback 1 (CR4.2 = 0, CR4.1 = 1) simply copies the downstream B1 to the upstream B1 through the GCI interface. In this case no Rx signal is sent to the line. The kit operates as previously set.

Loopback 2 (CR4.2 = 1, CR4.1 = 0) sets Kit SLIC in Active mode. It copies the output of DSD (Digital Sigma Delta converter) to the input of the DEC

block, as shown in fig. 3. Rx signal goes on to the line. Please note that this loopback function cuts off the Tx channel connection to the line.

All other functionalities are those of Active mode.

Loopback 3 (CR4.2 = 1, CR4.1 = 1) sets Kit SLIC in Active mode. Rx signal is prevented to go the line. Tx path is cut off from the line as well. Output of ASD is copied to input of AFE port filter. DSP part can be still exercised via B1. All the functionalities are those of active mode.

#### 4.4.3 - Test Tones Generation

In Active mode STL3040 can generate either 1kHz or 800Hz frequencies towards the 2-wire line. The two tones can also be enabled at the same time.

TON bit of CR1 register enables the 1 kHz test tone generator. 800Hz is enabled by CR5[3.0] = 4h.

800Hz amplitude is programmable through the same register (CR10) used to set TTX amplitude. 1kHz level is fixed at PCM full scale and can be modified changing Rx channel gain.

#### 4.5 COFISLIC Reset

Any reset to COFISLIC sets SLIC kit in External Indication. COFISLIC is set in Power denial. There are four different reset sources:

Power-On Reset,

Reset pin MR (pin 36),

Reset bit (SOP command bit 4).

During Reset, output pins are set as follows:

| DU  | (pin 6)  | High impedance |

|-----|----------|----------------|

| C1  | (pin 9)  | Vhv            |

| C2  | (pin 10) | $V_{hv}$       |

| PDO | (pin 28) | High impedance |

| O1  | (pin 39) | Low Level      |

Additionally a Reset of the DSP part of the COFISLIC is triggered by CLK fail detection (see also page 17).

## 4.5.1.1 Power On Reset

When voltage at VDD pin crosses over an internal fixed threshold (typ. 2.5V) COFISLIC is reset.

#### 4.5.1.2 Reset Pin MR

If an high level is applied to pin 36 (MR) the COFISLIC is reset.

MR pin has built-in filter to reduce spike sensitivity. Spikes smaller than 90ns are neglected.

Therefore at MR pin a high level is surely recognised as a Reset if it is present for at least 2µs.

## 4.5.1.3 Reset bit RST (SOP command bit 4)

If RST bit is programmed to 1 COFISLIC is reset. SOP register is set by GCI down stream channel.

Until the end of the current command processing, the GCI is kept active.

#### 4.5.1.4 - CLK fail Reset

Clock fail triggers a reset routine of the DSP which lasts, until the first good frame that follows the failed ones.

In active mode during the Reset routine, the voice channel of "Data up" (Du, pin 6) is forced IDLE dependent on the selected codification law.

As far as "Data down" (DD, pin 5) is concerned, the voice channel does not reach the Vout during this phase.

Z sinthesys is partially performed, the DSP branch is not active while the analog loop is kept active.

Coefficients and CR registers' contents do not change because of this partial reset, GCI state as well. Metering pulse injection signaling is not affected too. Ring generation and ring trip detection are not influenced too.

## 4.5.2. Start-up State

During reset the device is in Power- Denial Mode. After Reset, COFISLIC is automatically switched to its basic start-up state in which it uses internal default values for all filters and settings (AC and DC).

Programmed coefficients of filters are not reset. Bit 0 of CR6 register, FIXC, is set to 1, this means that fixed values are used after a Reset until FIXC is set to 0.

Even if FIXC = 1, both checksum and reading of filter coefficients are carried out on formerly programmed coefficient set.

Table 7: Fixed Filter Coefficients

| Filter | Coefficients (h)                   |  |  |  |

|--------|------------------------------------|--|--|--|

| KA, KD | 0E00                               |  |  |  |

| Z      | 019C, 24A0, 1600                   |  |  |  |

| Х      | 149A, 0521, 3F40,3EF2              |  |  |  |

| R      | 1879, 39E0, 00B4,0006              |  |  |  |

| GTX    | FF                                 |  |  |  |

| GRX    | 60                                 |  |  |  |

| В      | 0, 0, 0, 0050, 0680, 06D0, 0, 3C80 |  |  |  |

SLIC is switched to operating mode carried by GCI Command Indicate at least two frames after reset. SLIC status and Filter configuration can be changed by SOP and COP commands.

After reset the device is internally set as follows:

- configuration registers are set to their default

values (see Chapter 4-8 Configuration Register)

- RST bit (SOP command bit 4) is set to 1 to indicate that a reset has occured

- GCI interface is reset. After software Reset its former state is kept. On-going GCI communication is stopped

- DU is in high impedance state

- FIXC = 1 (CR6 Register) Fixed Coefficients are selected

- DC characteristics of SLIC-Kit

- External Indication

- Normal Battery

- Test Disabled

- Persistence for Off-Hook and I1: 10ms

- Persistence for Ground Key: 20ms

- Ring Trip threshold = 4.2mA

- Ilim = 22mA in active mode

- Ilim = 7.7mA in Stand-By mode

- Off-Hook detection threshold in active mode = 10mA

- Off-Hook detection threshold in Stand-By mode = 7.7mA

- Feeding Resistance in either Active or Stand-By mode = 2 · (50 + Rp) (fuse impedance value is not included)

- Ring: Internal

- Ring Frequency = 25Hz

- Ring Voltage = 65Vrms

- Line Voltage Drop = 28.2V

- External Indication Voltage Threshold for Off-Hook detection = 9.0V

- A-law is programmed

#### AC characteristics of SLIC-Kit

- Metering with Teletax

- Line Impedance: (Synthetized Impedance + 2

Rp) = 700Ω + 2Rp

- Balance Impedance:  $910\Omega$  / / 62nF

- Tx Gain: 0dBr

- Rx Gain: -7dBr

- Teletax Voltage onto line V<sub>TTX</sub> = 10Vrms

- Teletax Frequency = 16kHz

- Battery Reversal: Hard

#### Further after the reset

- I/O pins are set as inputs

- PD bit of CR1 is reset (means STLC3040 in Power-Denial mode).

- All bits of Signalling Register are masked

- Data Upstream C/I byte is reset to 0

Check Configuration-registers reset-value for more detailed information.

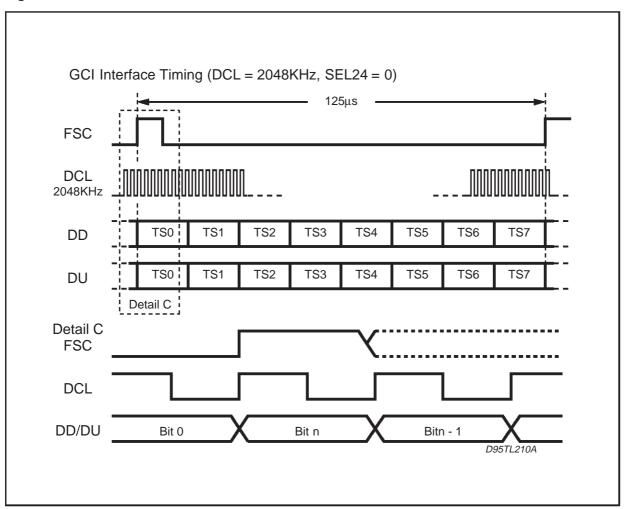

#### 4.6 GCI Backplane Interface

GCI is a standard serial interface for interconnection of SLIC kit to the line card backplane.

The digital interface is used to transfer status information to and from the SLIC as well as to transfer filter coefficients for the DSP.

With this approach an analog Line Card could be replaced by an ISDN one and viceversa without need to change the interface to the linecard controller

As far as physical level is concerned this standard consists of four wires:

- Serial Transmitted data to the backplane: DU

- Serial Received data from the backplane: DD

- 8KHz Frame Synchronization: FSC

- Master Data Clock (2048KHz or 4096KHz): DCL

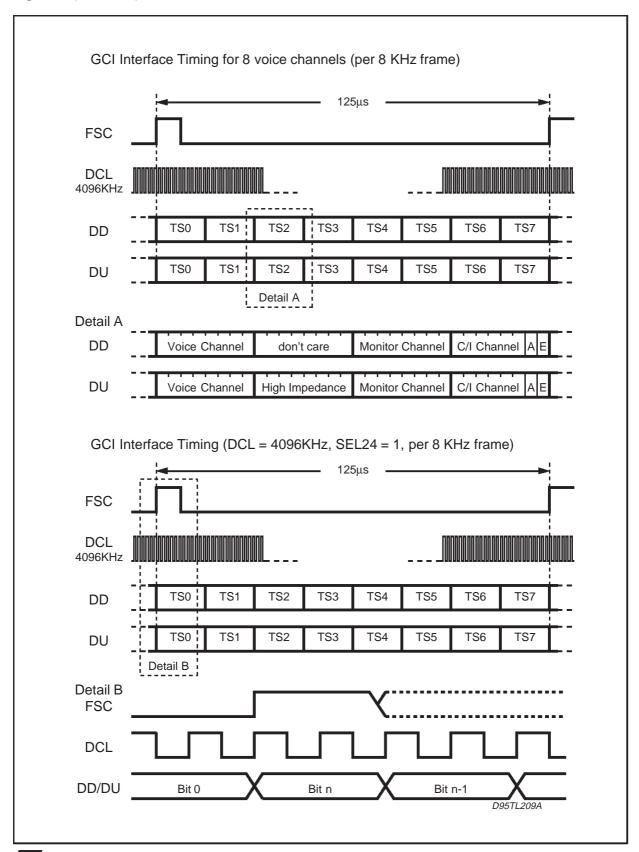

The frame is divided into eight time-slots which contains four bytes each. Bit rate in both directions is 2048Kbit/sec and it's not affected by clock frequency. This can be chosen setting SEL24 pin. Eight GCI time slots are selectable via three pins TS2-TS0 (see Table 8).

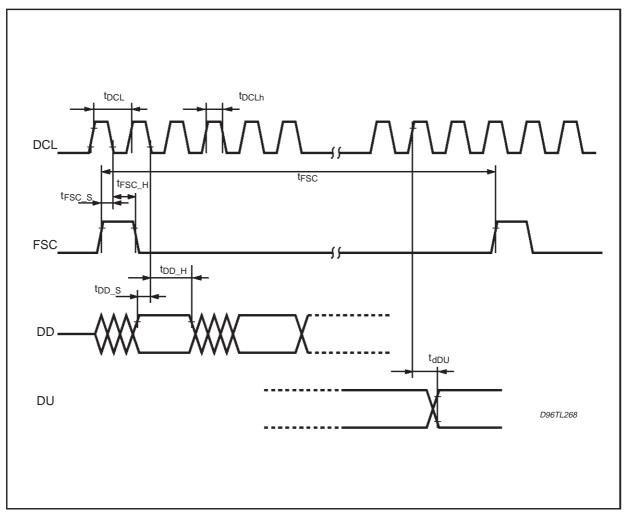

For every time slot the first bit, received or transmitted, is the Most Significant one, according to timing diagram shown in fig. 7.

Information is clocked out on the rising edge of data clock and it is latched in on the falling edge of DCL signal.

Frame Synchronization FSC is a 8KHz signal and its rising edge gives the time reference of the first bit in the first GCI (input or output) channel and resets the slot counter at the next falling edge of the clock every frame.