MPW

# DMILL

# **Mixed Analog/Digital Radiation Hard BiCMOS**

#### An emerging need in HEP

The decision to develop new equipment for High Energy Physics (HEP) research has led the need for ultra rad hard technology. The radiation tolerance for detector electronics adjacent to proton collision areas can be above 10 Mrad. Furthermore, the low level of the detector signals imposes very high signal to noise ratios. To meet these new requirements, the French Commissariat à l'Energie Atomique (CEA), an organization highly involved in almost all advanced nuclear physics research, has, by taking advantage of its extensive experience in silicon on insulator (SOI) hardened techniques, developed the **DMILL** technology (Durci Mixte Isolant Logico analog/digital Linéaire), a mixed technology hardened to tolerate more than 10Mrad and 10<sup>14</sup> neutrons/cm<sup>2</sup>. TEMIC started the industrial transfer of DMILL into its Nantes (France) factory in 1995. Testing of prototyping based on this technology and the subsequent large scale production are planned for early 1997 .

# **1E14 n/cm<sup>2</sup>**

## Civilian nuclear field

High radiation hardness levels are also of interest for engineers designing civilian nuclear equipment. Up to now they have not been suitable electronics for operating under very high radiation levels in hot areas in nuclear power plants and nuclear waste processing facilities. The rule has been to use discrete or passive equipment. As it is hardened against both photons and neutrons, DMILL technology provides a very efficient solution for these environments.

Photo CEA

#### **Performance Demonstration**

This technology, which has been selected by numerous groups for the prototype electronics of the two major LHC (Large Hadron Collider) experiments (ATLAS & CMS) has demonstrated high integration levels (1 Million transistors per cm<sup>2</sup>) for mixed analog/digital circuits, very low noise features and high radiation hardness. For example, the data for a CEA sliced 16-bit microprocessor designed for civilian nuclear applications show an extremely low sensitivity to radiation.

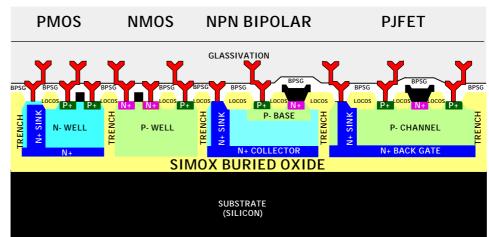

#### **DMILL Cross Section**

On one single chip, DMILL access to provides 4 different active devices. Two low-noise N and P MOS with transistors 0.8µm minimum gate length are available. For fast-low noise analog applications, there is a NPN bipolar transistor with a typical gain of 150. A-P type JFET is also proposed as well as resistors and capacitors. All these components are hardened to tolerate a combination of and  $1E14n/cm^2$ 10Mrad fluence.

#### **DMILL Basic Electrical parameters**

Access to DESIGN KIT requires signing a Non Disclosure Agreement. This includes kit electrical and topological (for Spice, data files ELDO environments). Cadence DRC and LVS tools are also available as well as some Input/ Output cells.

| Parameter      | Typical Value | Unit  | Comments                                                     |

|----------------|---------------|-------|--------------------------------------------------------------|

| MOS TRANSISTOR |               |       |                                                              |

| Leff N         | 0.62          | μm    | Electrical length of a 0.8µm N-channel device                |

| Leff P         | 0.78          | μm    | Electrical length of a 0.8µm P-channel device                |

| VTN            | 0.80          | V     | Threshold voltage for 25/0.8 N transistor                    |

| VTP            | -0.80         | V     | Threshold voltage for 25/0.8 P transistor                    |

| IDSN (0.8)     | 7.5           | mA    | Drain current of a 25/0.8 N Transistor with VGS=VDS=5.0V     |

| IDSP (0.8)     | 4.25          | mA    | Drain current of a 25/0.8 P Transistor with VGS=VDS=5.0V     |

| NPN-BIPOLAR    |               |       |                                                              |

| Beta (1.2*1.2) | 175           | NU    | NPN 1.2*1.2 ideal forward beta                               |

| BVCEO          | 15.0          | V     | Breakdown of collector/emitter junction with base open       |

| BVCBO          | 17.0          | V     | Breakdown of collector/base junction with emitter open       |

| P-JFET         |               |       |                                                              |

| VPPJ1.2        | 1.2           | V     | Pinch-off voltage of a 100/1.2 P-JFET                        |

| GDPJ1.2        | 1.135         | μS/μm | Drain Transconductance of a 100/1.2 P-JFET (VGS=0V, VDS=-3V) |

#### **MPW Prototyping**

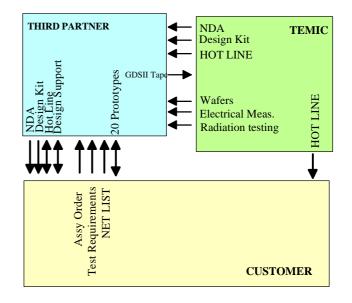

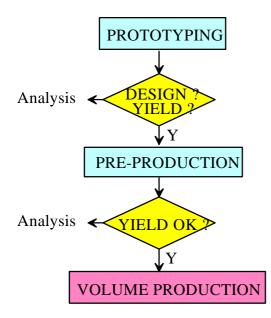

Prototyping is required for validating new functions or architectures. It also allows assessing yield values before large scale production. Cost reduction is achieved by sharing the non-recurring expenses of mask and wafer manufacturing between several users. Multi Project Wafers (MPW) activity is available through a third partner, who also offers front-end and back-end services. The standard offer is the delivery of 10 to 20 untested prototypes with the wafer batch electrical measurements values. Production of MPWs will begin early in 1997.

### **Manufacture**

Designer has access to electrical parameters and Topological rules. He provides TEMIC with a GDSII tape including all information required for circuit manufacture. After level checks (minimum size and pitch), reticules are fabricated and production starts at MHS. The wafers are inspected before delivery to ensure they meet electrical specifications. Unless it is not required, radiation hardness is checked up to 10Mrad or more by exposure of the components to Xrays. Eelectrical and dimensional measurement are provided with the wafers .

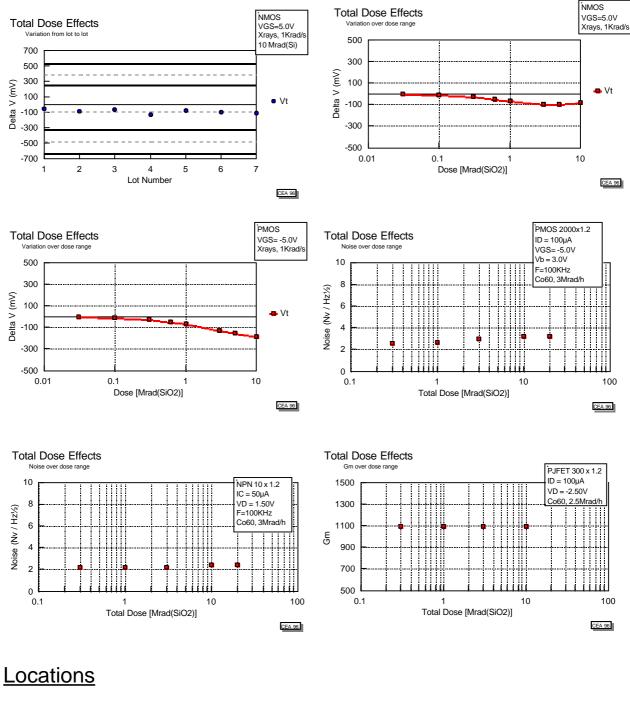

#### **Radiation assurance**

To provide radiation assurance, the variation of each radiation-sensitive parameter with dose is monitored by the irradiation of test structures up to 10Mrad on a Statistical Process Control basis. In addition, regular extended irradiation tests, including neutron and post-irradiation effects, are made to verify functionality and noise performances on specific mixed analog/digital test structures.

TEMIC France Les Quadrants 3, avenue du Centre - BP 309 78054 St-Quentin-en-Yvelines Cedex France Tel: (33) 1-30 60 70 00 Fax: (33) 1-30 64 06 93

TEMIC Scandinavia Kavallerivägen 24, Rissne P.O.B. 2042 17202 Sundbyberg Tel: (46) 87 33 00 90 Fax: (46) 87 33 05 58

#### TEMIC U.S.A.

2201 LaurelWood Road P.O.Box 54951 Santa Clara, CA 95056 U.S.A. Tel: (1) 408 970 57 00 Fax: (1) 408 970 39 79

TEMIC Italy Via Stephenson 94 I-20157 Milan Tel: (39) 2 332 121 Fax: (39) 2 332 12 201 TEMIC U.K.

Easthampstead Road, Braknell Berkshire RG12 1LX U.K. Tel: (44) 1344 48 -5757 Fax: (44) 1344 42 -7371

TEMIC Japan Roppongi First Bldg. 17F 1-9-9, Roppongi Minato-Ku, Tokyo 106 Tel: (81) 3 55 62 -3321 Fax: (81) 3 5562 -3316

#### **TEMIC** Germany

Microelectronic Gmbh Erfurterstrasse 31 D-85386 Eching Germany Tel: (49) 89 31 97 0-0 Fax: (49) 89 31 94 621

TEMIC Spain Electricida S.A. Principe de Vergara, 112 28002 Madrid Tel: (34) 1 562 -7600 Fax: (34) 1 562 -7514