# 100 and 120 MHz 3.45 Volt 5x86 CPU

#### PRELIMINARY DATA

1/39

#### ■ 586-CLASS PERFORMANCE

- 100 and 120 MHz core speeds with 33, 40, and 50 MHz bus options

- 16 KByte write-back cache

- Superpipelining and branch prediction

- Data forwarding

- Decoupled load/store unit

- On-chip FPU with 64-bit interface

- SMALL FOOTPRINT

- 208-pin QFP, 168-pin CPGA, 168-pin PPGA

#### BUILT-IN POWER MANAGEMENT

- System management mode

- Suspend mode

- FPU, pipeline, and cache auto idle

- Stop clock capability

- Operates at 3.45V with 5V tolerant I/O

#### ■ x86 INSTRUCTION SET COMPATIBLE

- Runs Windows, DOS, UNIX, Novell and others

The ST5x86<sup>™</sup> microprocessor is a high performance 586-class CPU compatible with all popular x86 operating systems, including DOS, Windows, Windows NT, Windows95, UNIX, Novell, OS/2 and Solaris.

The 586-class performance is achieved by a superpipelined architecture in the integer unit combined with data forwarding, branch prediction, 16-KByte write-back cache, single-cycle instruction decode, and single-cycle execution.

The 5x86 processor provides many power saving features that make it ideal for power sensitive systems. The CPU automatically powers down the Floating Point Unit (FPU) and other internal circuits when they are not in use.

Fast entry and exit from System Management Mode (SMM) allow frequent use of the SMM feature without noticeable performance degradation.

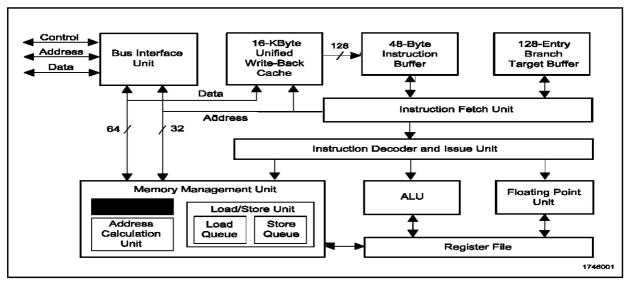

#### **BLOCK DIAGRAM**

#### October 1995

This is advanced information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

#### **1.0 ARCHITECTURE OVERVIEW**

The SGS-THOMSON 5x86 family represents a new generation of x86-compatible 64-bit microprocessors with fifth-generation features. The Branch Target Buffer provides branch prediction with accuracy averaging 80%. The decoupled Load/Store unit allows multiple instructions in a single clock cycle. Other features include single-cycle execution, single-cycle instruction decode, 16-KByte Write-Back cache, and clock rates up to 120 MHz made possible by the use of advanced process technologies and superpipelining. The 100-MHz core speed option can operate with a bus speed of either 33 MHz or 50 MHz. The 120-MHz core speed option operates with a bus speed of 40 MHz.

The 5x86 CPU operates from a 3.45-volt power supply, resulting in lower power consumption at all clock frequencies. Where additional power savings are required (especially in portable applications), designers can make use of suspend mode, stop clock capability, and System Management Mode (SMM).

#### 1.1 Major Functional Blocks

The 5x86 CPU is divided into major functional blocks as shown in the overall block diagram on the first page of this manual.

- Integer Unit

- Floating Point Unit

- Write-Back Cache

- Memory Management Unit

- Bus Interface Unit

The Integer Unit consists of the

- Instruction Buffer

- Instruction Fetch Unit

- Instruction Decoder and Issue Unit.

Instructions are executed in the integer unit and in the floating point unit. The cache unit stores the most recently used data and instructions and provides fast access to this information for the integer and floating point units.

When external memory access is required, the physical address is calculated by the Memory Management Unit and then passed to the Bus Interface Unit, which provides the interface between the external system board and the processor's internal execution and cache units. Figure 1.1. Integer-Unit Pipeline

# 1.2 INTEGER UNIT

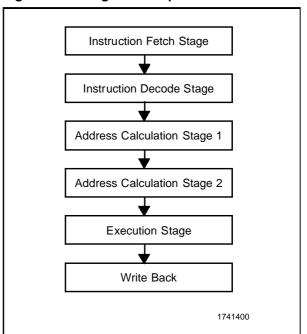

The superpipelined Integer Unit fetches, decodes, and executes x86 instructions through the use of a 6-stage integer pipeline (Figure 1.1.).

#### 1.2.1 Pipeline Stages

The **Instruction Fetch** pipe stage generates from the on-chip cache, a continuous, high-speed instruction stream for use by the processor. Up to 128 bits of code are read during a single clock cycle.

Branch prediction logic, within the prefetch unit, generates a predicted target address for unconditional or conditional branch instructions. When a branch instruction is detected, the instruction fetch stage starts loading instructions at the predicted address within a single clock cycle. Up to 48 bytes of code are queued prior to the Instruction Decode stage.

The **Instruction Decode** stage evaluates the code stream provided by the instruction fetch stage and determines the number of bytes in each instruction and the instruction type. Instructions are processed and decoded at a maximum rate of one instruction per clock.

The **Address Calculation** function is superpipelined and contains two stages, AC1 and AC2. If the instruction refers to a memory operand, the AC1 calculates a linear memory address for the instruction.

The AC2 stage performs any required memory management functions, cache accesses and reg-

ister file accesses. If a floating point instruction is detected by AC2, the instruction is sent to the floating point unit for processing.

The **Execution** stage, under control of microcode, executes instructions using the operands provided by the address calculation stage.

Write-Back, the last stage of the integer unit, updates the register file within the integer unit or writes to the load/store unit within the memory management unit.

#### 1.2.2 Branch Control

Branch instructions occur, on average, every five instructions in x86-compatible programs. When the normal sequential flow of a program changes due to a branch instruction, the pipeline stages may stall because they are waiting for the CPU to calculate or retrieve and decode the new instruction stream. The 5x86 CPU minimizes the performance impact and latency of branch instructions by using branch prediction.

#### 1.2.3 Branch Prediction

The 5x86 CPU uses a Branch Target Buffer (BTB) to store branch target addresses and branch prediction information. During the fetch stage, the instruction stream is checked for the presence of branch instructions. If an unconditional branch instruction is encountered, the 5x86 processor accesses the BTB to check for the branch instruction hits in the BTB, the 5x86 CPU begins fetching at the target address specified by the BTB.

In the case of conditional branches, the BTB also provides history information to indicate whether the branch is more likely to be taken or not taken. If the conditional branch instruction hits in the BTB, the 5x86 CPU begins fetching instructions at the predicted target address. The decision to fetch the taken or not taken target address is based on a four-state branch prediction algorithm that achieves approximately 80% prediction accuracy. If the conditional branch misses in the BTB, the 5x86 processor predicts whether the branch will be taken or not-taken based on the opcode of the instruction.

Once fetched, a conditional branch instruction is decoded and then dispatched to the pipeline. The conditional branch instruction continues through the pipeline and is resolved in the EX stage.

Correctly predicted branch instructions execute in a single clock. If resolution of a branch indicates that a misprediction has occurred, the 5x86 CPU flushes the pipeline and starts fetching from the correct target address. Although the branch is resolved in the EX stage, the misprediction latency is five clock cycles. If a conditional branch misses in the BTB, the 5x86 CPU prefetches both the predicted path and the non-predicted path for each conditional branch, eliminating the cache access cycle on a misprediction.

Since the target address of a return (RET) instruction is dynamic rather than static, the 5x86 processor caches the target addresses for RET instructions in a return stack rather than in the BTB. The return address is pushed on the return stack during a CALL instruction and popped during the corresponding RET instruction.

#### 1.3 Write-Back Cache

The 16-KByte write-back unified cache is a data/instruction cache and is configured as four-way set associative. The cache stores up to 16 KBytes of code and data in 1024 cache lines.

#### 1.4 Memory Management Unit

The memory management unit translates the linear address supplied by the integer unit into a physical address to be used by the cache unit and the bus interface. Memory management procedures are x86-compatible, adhering to standard paging mechanisms.

The memory management unit also contains a load/store unit that is responsible for scheduling cache and external memory accesses. The load/store unit incorporates two performance-enhancing features:

#### Load Store reordering

- prioritizes memory reads required by the integer unit over writes to external memory

- Memory-read bypassing

- eliminates unnecessary memory reads by using valid data still in the execution unit.

#### 1.5 Floating Point Unit

The 5x86 processor floating point unit interfaces to the integer unit and the cache unit through a 64-bit bus. The 5x86 CPU FPU is x87-instruction-set compatible and adheres to the IEEE-754 standard. Because most applications contain FPU instructions mixed with integer instructions, the 5x86 FPU achieves high performance by completing integer and FPU operations in parallel.

FPU instructions are dispatched to the pipeline within the integer unit. The address calculation stage of the pipeline checks for memory management exceptions and accesses memory operands for use by the FPU. Once the instructions and operands have been provided to the FPU, the FPU completes instruction execution independently of the integer unit.

#### 1.6 Bus Interface Unit

The Bus Interface Unit provides the signals and timing required by external circuitry. The signal descriptions and bus interface timing information is provided in Chapter 3 and Chapter 4 of the data book.

#### **1.7 Configuration Registers**

The 5x86 CPU provides four 8-bit Configuration Control Registers (CCR1, CCR2, CCR3 and CCR4) that include control for the on-chip write-back cache, and SMM features. The CPU also provides a Power Management Control Register (PMR), two 8-bit internal read-only device identification registers (DIR0 and DIR1), one 24-bit SMM Address Region Register (SMAR), and an 8 bit Performance Control Register PCR0. The CCR, PMR, DIR, PCR0, and SMAR registers exist in I/O memory space and are selected by a "register index" number as listed in Table 1.1. (Page 5).

Access to these registers is achieved by writing the index of the register to I/O port 22h. I/O port 23h is then used for data transfer. Each I/O port 23h data transfer must be preceded by an I/O port 22h register index selection, otherwise the second and later I/O port 23h operations are directed off-chip and produce external I/O cycles. If the register index number is outside the C0h-CFh, FEh-FFh range, external I/O cycles will also occur.

If the MAPEN field in CCR3 is set to 0001, then access can be made to the CCR4, PCR0, and PMR registers. Otherwise, external I/O cycles will occur if the register index number is outside the range C0-CFh, FEh, FFh. The MAPEN field must remain 0 during normal operation to allow system registers located at port 22h to be accessed.

| REGIST<br>and INE                     |      | MAPEN | 7        | 6         | 5      | 4      | 3         | 2       | 1        | 0        |

|---------------------------------------|------|-------|----------|-----------|--------|--------|-----------|---------|----------|----------|

| Perfor-<br>mance<br>Control<br>[PCR0] | 20h* | 1h    | LSSER    |           |        |        |           | LOOP_EN | BTB_EN   | RSTK_EN  |

| Control 1<br>[CCR1]                   | C1h  | xh    |          |           |        |        | MMAC      | SMAC    | USE_SMI  |          |

| Control 2<br>[CCR2]                   | C2h  | xh    | USE_SUSP | BWRT      |        | WT1    | SUSP_HALT | LOCK_NW | USE_WBAK |          |

| Control 3<br>[CCR3]                   | C3h  | xh    | MAPEN3   | MAPEN2    | MAPEN1 | MAPEN0 | SMM_MODE  | LINBRST | NMI_EN   | SMI_LOCK |

| Control 4<br>[CCR4]                   | E8h* | 1h    |          |           |        | DTE_EN | MEM_BYP   | IORT2   | IORT1    | IORT0    |

| SMM<br>Address<br>[SMAR0]             | CDh  | xh    | A31      | A30       | A29    | A28    | A27       | A26     | A25      | A24      |

| SMM<br>Address<br>[SMAR1]             | CEh  | xh    | A23      | A22       | A21    | A20    | A19       | A18     | A17      | A16      |

| SMM<br>Address<br>[SMAR2]             | CFh  | xh    | A15      | A14       | A13    | A12    | S1ZE3     | SIZE2   | SIZE1    | SIZE0    |

| Power<br>Manage-<br>ment<br>[PMR]     | F0h* | 1h    |          |           |        |        |           | HLF_CLK | CLK1     | CLK0     |

| Device<br>ID0<br>[DIR0]               | FEh  | xh    |          | DEVICE_ID |        |        |           |         |          |          |

| Device<br>ID1<br>[DIR1]               | FFh  | xh    | SID3     | SID2      | SID1   | SID0   | RID3      | RID2    | RID1     | RID0     |

Table 1.1. Configuration Registration Set

**Note:** The following register index numbers are reserved for future use: C0h through CFh and FEh, FFh. **\*Note:** MAPEN must be set to access these registers.

| Figure 1.2. | Performa | nce Cor | ntrol Re | gister 0 | (PCR0)  |        |         |      |  |

|-------------|----------|---------|----------|----------|---------|--------|---------|------|--|

| 7           | 6        | 5       | 4        | 3        | 2       | 1      | 0       |      |  |

| LSSER       |          |         |          |          | LOOP_EN | BTB_EN | RSTK_EN | PCRO |  |

| REGISTER    |          | = 20h   |          |          |         |        |         |      |  |

#### 1.2 Dorfe ntrol Dogista ----~

# Table 1.2. PCR0 Bit Definitions

| BIT<br>POSITION | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | RSTK_EN | Return Stack Enable.<br>If = 1: the Return Stack is enabled and RET instructions will speculatively execute the<br>code following the associated CALL to improve performance.<br>If = 0: the Return Stack is not enabled and optimum performance will not be achieved.                                                                                                                                                                                                                                                                                        |

| 1               | BTB_EN  | Branch Target Buffer enable.<br>If = 1: the Branch Target Buffer is enabled and branch prediction occurs.<br>If = 0: no branch prediction will occur.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2               | LOOP_EN | Loop Enable.<br>If = 1: the CPU will not flush the prefetch buffer if the destination of a jump is already present in the prefetch buffer. This eliminates the need for a read from the cache and thus improves performance.                                                                                                                                                                                                                                                                                                                                  |

| 3-6             |         | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7               | LSSER   | Load Store Serialize Enable (Reorder Disable).<br>If = 1: all memory reads and writes will occur in execution order (load store serializing<br>enabled, reordering disabled).<br>If = 0: memory reads and writes can be reordered for optimum performance (load store<br>serializing disabled, reordering enabled). Memory accesses in the address range 640K<br>to 1M will always be issued in execution order.<br>LSSER should be set to ensure that memory-mapped I/O devices operating outside of<br>the address range 640K to 1M will operate correctly. |

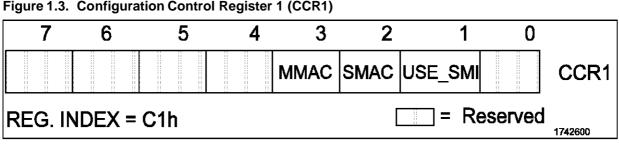

# Figure 1.3. Configuration Control Register 1 (CCR1)

# Table 1.3. CCR1 Bit Definitions

| BIT<br>POSITION | NAME    | DESCRIPTION                                                                                                                                                                                                                |

|-----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1*              | USE_SMI | Enable SMM Pins<br>If = 1: SMI# input/output pin and SMADS# output pin are enabled.<br>If = 0: SMI# input pin ignored and SMADS# output pin floats.                                                                        |

| 2*              | SMAC    | System Management Memory Access<br>If = 1: Any access to addresses within the SMM memory space cause external bus<br>cycles to be issued with SMADS# output active. SMI# input is ignored.<br>If = 0: No effect on access. |

| 3*              | MMAC    | Main Memory Access<br>If = 1: All data accesses which occur within an SMI service routine (or when SMAC = 1)<br>access main memory instead of SMM memory space.<br>If = 0: No effect on access.                            |

Note: Bits 0, 4-7 are reserved. Bits 1-3 are cleared to 0 at reset.

\*Note: Access enabled by CCR3, bit 0, SMI-Lock bit.

| Figure 1.4. | Conngura | ation Com | ITOI Reg | Jister Z (CCRZ | )       |           |   |         |

|-------------|----------|-----------|----------|----------------|---------|-----------|---|---------|

| 7           | 6        | 5         | 4        | 3              | 2       | 1         | 0 |         |

| USE_SUSP    | BWRT     |           | WT1      | SUSP_HALT      | LOCK_NW | USE_WBAK  |   | CCR2    |

| REGIST      | er ind   | DEX = C   | 2h       |                |         | = Reserve | d | 1742700 |

# Figure 1.4. Configuration Control Register 2 (CCR2)

# Table 1.4. CCR2 Bit Definitions

| BIT<br>POSITION | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |

|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | USE_WBAK  | Enable Write-Back Cache Interface Pins<br>If = 1: Enable INVAL and WM_RST input pins, CACHE#, and HITM# output pins.<br>When enabling write-back cache mode, the USE_WBAK bit must be set prior to set-<br>ting the NW bit in CR0.<br>If = 0: INVAL and WM_RST input pins are ignored, and CACHE# and HITM# output<br>pins float. |

| 2               | LOCK_NW   | LOCK NW Bit<br>If = 1: Prohibits changing the state of the NW bit in CR0.                                                                                                                                                                                                                                                         |

| 3               | SUSP_HALT | Suspend on HALT<br>If = 1: CPU enters suspend mode following execution of a HALT instruction.                                                                                                                                                                                                                                     |

| 4               | WT1       | Write-Through Region 1<br>If = 1: Forces all writes to the address region between 640 KBytes to 1 MByte that hit<br>in the on-chip cache to be issued on the external bus.                                                                                                                                                        |

| 6               | BWRT      | Enable Burst Write Cycles<br>If = 1: Enables use of 16-byte burst write-back cycles.                                                                                                                                                                                                                                              |

| 7               | USE_SUSP  | Enable Suspend Pins<br>If = 1: SUSP# input and SUSPA# output are enabled.<br>If = 0: SUSP# input is ignored and SUSPA# output floats.                                                                                                                                                                                             |

Note: Bits 0 and 5 are reserved. Bits 1-4, 6 and 7 are cleared to 0 at reset.

| 7                    |        |        |        |          |         |        |          |      |

|----------------------|--------|--------|--------|----------|---------|--------|----------|------|

| <u> </u>             | 6      | 5      | 4      | 3        | 2       | 1      | 0        |      |

| MAPEN3               | MAPEN2 | MAPEN1 | MAPEN0 | SMM_MODE | LINBRST | NMI_EN | SMI_LOCK | CCR3 |

| REGISTER INDEX = C3h |        |        |        |          |         |        |          |      |

Figure 1.5. Configuration Control Register 3 (CCR3)

# Table 1.5. CCR3 Bit Definitions

| BIT<br>POSITION | NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

|-----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | SMI_LOCK   | SMM Register Lock         If = 1: the following SMM control bits can not be modified:         CCR1 bits: 1, 2, and 3         CCR3 bit: 1         all SMAR bits.         However, while operating within a SMI handler these SMM control bits can be modified.         Once set, the SMI_LOCK bit can only be cleared by asserting the RESET pin. |

| 1*              | NMI_EN     | NMI Enable<br>If = 1: NMI is enabled during SMM.<br>If = 0: NMI is not recognized during SMM.                                                                                                                                                                                                                                                    |

| 2               | LINBRST    | Linear Address Burst Cycles<br>If = 1: linear address sequence is used while performing burst cycles.<br>If = 0: "1+4" address sequencing is used while performing burst cycles.                                                                                                                                                                 |

| 3*              | SMM_MODE   | SMM Mode<br>If = 1: SMM pins function as defined for SL-compatible mode.<br>If = 0: SMM pins function as defined for standard Cyrix SMM mode.                                                                                                                                                                                                    |

| 4-7             | MAPEN[3-0] | MAP Enable<br>If = 1h: all configuration registers are accessible. All accesses to port 22h are trapped.<br>If = 0h: only configuration registers C0h through CFh, FEh and FFh are accessible.                                                                                                                                                   |

Note: Bits 0-7 are cleared to zero at reset. \*Note: Access defined by CCR3, bit 0, SMI-Lock bit.

| Figure 1.6. | Configura | tion Contr | ol Registe | er 4 (CCR4) |     |         |         |

|-------------|-----------|------------|------------|-------------|-----|---------|---------|

| 7           | 6         | 5          | 4          | 3           | 2   | 1       | 0       |

|             |           | C          | TE_EN      | MEM_BYP     | IOF | RT[2-0] | CCR4    |

| REGIST      | ER IND    | EX = E8    | Bh         |             |     | ]= Rese | 1742900 |

# Table 1.6. CCR4 Bit Definitions

| BIT<br>POSITION | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                             |

|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-0             | IORT[2-0] | I/O Recovery Time<br>Specifies the minimum number of bus clocks between I/O accesses:<br>Oh = no clock delay<br>1h = 2-clock delay<br>2h = 4-clock delay<br>3h = 8-clock delay<br>4h = 16-clock delay<br>5h = 32-clock delay (default value after RESET)<br>6h = 64-clock delay<br>7h = 128-clock delay |

| 3               | MEM_BYP   | If = 1: Memory read bypassing is enabled.<br>If = 0: Memory read bypassing is disabled.                                                                                                                                                                                                                 |

| 4               | DTE_EN    | Enable Directory Table Entry Cache<br>If = 1: the Directory Table Entry cache is enabled.<br>If = 0: the Directory Table Entry cache is disabled.                                                                                                                                                       |

Note: Bits 0-4 are cleared to zero at reset, bits 5-7 are reserved.

| 7     | 6       | 5       | 4 | 3 | 2       | 1        | 0   |     |

|-------|---------|---------|---|---|---------|----------|-----|-----|

|       |         |         |   | F | ILF_CLK | CLK[1-0] |     | PMR |

| REGIS | ter ind | EX = F0 | า |   | = F     | Reserved | 000 |     |

Figure 1.7. Power Management Register (PMR)

# Table 1.7. PMR Bit Definitions

| BIT<br>POSITION | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1-0             | CLK[1-0] | Core Clock/Bus Clock Ratio<br>If = 0h: ratio = 1/1<br>If = 1h: ratio = 2/1 (default power-up for CLKMUL pin = 0)<br>If = 2h: ratio = reserved<br>If = 3h: ratio = 3/1 (default power-up for CLKMUL pin = 1)<br>At reset, the CLK[1-0] bits are initialized to 1h if CLKMUL = 0, or to 3h if CLKMUL = 1.<br>After reset is completed, CLK[1-0] bits may be set to 0h in order to obtain lower power<br>consumption. The default power-up value must be restored when peak CPU perfor-<br>mance is required. |  |  |  |  |  |

| 2               | HLF_CLK  | Half Speed Clock<br>If = 1: the CPU core operates at half the speed of the external bus clock regardless of<br>the CLK[1-0] bits except during external bus transfers. When an external bus transfer<br>occurs, the core clock frequency automatically increases in frequency for the duration<br>of the transfer. When the transfer is complete, the core returns to half the frequency of<br>the bus.                                                                                                    |  |  |  |  |  |

Note: Bit 2 is cleared to zero at reset, bits 3-7 are reserved.

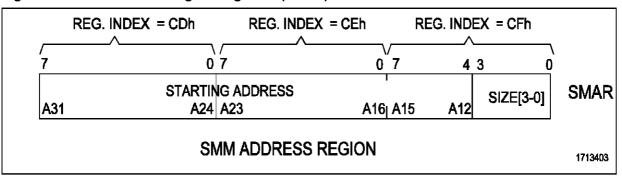

#### Figure 1.8. SMM Address Region Registers (SMAR)

**Note:** The SMAR register is accessed as three unique registers using separate register indices CDh, CEh, and CFh. **Note:** Access to the SMAR register is enabled by CCR3 bit 0, SMI\_LOCK bit.

| SIZE (3-0) | BLOCK SIZE | SIZE (3-0) | BLOCK SIZE            |

|------------|------------|------------|-----------------------|

| Oh         | Disabled   | 8h         | 512 KBytes            |

| 1h         | 4 KBytes   | 9h         | 1 MBytes              |

| 2h         | 8 KBytes   | Ah         | 2 MBytes              |

| 3h         | 16 KBytes  | Bh         | 4 MBytes              |

| 4h         | 32 KBytes  | Ch         | 8 MBytes              |

| 5h         | 64 KBytes  | Dh         | 16 MBytes             |

| 6h         | 128 KBytes | Eh         | 32 MBytes             |

| 7h         | 256 KBytes | Fh         | 4 KBytes (same as 1h) |

#### Table 1.8. SMAR-SIZE Field Bit Definitions

| Figure 1.9. | <b>Device Identification</b> | Register 0 | DIR0) |

|-------------|------------------------------|------------|-------|

|             |                              |            |       |

| 7                    | 6              | 5 | 4 | 3 | 2 | 1 | 0       |      |

|----------------------|----------------|---|---|---|---|---|---------|------|

|                      | DEVICE_ID[7-0] |   |   |   |   |   |         | DIR0 |

| REGISTER INDEX = FEh |                |   |   |   |   |   | 1723900 |      |

# Table 1.9. DIR0 Bit 0 Definitions

| BIT<br>POSITION | NAME           | DESCRIPTION                                   |  |

|-----------------|----------------|-----------------------------------------------|--|

| 7 - 0           | DEVICE_ID[7-0] | CPU Device Identification Number (read only). |  |

| i igure i i iu. | Devide fac | minoation | riogiotoi |              |   |   |   |      |

|-----------------|------------|-----------|-----------|--------------|---|---|---|------|

| 7               | 6          | 5         | 4         | 3            | 2 | 1 | 0 |      |

|                 | SID[       | [3-0]     |           | RID[3-0] DIF |   |   |   | DIR1 |

| REGIS           |            | IDEX =    | FFh       | 1723800      |   |   |   | D    |

# Figure 1.10. Device Identification Register 1 (DIR1)

# Table 1.10. DIR1 Bit Definitions

| BIT<br>POSITION | NAME     | DESCRIPTION                                                                             |

|-----------------|----------|-----------------------------------------------------------------------------------------|

| 3-0             | RID[3-0] | Revision Identification:<br>RID[3-0] are read only and indicate device revision number. |

| 7-4             | SID[3-0] | Stepping Identification:<br>SID[3-0] are read only and indicate device stepping number. |

# 2.0 ELECTRICAL SPECIFICATIONS

This section provides information on electrical connections, absolute maximum ratings, recommended operating conditions, and DC characteristics, and AC characteristics. All voltage values in Electrical Specifications are with respect to  $V_{\rm SS}$  unless otherwise noted.

#### 2.1 Electrical Connections

#### 2.1.1 Power and Ground Connections and Decoupling

Testing and operating the 5x86 CPU requires the use of standard high frequency techniques to reduce parasitic effects. These effects can be minimized by filtering the DC power leads with low-inductance decoupling capacitors, using low impedance wiring, and by utilizing all of the  $V_{CC}$  and GND pins.

#### 2.2 Pull-Up/Pull-Down Resistors

Table 2.1. lists the input pins that are internally connected to pull-up and pull-down resistors. When unused, these inputs do not require connection to external pull-up or pull-down resistors. The SUSP# pin is unique in that it is connected to a pull-up resistor only when SUSP# is not asserted. CLKMUL should not be connected to a switching signal.

| Table 2.1. Pins | Connected to Internal Pull-Up |

|-----------------|-------------------------------|

| and Pull-Down   | Resistors                     |

| SIGNAL | RESISTOR                |

|--------|-------------------------|

| A20M#  | 20-k $\Omega$ pull-up   |

| AHOLD  | 20-k $\Omega$ pull-down |

| BOFF#  | 20-k $\Omega$ pull-up   |

| BS16#  | 20-kΩ pull-up           |

| BS8#   | 20-kΩ pull-up           |

| BRDY#  | 20-k $\Omega$ pull-up   |

| CLKMUL | 20-kΩ pull-up           |

| EADS#  | 20-k $\Omega$ pull-up   |

| FLUSH# | 20-k $\Omega$ pull-up   |

| IGNNE# | 20-k $\Omega$ pull-up   |

| INVAL  | 20-kΩ pull-up           |

| KEN#   | 20-kΩ pull-up           |

| RDY#   | 20-kΩ pull-up           |

| SUSP#  | 20-kΩ pull-up           |

| UP#    | 20-kΩ pull-up           |

| WM_RST | 20-k $\Omega$ pull-down |

It is recommended that the ADS#, LOCK# and SMI# output pins be connected to pull-up resistors, as indicated in Table 2.2. The external pull-ups guarantee that the signals remain high (inactive) during hold acknowledge states.

# Table 2.2. Pins Requiring External Pull-UpResistors

| SIGNAL | EXTERNAL RESISTOR     |

|--------|-----------------------|

| ADS#   | 20-k $\Omega$ pull-up |

| LOCK#  | 20-k $\Omega$ pull-up |

| SMI#   | 20-kΩ pull-up         |

#### 2.2.2 Unused Input Pins

All inputs not used by the system designer and not listed in Table 2.1. (Page 15) should be kept at either ground or V<sub>CC</sub>. To prevent possible spurious operation, connect active-high inputs to ground through a 20-k $\Omega$  (± 10%) pull-down resistor and active-low inputs to V<sub>CC</sub> through a 20-k $\Omega$  (± 10%) pull-up resistor.

#### 2.2.3 NC Designated Pins

Pins designated NC should be left disconnected. Connecting an NC pin to a pull-up resistor, pull-down resistor, or an active signal could cause unexpected results and possible circuit malfunctions.

Table 2.3.

Absolute Maximum Ratings

#### 2.3 Absolute Maximum Ratings

Table 2.3. lists absolute maximum ratings for the 5x86 microprocessors. Stresses beyond the listed ratings may cause permanent damage to the device. Exposure to conditions beyond these limits may (1) reduce device reliability and (2) result in premature failure even when there is no immediately apparent sign of failure. Prolonged exposure to conditions at or near the absolute maximum ratings may also result in reduced useful life and reliability. These are stress ratings only and do not imply that operation under any conditions other than those listed under "Recommended Operating Conditions" Table 2.4. (Page 17) is possible.

| PARAMETER                             | ALL 5x86 CPUs |     | UNITS | NOTES         |  |

|---------------------------------------|---------------|-----|-------|---------------|--|

| FARAMETER                             | MIN           | MAX |       |               |  |

| Operating Case Temperature            | -65           | 110 | °C    | Power Applied |  |

| Storage Temperature                   | -65           | 150 | °C    | No Bias       |  |

| Supply Voltage, V <sub>CC</sub>       | -0.5          | 4.0 | V     |               |  |

| Voltage On Any Pin                    | -0.5          | 6.0 | V     |               |  |

| Input Clamp Current, IIK              |               | 10  | mA    | Power Applied |  |

| Output Clamp Current, I <sub>OK</sub> |               | 25  | mA    | Power Applied |  |

# 2.4 Recommended Operating Conditions

Table 2.4. lists the recommended operating conditions for the 5x86 CPU.

Table 2.4. Recommended Operating Conditions

| PARAMETER                                                                          | ALL 5x86 CPUs |            | UNITS | NOTES                                |

|------------------------------------------------------------------------------------|---------------|------------|-------|--------------------------------------|

| PARAMETER                                                                          | MIN           | МАХ        |       | NOTES                                |

| T <sub>C</sub> Operating Case Temperature                                          | 0             | 85         | °C    |                                      |

| V <sub>CC</sub> Supply Voltage                                                     | 3.3           | 3.6        | V     |                                      |

| V <sub>IH</sub> High-Level Input Voltage                                           | 2.0           | 5.5        | V     |                                      |

| V <sub>IL</sub> Low-Level Input Voltage<br>All Inputs Except CLK<br>CLK Input Only | -0.3<br>-0.3  | 0.6<br>0.5 | v     |                                      |

| I <sub>OH</sub> High-Level Output Current                                          |               | -2.0       | mA    | V <sub>O</sub> =V <sub>OH(MIN)</sub> |

| I <sub>OL</sub> Low-Level Output Current                                           |               | 5.0        | mA    | V <sub>O</sub> =V <sub>OL(MAX}</sub> |

## 2.5 DC Characteristics

#### Table 2.5. DC Characteristics (at Recommended Operating Conditions)

| PARAMETER                                                                                                                                                                        | ALL 5x8          | 86 CPUs    |    | NOTES                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|----|-----------------------------------------------------------|

| PARAMETER                                                                                                                                                                        | MIN              | МАХ        |    | NOTES                                                     |

| V <sub>OL</sub> Output Low Voltage                                                                                                                                               |                  | 0.45       | V  | I <sub>OL</sub> = 5 mA                                    |

| V <sub>OH</sub> Output High Voltage                                                                                                                                              | 2.4              |            | V  | I <sub>OH</sub> = -2 mA                                   |

| I Input Leakage Current for all pins<br>except those with internal pull-ups or<br>pull-downs                                                                                     |                  | ±15        | μΑ | 0 < V <sub>IN</sub> < V <sub>CC</sub> ,<br>See Table 2.1. |

| I <sub>IH</sub> Input Leakage Current for all pins with internal pull-downs.                                                                                                     |                  | 200        | μΑ | V <sub>IH</sub> = 2.4 V,<br>See Table 2.1.                |

| I <sub>IL</sub> Input Leakage Current for all pins with<br>internal pull-ups.                                                                                                    |                  | -400       | μΑ | V <sub>IL</sub> = 0.45 V,<br>See Table 2.1.               |

| $\begin{array}{ll} I_{CC} & \mbox{Active } I_{CC} \\ 5x86\mbox{-}100 \mbox{ at } f_{CLK} = 100 \mbox{ MHz} \\ 5x86\mbox{-}120 \mbox{ at } f_{CLK} = 120 \mbox{ MHz} \end{array}$ | 0.9TYP<br>1.0TYP | 1.2<br>1.4 | A  | Note 1                                                    |

| $I_{CCSM}$ Suspend Mode $I_{CC}$<br>5x86-100 at $f_{CLK}$ = 100 MHz<br>5x86-120 at $f_{CLK}$ = 120 MHz                                                                           | 20 TYP<br>50 TYP | 75<br>75   | μΑ | Notes 1, 3                                                |

| I <sub>CCSS</sub> Standby I <sub>CC</sub> (Suspended and CLK<br>Stopped)                                                                                                         | 15 TYP           | 60         | μΑ | f <sub>CLK</sub> = 0 MHz, Note 4                          |

| C <sub>IN</sub> Input Capacitance                                                                                                                                                |                  | 20         | pF | f = 1 MHz, Note 2                                         |

| C <sub>OUT</sub> Output or I/O Capacitance                                                                                                                                       |                  | 20         | pF | f = 1 MHz, Note 2                                         |

| C <sub>CLK</sub> CLK Capacitance                                                                                                                                                 |                  | 20         | pF | f = 1 MHz, Note 2                                         |

Notes: 1. f<sub>CLK</sub> ratings refer to internal clock frequency. 2. Not 100% tested.

All inputs are at 0.4 or V<sub>CC</sub> - 0.4 (CMOS levels). All inputs held are static except clock and all outputs are unloaded (static I<sub>OUT</sub> = 0 mA). This specification is also valid for UP# = 0.

All inputs are at 0.4 or V<sub>CC</sub> - 0.4 (CMOS levels). All inputs are held static and all outputs are unloaded (static I<sub>OUT</sub> = 0 mA).

#### 2.6 AC Characteristics

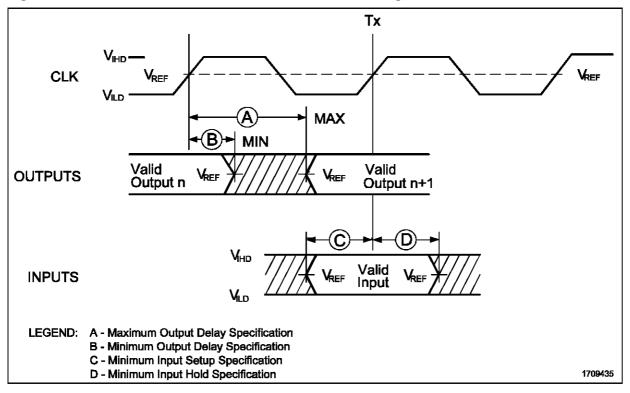

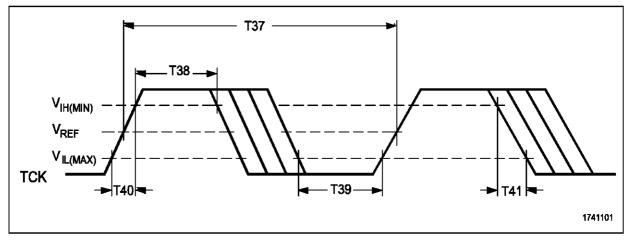

Table 2.6. (Page 19) through Table 2.12. (Page 25) list the AC characteristics including output delays, input setup requirements, input hold requirements and output float delays. These measurements are based on the measurement points identified in Figure 2.1. (Page 20) and Figure 2.2. (Page 21). The rising-clock-edge reference level  $V_{\mathsf{REF}}$  and other reference levels are shown in

Table 2.6. below. Input or output signals must cross these levels during testing.

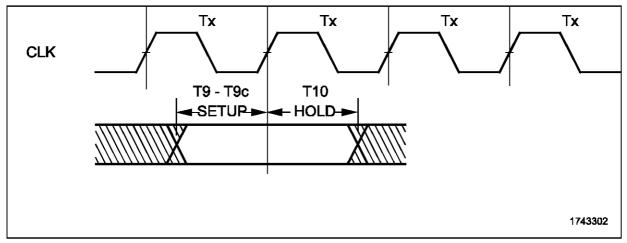

Figure 2.1. shows output delay (A and B) and input setup and hold times (C and D). Input setup and hold times are specified minimums, defining the smallest acceptable sampling window a synchronous input signal must be stable for correct operation.

| Table 2.6. | <b>Drive Level and Measurement</b> |  |

|------------|------------------------------------|--|

| Points for | Switching Characteristics          |  |

| SYMBOL           | VOLTAGE<br>(Volts) |

|------------------|--------------------|

| V <sub>REF</sub> | 1.5                |

| V <sub>IHD</sub> | 2.3                |

| V <sub>ILD</sub> | 0                  |

Note: Refer to Figure 2.1.

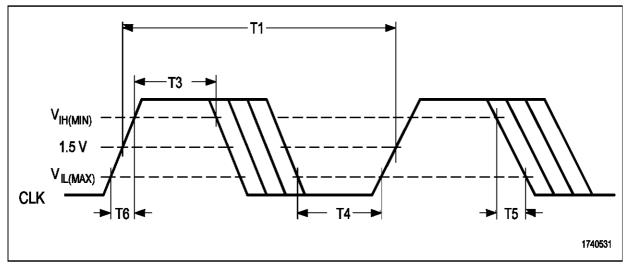

|    | PARAMETER            |     | 6-100<br>Iz BUS |     | 6-120<br>Iz BUS |     | 6-100<br>Iz BUS | UNITS | NOTES      |

|----|----------------------|-----|-----------------|-----|-----------------|-----|-----------------|-------|------------|

|    |                      | MIN | MAX             | MIN | МАХ             | MIN | MAX             |       |            |

|    | CLK Frequency        |     | 33              |     | 40              |     | 50              | MHz   |            |

| T1 | CLK Period           | 30  |                 | 25  |                 | 20  |                 | ns    |            |

| T2 | CLK Period Stability |     | ± 250           |     | ± 250           |     | ± 250           | ps    |            |

| Т3 | CLK High Time        | 11  |                 | 9   |                 | 7   |                 | ns    | At 2 V     |

| T4 | CLK Low Time         | 11  |                 | 9   |                 | 7   |                 | ns    | 0.5 V      |

| T5 | CLK Fall Time        |     | 3               |     | 3               |     | 2               | ns    | 2 to 0.5 V |

| Т6 | CLK Rise Time        |     | 3               |     | 3               |     | 2               | ns    | 0.5 to 2 V |

Table 2.7. Clock Specifications Tcase = 0 to 85 °C (See Figure 2.2.)

Figure 2.2. CLK Timing and Measurement Points

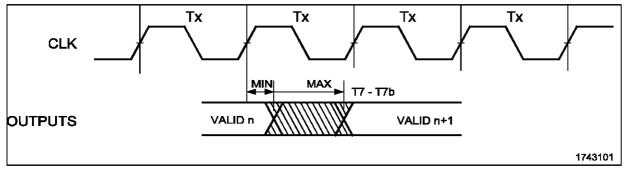

|     | PARAMETER                           |     | 6-100<br>Iz BUS |     | 6-120<br>Iz BUS | 5x86<br>50-MH |      | UNITS |

|-----|-------------------------------------|-----|-----------------|-----|-----------------|---------------|------|-------|

|     |                                     | MIN | МАХ             | MIN | МАХ             | MIN           | МАХ  |       |

| T7  | All output signals not listed below | 3   | 14              | 3   | 14              | 2             | 12   | ns    |

| T7a | D31 - D0, DP3 - DP0                 | 3   | 14              | 3   | 14              | 3             | 12   | ns    |

| T7b | A19 - A2                            | 3   | 14              | 3   | 14              | 2             | 10.5 | ns    |

Table 2.8. Output Valid Delays CL = 50 pF, Tcase = 0 to 85 °C (See Figure 2.3.)

# Figure 2.3. Output Valid Delay Timing

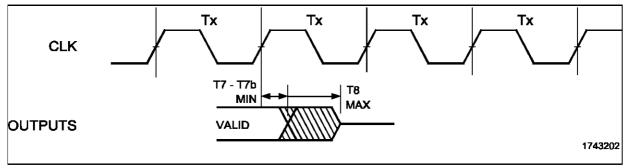

|    | PARAMETER           | 5x86<br>33-MH |     | 5x86<br>40-MH |     | 5x86<br>50-MH | UNITS |    |

|----|---------------------|---------------|-----|---------------|-----|---------------|-------|----|

|    |                     | MIN           | МАХ | MIN           | MAX | MIN           | МАХ   |    |

| T8 | All output signals. |               | 20  |               | 19  |               | 18    | ns |

# Table 2.9. Output Float Delays CL = 50 pF, Tcase = 0 to 85 °C (See Figure 2.4.)

Figure 2.4. Output Float Delay Timing

|     | PARAMETER                        | 5x86-100<br>33-MHz BUS | 5x86-120<br>40-MHz BUS | 5x86-100<br>50-MHz BUS | UNITS |

|-----|----------------------------------|------------------------|------------------------|------------------------|-------|

|     |                                  | MIN                    | MIN                    | MIN                    |       |

| Т9  | All inputs not listed below      | 5                      | 5                      | 5                      | ns    |

| T9a | HOLD, AHOLD                      | 6                      | 5                      | 5                      | ns    |

| T9b | BOFF#                            | 7                      | 6                      | 5                      | ns    |

| T9c | A31 - A4, D31 - D0,<br>DP3 - DP0 | 5                      | 5                      | 4                      | ns    |

Table 2.10. Input Setup Times Tcase = 0 to 85 °C (See Figure 2.5.)

Table 2.11. Input Hold Times Tcase = 0 to 85 °C (See Figure 2.5.)

|     | PARAMETER  | 5x86-100<br>33-MHz BUS | 5x86-120<br>40 MHz-BUS | 5x86-100<br>50-MHz BUS | UNITS |

|-----|------------|------------------------|------------------------|------------------------|-------|

|     |            | MIN                    | MIN                    | MIN                    |       |

| T10 | All inputs | 3                      | 3                      | 2                      | ns    |

# Figure 2.5. Input Setup and Hold Timing

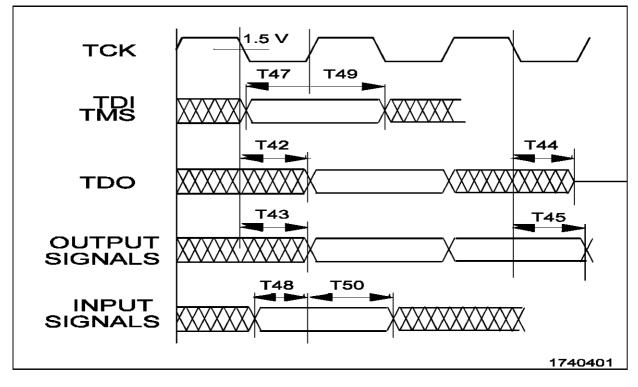

|        | DADAMETER                    | ALL BUS FR | EQUENCIES |       |             |

|--------|------------------------------|------------|-----------|-------|-------------|

| SYMBOL | PARAMETER                    | MIN        | MAX       | UNITS | FIGURE      |

|        | TCK Frequency (MHz)          |            |           | MHz   |             |

| T37    | TCK Period                   | 40         |           | ns    | Figure 2.6. |

| T38    | TCK High Time                | 10         |           | ns    | Figure 2.6. |

| T39    | TCK Low Time                 | 10         |           | ns    | Figure 2.6. |

| T40    | TCK Rise Time                |            | 4         | ns    | Figure 2.6. |

| T41    | TCK Fall Time                |            | 4         | ns    | Figure 2.6. |

| T42    | TDO Valid Delay              | 3          | 25        | ns    | Figure 2.7. |

| T43    | Non-test Outputs Valid Delay | 3          | 25        | ns    | Figure 2.7. |

| T44    | TDO Float Delay              |            | 30        | ns    | Figure 2.7. |

| T45    | Non-test Outputs Float Delay |            | 36        | ns    | Figure 2.7. |

| T47    | TDI, TMS Setup Time          | 8          |           | ns    | Figure 2.7. |

| T48    | Non-test Inputs Setup Time   | 8          |           | ns    | Figure 2.7. |

| T49    | TDI, TMS Hold Time           | 7          |           | ns    | Figure 2.7. |

| T50    | Non-test Inputs Hold Time    | 7          |           | ns    | Figure 2.7. |

Table 2.12. JTAG AC Specifications

Figure 2.6. TCK Timing and Measurement Points

# 3.0 MECHANICAL SPECIFICATIONS

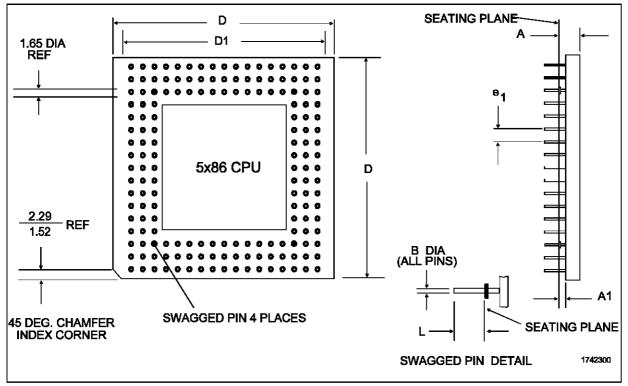

# 3.1 168-Pin PGA Package

The pin assignments for the 5x86V10HS, 5x86V10PS, 5x86V12HS and 5x86V12PS are shown in Figure 3.1. The pins are listed by signal name and pin number in Table 3.1. and Table 3.2. respectively. Dimensions for the 168-pin CPGA package are shown in Figure 3.2. and Table 3.3.

|    | S                      | R               | Q                    | Ρ         | N                 | М           | L         | K           | J         | н        | G          | F          | Е         | D          | С               | В                 | A                    |           |

|----|------------------------|-----------------|----------------------|-----------|-------------------|-------------|-----------|-------------|-----------|----------|------------|------------|-----------|------------|-----------------|-------------------|----------------------|-----------|

| 1  | A27<br>©               | A28<br>©        | <b>A31</b><br>⊚      | D0<br>©   | D2<br>©           | Vss<br>©    | Vss<br>⊚  | Vss<br>©    | NC<br>©   | Vss<br>© | Vss<br>©   | <b>DP1</b> | Vss<br>©  | D9<br>©    | D11<br>©        | D19<br>©          | D20<br>©             | ١         |

| 2  | A26<br>⊚               | A25<br>©        | Vas<br>©             | A29<br>©  | D1<br>©           | Vcc<br>©    | D6<br>()) | Vcc<br>©    | D5<br>©   | D3       | Vcc<br>©   | D8<br>©    | Vcc<br>©  | D13<br>©   | D18<br>©        | D21               | D22<br>©             |           |

| 3  | A23<br>©               | Vcc<br>©        | A17<br>⊚             | A30<br>◎  | DP0<br>⊗          | D4<br>⊚     | D7<br>©   | D14<br>◎    | D16<br>©  | DP2<br>© | D12<br>©   | D15<br>©   | D10<br>©  | D17<br>©   | с∟к<br>⊚        | V58<br>©          | тск<br>⊚             | :         |

| 4  | VOLDET<br>©            | V88<br>©        | A19<br>©             |           |                   |             |           |             |           |          |            |            |           |            | Vcc<br>©        | V\$8<br>©         | D23<br>©             | .         |

| 5  | A14<br>©               | A18<br>◎        | <b>A21</b><br>⊚      |           |                   |             |           |             |           |          |            |            |           |            | Vcc<br>©        | Vss<br>©          | <b>DP3</b><br>©      | 4         |

| 6  | Vss<br>©               | Vcc<br>©        | <b>A24</b><br>⊚      |           |                   |             |           |             |           |          |            |            |           |            | <b>D27</b><br>© | D25<br>©          | D24<br>©             |           |

| 7  | <b>A12</b><br>⊚        | A15<br>©        | <b>A22</b><br>©      |           |                   |             | 5         | <b>x8</b> ( | 6 C       | PL       | J          |            |           |            | D26<br>©        | Vcc<br>©          | Vss<br>©             | 7         |

| 8  | Vss<br>©               | Vcc<br>©        | A20<br>©             |           |                   |             | -         |             |           |          |            |            |           |            | D28<br>©        | D31<br>©          | D29<br>©             | 8         |

| 9  | Vss<br>©               | Vcc<br>©        | A16<br>©             |           |                   |             | 16        | 8-F         | 'n        | PC       | jΑ         |            |           |            | <b>D30</b><br>© | Vcc<br>©          | V59<br>©             | 4         |

| 10 | Vas<br>©               | Vcc<br>©        | A13<br>©             |           |                   |             | (         | Гор         | b V       | 'iev     | V)         |            |           | •          | MM_RST<br>◎     | <b>sm⊯</b><br>⊘   | INVAL<br>©           | 1         |

| 11 | Vss<br>©               | Vcc<br>©        | <b>A9</b><br>©       |           |                   |             |           |             |           |          |            |            |           |            | UP#<br>©        | Vcc<br>©          | <b>V58</b><br>©      | 1         |

| 12 | Vss<br>©               | <b>A11</b><br>⊚ | <b>A5</b><br>⊗       |           |                   |             |           |             |           |          |            |            |           | S          | MADS# C         | CACHE#            | • HI <b>TM#</b><br>© | 1         |

| 13 | A10<br>©               | A8<br>())       | <b>A7</b><br>⊘       |           |                   |             |           |             |           |          |            |            |           |            | NC<br>⊚         | NC<br>©           | SUSPA#               | 1         |

| 14 | Vss<br>©               | Vcc<br>©        | <b>A2</b><br>⊚       |           |                   |             |           |             |           |          |            |            |           | F          | ERR#            | TMS<br>©          | TDI<br>©             | 1         |

| 15 | <b>A6</b><br>©         | A3<br>())       | BREQ<br>©            | HLDA<br>© | LOCK#<br>⊚        | <b>D/C#</b> | PWT<br>◎  | BE0#<br>©   | BE2#<br>© | BRDY#    | SUSP#<br>© | KEN#       | Hold<br>© | A20M#      | FLUSH#<br>©     | NMI<br>©          | ignne#<br>©          | 1         |

| 16 | ۲                      | ۲               | PLOCK#<br>©          | ۲         | <b>M/IO#</b><br>⊚ | Vcc<br>©    | Vcc<br>©  | Vcc<br>©    | BE1#<br>© | Vcc<br>© | Vcc<br>©   | RDY#<br>©  | Vcc<br>©  | 856#<br>©  | RESET<br>©      | <b>TDO</b><br>()) | INTR<br>©            | 1         |

| 7  | ADS# <sup>C</sup><br>⊚ | ©               | • PCH <b>K#</b><br>© | Vss<br>©  | <b>₩/R#</b><br>◎  | Vss<br>©    | Vas<br>©  | Vss<br>©    | PCD<br>©  | Vss<br>© | Vss<br>©   | BE3#<br>◎  | Vss<br>©  | BOFF#<br>© | BS16#<br>⊚      | eads#<br>©        | AHOLD<br>©           | 1         |

| L  | S                      | R               | a                    | P         | N                 | м           | L         | к           | J         | н        | G          | F          | Е         | D          | с               | B                 | A                    | ]<br>174: |

Figure 3.1. 168-Pin PGA Package Pin Assignments

| Signal | Pin |

|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|

| A2     | Q14 | A29    | P2  | D9     | D1  | FERR#  | C14 | TMS    | B14 | VSS    | A11 |

| A3     | R15 | A30    | P3  | D10    | E3  | FLUSH# | C15 | UP#    | C11 | VSS    | В3  |

| A4     | S16 | A31    | Q1  | D11    | C1  | HITM#  | A12 | vcc    | В7  | vss    | B4  |

| A5     | Q12 | ADS#   | S17 | D12    | G3  | HLDA   | P15 | vcc    | В9  | vss    | B5  |

| A6     | S15 | AHOLD  | A17 | D13    | D2  | HOLD   | E15 | vcc    | B11 | vss    | E1  |

| A7     | Q13 | BE0#   | K15 | D14    | КЗ  | IGNNE# | A15 | vcc    | C4  | vss    | E17 |

| A8     | R13 | BE1#   | J16 | D15    | F3  | INTR   | A16 | vcc    | C5  | VSS    | G1  |

| A9     | Q11 | BE2#   | J15 | D16    | J3  | INVAL  | A10 | vcc    | E2  | VSS    | G17 |

| A10    | S13 | BE3#   | F17 | D17    | D3  | KEN#   | F15 | vcc    | E16 | vss    | H1  |

| A11    | R12 | BLAST# | R16 | D18    | C2  | LOCK#  | N15 | vcc    | G2  | vss    | H17 |

| A12    | S7  | BOFF#  | D17 | D19    | B1  | M/IO#  | N16 | vcc    | G16 | vss    | K1  |

| A13    | Q10 | BRDY#  | H15 | D20    | A1  | NC     | B13 | vcc    | H16 | vss    | K17 |

| A14    | S5  | BREQ   | Q15 | D21    | B2  | NC     | C13 | vcc    | К2  | vss    | L1  |

| A15    | R7  | BS8#   | D16 | D22    | A2  | NC     | J1* | vcc    | K16 | VSS    | L17 |

| A16    | Q9  | BS16#  | C17 | D23    | A4  | NMI    | B15 | vcc    | L16 | vss    | M1  |

| A17    | Q3  | CACHE# | B12 | D24    | A6  | PCD    | J17 | vcc    | M2  | vss    | M17 |

| A18    | R5  | CLK    | СЗ  | D25    | B6  | PCHK#  | Q17 | vcc    | M16 | VSS    | P17 |

| A19    | Q4  | CLKMUL | R17 | D26    | C7  | PLOCK# | Q16 | vcc    | P16 | VSS    | Q2  |

| A20    | Q8  | D/C#   | M15 | D27    | C6  | PWT    | L15 | vcc    | R3  | VSS    | R4  |

| A20M#  | D15 | D0     | P1  | D28    | C8  | RDY#   | F16 | vcc    | R6  | VSS    | S6  |

| A21    | Q5  | D1     | N2  | D29    | A8  | RESET  | C16 | vcc    | R8  | vss    | S8  |

| A22    | Q7  | D2     | N1  | D30    | C9  | SMADS# | C12 | vcc    | R9  | vss    | S9  |

| A23    | S3  | D3     | H2  | D31    | B8  | SMI#   | B10 | vcc    | R10 | vss    | S10 |

| A24    | Q6  | D4     | M3  | DP0    | N3  | SUSP#  | G15 | vcc    | R11 | VSS    | S11 |

| A25    | R2  | D5     | J2  | DP1    | F1  | SUSPA# | A13 | vcc    | R14 | VSS    | S12 |

| A26    | S2  | D6     | L2  | DP2    | нз  | тск    | A3  | VOLDET | S4  | VSS    | S14 |

| A27    | S1  | D7     | L3  | DP3    | A5  | тді    | A14 | vss    | A7  | W/R#   | N17 |

| A28    | R1  | D8     | F2  | EADS#  | B17 | TDO    | B16 | vss    | A9  | WM_RST | C10 |

Table 3.1. 168-Pin PGA Package Pin Numbers Sorted by Signal Name

\*Note: J1 is an internal no connect and may be connected to an external supply voltage.

| Pin | Signal |

|-----|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|--------|

| A1  | D20    | B12 | CACHE# | D17 | BOFF#  | J15 | BE2#   | P2  | A29    | R7  | A15    |

| A2  | D22    | B13 | NC     | E1  | VSS    | J16 | BE1#   | Р3  | A30    | R8  | VCC    |

| A3  | тск    | B14 | TMS    | E2  | vcc    | J17 | PCD    | P15 | HLDA   | R9  | VCC    |

| A4  | D23    | B15 | NMI    | E3  | D10    | K1  | VSS    | P16 | vcc    | R10 | vcc    |

| A5  | DP3    | B16 | TDO    | E15 | HOLD   | K2  | VCC    | P17 | VSS    | R11 | VCC    |

| A6  | D24    | B17 | EADS#  | E16 | vcc    | К3  | D14    | Q1  | A31    | R12 | A11    |

| A7  | VSS    | C1  | D11    | E17 | VSS    | K15 | BE0#   | Q2  | VSS    | R13 | A8     |

| A8  | D29    | C2  | D18    | F1  | DP1    | K16 | vcc    | Q3  | A17    | R14 | vcc    |

| A9  | VSS    | СЗ  | CLK    | F2  | D8     | K17 | VSS    | Q4  | A19    | R15 | A3     |

| A10 | INVAL  | C4  | vcc    | F3  | D15    | L1  | VSS    | Q5  | A21    | R16 | BLAST# |

| A11 | VSS    | C5  | vcc    | F15 | KEN#   | L2  | D6     | Q6  | A24    | R17 | CLKMUL |

| A12 | HITM#  | C6  | D27    | F16 | RDY#   | L3  | D7     | Q7  | A22    | S1  | A27    |

| A13 | SUSPA# | C7  | D26    | F17 | BE3#   | L15 | PWT    | Q8  | A20    | S2  | A26    |

| A14 | TDI    | C8  | D28    | G1  | VSS    | L16 | VCC    | Q9  | A16    | S3  | A23    |

| A15 | IGNNE# | C9  | D30    | G2  | vcc    | L17 | VSS    | Q10 | A13    | S4  | VOLDET |

| A16 | INTR   | C10 | WM_RST | G3  | D12    | M1  | VSS    | Q11 | A9     | S5  | A14    |

| A17 | AHOLD  | C11 | UP#    | G15 | SUSP#  | M2  | vcc    | Q12 | A5     | S6  | VSS    |

| B1  | D19    | C12 | SMADS# | G16 | vcc    | M3  | D4     | Q13 | A7     | S7  | A12    |

| B2  | D21    | C13 | NC     | G17 | VSS    | M15 | D/C#   | Q14 | A2     | S8  | VSS    |

| B3  | VSS    | C14 | FERR#  | H1  | VSS    | M16 | vcc    | Q15 | BREQ   | S9  | VSS    |

| B4  | VSS    | C15 | FLUSH# | H2  | D3     | M17 | VSS    | Q16 | PLOCK# | S10 | VSS    |

| B5  | VSS    | C16 | RESET  | нз  | DP2    | N1  | D2     | Q17 | PCHK#  | S11 | VSS    |

| B6  | D25    | C17 | BS16#  | H15 | BRDY#  | N2  | D1     | R1  | A28    | S12 | VSS    |

| B7  | vcc    | D1  | D9     | H16 | vcc    | N3  | DP0    | R2  | A25    | S13 | A10    |

| B8  | D31    | D2  | D13    | H17 | vss    | N15 | LOCK#  | R3  | vcc    | S14 | VSS    |

| B9  | vcc    | D3  | D17    | J1* | NC     | N16 | M/IO#  | R4  | vss    | S15 | A6     |

| B10 | SMI#   | D15 | A20M#  | J2  | D5     | N17 | W/R#   | R5  | A18    | S16 | A4     |

| B11 | vcc    | D16 | BS8#   | J3  | D16    | P1  | D0     | R6  | vcc    | S17 | ADS#   |

Table 3.2. 168-Pin PGA Package Signal Names Sorted by Pin Number

\*Note: J1 is an internal no connect and may be connected to an external supply voltage.

| Table 3.3. | 168-Pin | PGA | Package | Dimensions |

|------------|---------|-----|---------|------------|

|------------|---------|-----|---------|------------|

| SYMBOL | MILLIM | IETERS | INC   | HES   |

|--------|--------|--------|-------|-------|

| STWBOL | MIN    | MAX    | MIN   | MAX   |

| A      | 3.56   | 4.57   | 0.140 | 0.180 |

| A1     | 1.14   | 1.40   | 0.045 | 0.055 |

| В      | 0.43   | 0.51   | 0.017 | 0.020 |

| D      | 44.07  | 44.83  | 1.735 | 1.765 |

| D1     | 40.51  | 40.77  | 1.595 | 1.605 |

| e1     | 2.29   | 2.79   | 0.090 | 0.110 |

| L      | 2.54   | 3.30   | 0.100 | 0.130 |

# 3.2 208-Lead QFP Package

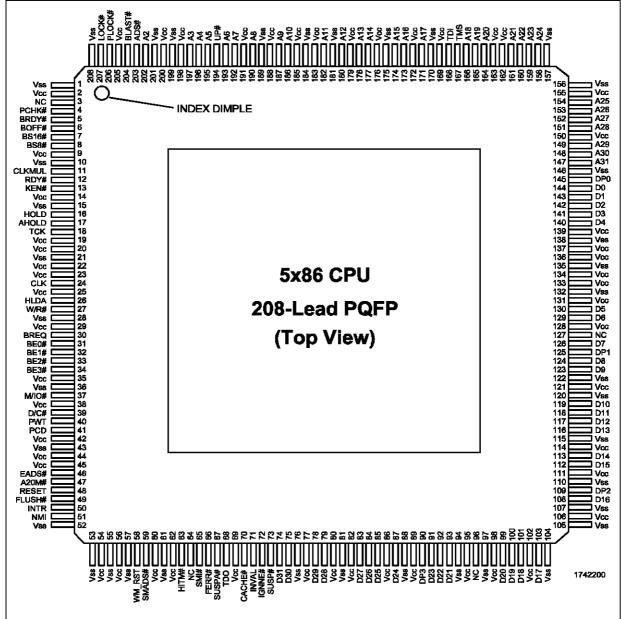

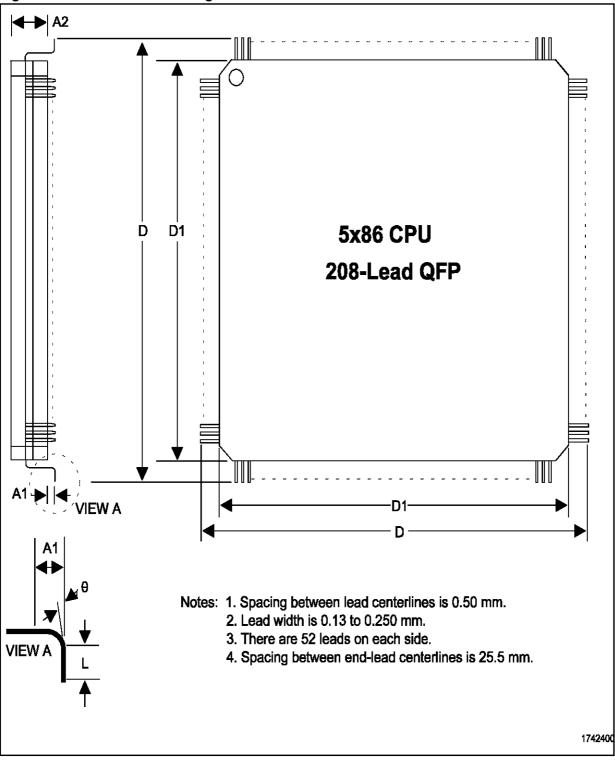

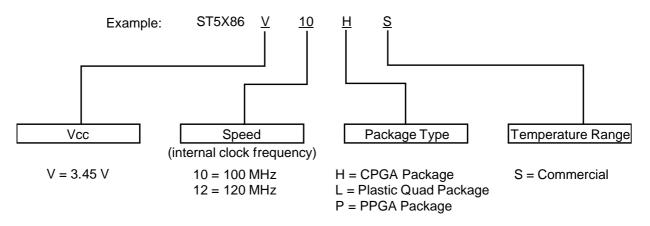

The pin assignments for the 5x86V10LS and 5x86V12LS are shown in Figure 3.3. Pins are listed by signal name in Table 3.4. and by pin number in Table 3.5. Package dimensions for the 208-lead QFP (Quad Flat Pack) are shown in Figure 3.4. and Table 3.6.

Figure 3.3. 208-Lead QFP Package Pin Assignments

| Signal | Pin |

|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|

| A2     | 202 | BE2#   | 33  | D24    | 87  | RESET  | 48  | Vcc    | 98  | Vss    | 52  |

| A3     | 197 | BE3#   | 34  | D25    | 85  | SMADS# | 59  | Vcc    | 102 | Vss    | 53  |

| A4     | 196 | BLAST# | 204 | D26    | 84  | SMI#   | 65  | Vcc    | 106 | Vss    | 55  |

| A5     | 195 | BOFF#  | 6   | D27    | 83  | SUSP#  | 73  | Vcc    | 111 | Vss    | 57  |

| A6     | 193 | BRDY#  | 5   | D28    | 79  | SUSPA# | 67  | Vcc    | 114 | Vss    | 61  |

| A7     | 192 | BREQ   | 30  | D29    | 78  | тск    | 18  | Vcc    | 121 | Vss    | 76  |

| A8     | 190 | BS16#  | 7   | D30    | 75  | TDI    | 168 | Vcc    | 128 | Vss    | 81  |

| A9     | 187 | BS8#   | 8   | D31    | 74  | TDO    | 68  | Vcc    | 131 | Vss    | 88  |

| A10    | 186 | CACHE# | 70  | D/C#   | 39  | TMS    | 167 | Vcc    | 133 | Vss    | 94  |

| A11    | 182 | CLK    | 24  | DP0    | 145 | UP#    | 194 | Vcc    | 134 | Vss    | 97  |

| A12    | 180 | CLKMUL | 11  | DP1    | 125 | Vcc    | 2   | Vcc    | 136 | Vss    | 104 |

| A13    | 178 | D0     | 144 | DP2    | 109 | Vcc    | 9   | Vcc    | 137 | Vss    | 105 |

| A14    | 177 | D1     | 143 | DP3    | 90  | Vcc    | 14  | Vcc    | 139 | Vss    | 107 |

| A15    | 174 | D2     | 142 | EADS#  | 46  | Vcc    | 19  | Vcc    | 150 | Vss    | 110 |

| A16    | 173 | D3     | 141 | FERR#  | 66  | Vcc    | 20  | Vcc    | 155 | Vss    | 115 |

| A17    | 171 | D4     | 140 | FLUSH# | 49  | Vcc    | 22  | Vcc    | 162 | Vss    | 120 |

| A18    | 166 | D5     | 130 | HITM#  | 63  | Vcc    | 23  | Vcc    | 163 | Vss    | 122 |

| A19    | 165 | D6     | 129 | HLDA   | 26  | Vcc    | 25  | Vcc    | 169 | Vss    | 132 |

| A20    | 164 | D7     | 126 | HOLD   | 16  | Vcc    | 29  | Vcc    | 172 | Vss    | 135 |

| A20M#  | 47  | D8     | 124 | IGNNE# | 72  | Vcc    | 35  | Vcc    | 176 | Vss    | 138 |

| A21    | 161 | D9     | 123 | INTR   | 50  | Vcc    | 38  | Vcc    | 179 | Vss    | 146 |

| A22    | 160 | D10    | 119 | INVAL  | 71  | Vcc    | 42  | Vcc    | 183 | Vss    | 156 |

| A23    | 159 | D11    | 118 | KEN#   | 13  | Vcc    | 44  | Vcc    | 185 | Vss    | 157 |

| A24    | 158 | D12    | 117 | LOCK#  | 207 | Vcc    | 45  | Vcc    | 188 | Vss    | 170 |

| A25    | 154 | D13    | 116 | M/IO#  | 37  | Vcc    | 54  | Vcc    | 191 | Vss    | 175 |

| A26    | 153 | D14    | 113 | NC     | 3*  | Vcc    | 56  | Vcc    | 198 | Vss    | 181 |

| A27    | 152 | D15    | 112 | NC     | 64  | Vcc    | 60  | Vcc    | 200 | Vss    | 184 |

| A28    | 151 | D16    | 108 | NC     | 96  | Vcc    | 62  | Vcc    | 205 | Vss    | 189 |

| A29    | 149 | D17    | 103 | NC     | 127 | Vcc    | 69  | Vss    | 1   | Vss    | 199 |

| A30    | 148 | D18    | 101 | NMI    | 51  | Vcc    | 77  | Vss    | 10  | Vss    | 201 |

| A31    | 147 | D19    | 100 | PCD    | 41  | Vcc    | 80  | Vss    | 15  | Vss    | 208 |

| ADS#   | 203 | D20    | 99  | РСНК   | 4   | Vcc    | 82  | Vss    | 21  | WM_RST | 58  |

| AHOLD  | 17  | D21    | 93  | PLOCK# | 206 | Vcc    | 86  | Vss    | 28  | W/R#   | 27  |

| BE0#   | 31  | D22    | 92  | PWT    | 40  | Vcc    | 89  | Vss    | 36  |        |     |

| BE1#   | 32  | D23    | 91  | RDY#   | 12  | Vcc    | 95  | Vss    | 43  |        |     |

Table 3.4. 208-Lead QFP Package Pins Sorted by Signal Name

\*Note: Pin 3 is an internal no connect and may be connected to an external supply voltage.

| Pin | Signal |

|-----|--------|-----|--------|-----|--------|-----|--------|-----|--------|-----|--------|

| 1   | Vss    | 36  | Vss    | 71  | INVAL  | 106 | Vcc    | 141 | D3     | 176 | Vcc    |

| 2   | Vcc    | 37  | M/IO#  | 72  | IGNNE# | 107 | Vss    | 142 | D2     | 177 | A14    |

| 3*  | NC     | 38  | Vcc    | 73  | SUSP#  | 108 | D16    | 143 | D1     | 178 | A13    |

| 4   | PCHK#  | 39  | D/C#   | 74  | D31    | 109 | DP2    | 144 | D0     | 179 | Vcc    |

| 5   | BRDY#  | 40  | PWT    | 75  | D30    | 110 | Vss    | 145 | DP0    | 180 | A12    |

| 6   | BOFF#  | 41  | PCD    | 76  | Vss    | 111 | Vcc    | 146 | Vss    | 181 | Vss    |

| 7   | BS16#  | 42  | Vcc    | 77  | Vcc    | 112 | D15    | 147 | A31    | 182 | A11    |

| 8   | BS8#   | 43  | Vss    | 78  | D29    | 113 | D14    | 148 | A30    | 183 | Vcc    |

| 9   | Vcc    | 44  | Vcc    | 79  | D28    | 114 | Vcc    | 149 | A29    | 184 | Vss    |

| 10  | Vss    | 45  | Vcc    | 80  | Vcc    | 115 | Vss    | 150 | Vcc    | 185 | Vcc    |

| 11  | CLKMUL | 46  | EADS#  | 81  | Vss    | 116 | D13    | 151 | A28    | 186 | A10    |

| 12  | RDY#   | 47  | A20M#  | 82  | Vcc    | 117 | D12    | 152 | A27    | 187 | A9     |

| 13  | KEN#   | 48  | RESET  | 83  | D27    | 118 | D11    | 153 | A26    | 188 | Vcc    |

| 14  | Vcc    | 49  | FLUSH# | 84  | D26    | 119 | D10    | 154 | A25    | 189 | Vss    |

| 15  | Vss    | 50  | INTR   | 85  | D25    | 120 | Vss    | 155 | Vcc    | 190 | A8     |

| 16  | HOLD   | 51  | NMI    | 86  | Vcc    | 121 | Vcc    | 156 | Vss    | 191 | Vcc    |

| 17  | AHOLD  | 52  | Vss    | 87  | D24    | 122 | Vss    | 157 | Vss    | 192 | A7     |

| 18  | тск    | 53  | Vss    | 88  | Vss    | 123 | D9     | 158 | A24    | 193 | A6     |

| 19  | Vcc    | 54  | Vcc    | 89  | Vcc    | 124 | D8     | 159 | A23    | 194 | UP#    |

| 20  | Vcc    | 55  | Vss    | 90  | DP3    | 125 | DP1    | 160 | A22    | 195 | A5     |

| 21  | Vss    | 56  | Vcc    | 91  | D23    | 126 | D7     | 161 | A21    | 196 | A4     |

| 22  | Vcc    | 57  | Vss    | 92  | D22    | 127 | NC     | 162 | Vcc    | 197 | A3     |

| 23  | Vcc    | 58  | WM_RST | 93  | D21    | 128 | Vcc    | 163 | Vcc    | 198 | Vcc    |

| 24  | CLK    | 59  | SMADS# | 94  | Vss    | 129 | D6     | 164 | A20    | 199 | Vss    |

| 25  | Vcc    | 60  | Vcc    | 95  | Vcc    | 130 | D5     | 165 | A19    | 200 | Vcc    |

| 26  | HLDA   | 61  | Vss    | 96  | NC     | 131 | Vcc    | 166 | A18    | 201 | Vss    |

| 27  | W/R#   | 62  | Vcc    | 97  | Vss    | 132 | Vss    | 167 | TMS    | 202 | A2     |

| 28  | Vss    | 63  | HITM#  | 98  | Vcc    | 133 | Vcc    | 168 | TDI    | 203 | ADS#   |

| 29  | Vcc    | 64  | NC     | 99  | D20    | 134 | Vcc    | 169 | Vcc    | 204 | BLAST# |

| 30  | BREQ   | 65  | SMI#   | 100 | D19    | 135 | Vss    | 170 | Vss    | 205 | Vcc    |

| 31  | BE0#   | 66  | FERR#  | 101 | D18    | 136 | Vcc    | 171 | A17    | 206 | PLOCK# |

| 32  | BE1#   | 67  | SUSPA# | 102 | Vcc    | 137 | Vcc    | 172 | Vcc    | 207 | LOCK#  |

| 33  | BE2#   | 68  | TDO    | 103 | D17    | 138 | Vss    | 173 | A16    | 208 | Vss    |

| 34  | BE3#   | 69  | Vcc    | 104 | Vss    | 139 | Vcc    | 174 | A15    |     |        |

| 35  | Vcc    | 70  | CACHE# | 105 | Vss    | 140 | D4     | 175 | Vss    |     |        |

Table 3.5. 208-Lead QFP Package Signals Sorted by Pin Number

\*Note: Pin 3 is an internal no connect and may be connected to an external supply voltage.

| SYMBOL | MILLIMETERS |       | INC   | HES   | DEGREES |     |  |

|--------|-------------|-------|-------|-------|---------|-----|--|

| STWBOL | MIN         | MAX   | MIN   | MAX   | MIN     | МАХ |  |

| A1     | 0.28        | 0.41  | 0.011 | 0.017 |         |     |  |

| A2     | 3.29        | 3.45  | 0.130 | 0.136 |         |     |  |

| D      | 30.35       | 30.85 | 1.195 | 1.215 |         |     |  |

| D1     | 27.90       | 28.10 | 1.095 | 1.107 |         |     |  |

| L      | 0.50        | 0.70  | 0.019 | 0.028 |         |     |  |

| θ      |             |       |       |       | 0       | 7   |  |

Table 3.6. 208-Lead QFP Package Dimensions

# 3.3 Thermal Characteristics

The 5x86 processor is designed to operate when the case temperature at the top center of the package is between 0°C and 85°C. The maximum die (junction) temperature, T<sub>J MAX</sub>, and the maximum ambient temperature, T<sub>A MAX</sub>, can be calculated by substituting thermal resistance and maximum values for case or junction temperature and power dissipation in the following equations:

$T_{J} = T_{C} + (P * \theta_{JC})$

$$T_A = T_J - (P * \theta_{JA})$$

where:

| T <sub>A</sub>       | <ul> <li>Ambient temperature (°C)</li> </ul>                       |

|----------------------|--------------------------------------------------------------------|

| Т <sub>Ј</sub>       | <ul> <li>Average junction temperature (°C)</li> </ul>              |

| т <sub>с</sub>       | <ul> <li>Case temperature at top center of package (°C)</li> </ul> |

| Р                    | = Power dissipation (W)                                            |

| $\theta_{\text{JC}}$ | <ul> <li>Junction-to-case thermal resistance (°C/W)</li> </ul>     |

| θ <sub>JA</sub>      | = Junction-to-ambient thermal resistance (°C/W).                   |

|                      |                                                                    |

## **PGA Package**

Table 3.7. lists the junction-to-ambient and junction-to-case thermal resistances for the 5x86 processors in the 168-pin PGA (pin grid array) package. These devices have an "H" or "P" package suffix as shown in the ordering information. Table 3.8. lists the maximum ambient temperatures permitted for various clock frequencies at maximum I<sub>CC</sub> and V<sub>CC</sub> = 3.6 volts. The heatsink used to measure the data below is characterized by  $\theta_{JA}$  = 10 °C/W.

| Table 3.7. | PGA Package Thermal Resistance with No Airflow |

|------------|------------------------------------------------|

|------------|------------------------------------------------|

| PGA THERMAL RESISTANCE (°C/W) |                 |                 |                 |  |

|-------------------------------|-----------------|-----------------|-----------------|--|

| WITH НЕ                       | EATSINK         | WITHOUT         | HEATSINK        |  |

| $\theta_{JA}$                 | θ <sub>JC</sub> | θ <sub>JA</sub> | θ <sub>JC</sub> |  |

| 12.5                          | 2.5             | 17              | 2.0             |  |

| Table 3.8. P | PGA Package Maximum | Ambient Temperature | (with Heatsink, Airflow = 0) |

|--------------|---------------------|---------------------|------------------------------|

|--------------|---------------------|---------------------|------------------------------|

| CPU INTERNAL CLOCK FREQUENCY                             | AMBIENT TEMPERATURE |

|----------------------------------------------------------|---------------------|

| 100 MHz                                                  | 42 °C               |

| <b>120 MHz</b><br>(5x86V12HS and 5x86V12PS devices only) | 35 °C               |

# **QFP** Package

Table 3.9. lists the junction-to-ambient and junction-to-case thermal resistances for the 5x86 processors in the QFP (quad flat pack) package without a heat sink. These devices have an "L" package suffix as shown in the ordering information.

| AIRFLOW<br>(LFM) | QFP THERMAL RESISTANCE<br>(°C/W) |     |  |  |

|------------------|----------------------------------|-----|--|--|

| (LFW)            | $\theta_{JA}$                    | θJC |  |  |

| 0                | 16                               | 2   |  |  |

| 100              | 14                               | 2   |  |  |

| Table 3.10. | QFP Package Maximum Ambient Temperature |

|-------------|-----------------------------------------|

|-------------|-----------------------------------------|

| CPU INTERNAL CLOCK<br>FREQUENCY            | AIRFLOW<br>(LFM) | AMBIENT<br>TEMPERATURE<br>(°C) |

|--------------------------------------------|------------------|--------------------------------|

| 100 MHz                                    | 0                | 25                             |

|                                            | 100              | 33                             |

| <b>120 MHz</b><br>(5x86V12LS devices only) | 0                | 14                             |

|                                            | 100              | 25                             |

Heatsinking is required for most applications. The appropriate heat sink will have a total case-to-heatsink and heatsink-to-ambient thermal resistance ( $\theta_{CH} + \theta_{HA}$ ) no larger than the value resulting from the equation below.

| θ <sub>CH +</sub> θ <sub>HA</sub><br>where: | = $(T_{C \text{ MAX}} - T_{A \text{ MAX}}) / (V_{CC \text{ MAX}} * I_{CC \text{ MAX}})$ |  |

|---------------------------------------------|-----------------------------------------------------------------------------------------|--|