# PROGRAMMABLE TRANSPORT IC FOR DVB APPLICATIONS

#### **FEATURES**

- Enhanced 32-bit VL-RISC CPU 0 to 50 MHz processor clock fast integer/bit operations very high code density

- 8 Kbytes on-chip SRAM

200 Mbytes/s maximum bandwidth

- Programmable memory interface

4 separately configurable regions

8/16/32-bits wide

support for mixed memory

2 cycle external access

support for page mode DRAM

support for MPEG decoders

support for PCMCIA CA module

- Serial communications

**OS-Link**

- 2 Programmable UARTs (ASC)

- 2 Synchronous serial interfaces (I<sup>2</sup>C)

- Vectored interrupt subsystem

Prioritized interrupts

8 levels of preemption

500 ns response time

- DMA engines/interfaces

- 2 MPEG decoder DMAs

- 2 SmartCard interfaces

Link IC DMA interface

Section filter engine

**DVB** descrambler DMA

Block move DMA

Teletext interface (I/O)

IEEE 1284/ Transport out DMA

- PWM/counter module

- Two 8-bit PWM

Two 32-bit counters and capture registers

Low power controller

Real time clock

Watchdog timer

- Programmable IO module

- Professional toolset support

ANSI C compiler and libraries

INQUEST advanced debugging tools

- Technology

- 208 pin PQFP package

0.5 micron process technology

JTAG Test Access Port

#### **APPLICATIONS**

Set top terminals

# **Contents**

| 1 | Intro | Introduction                         |  |  |  |  |  |

|---|-------|--------------------------------------|--|--|--|--|--|

| 2 | ST2   | ST20-TP2 architecture overview       |  |  |  |  |  |

|   | 2.1   | Transport demultiplexing             |  |  |  |  |  |

|   | 2.2   | ST20-TP2 functional modules          |  |  |  |  |  |

| 3 | Cen   | tral processing unit                 |  |  |  |  |  |

|   | 3.1   | Registers                            |  |  |  |  |  |

|   | 3.2   | Processes and concurrency            |  |  |  |  |  |

|   | 3.3   | Priority                             |  |  |  |  |  |

|   | 3.4   | Process communications               |  |  |  |  |  |

|   | 3.5   | Timers                               |  |  |  |  |  |

|   | 3.6   | Traps and exceptions                 |  |  |  |  |  |

| 4 | Inte  | rupt controller                      |  |  |  |  |  |

|   | 4.1   | Interrupt vector table               |  |  |  |  |  |

|   | 4.2   | Interrupt handlers                   |  |  |  |  |  |

|   | 4.3   | Interrupt latency                    |  |  |  |  |  |

|   | 4.4   | Preemption and interrupt priority    |  |  |  |  |  |

|   | 4.5   | Restrictions on interrupt handlers   |  |  |  |  |  |

|   | 4.6   | Interrupt configuration registers    |  |  |  |  |  |

| 5 | Inte  | rupt level controller                |  |  |  |  |  |

|   | 5.1   | Interrupt level controller registers |  |  |  |  |  |

| 6 | Insti | Instruction set                      |  |  |  |  |  |

|   | 6.1   | Instruction cycles                   |  |  |  |  |  |

|   | 6.2   | Instruction characteristics          |  |  |  |  |  |

|   | 6.3   | Instruction set tables               |  |  |  |  |  |

| 7 | Men   | nory map                             |  |  |  |  |  |

|   | 7.1   | System memory use                    |  |  |  |  |  |

|   | 7.2   | Boot ROM                             |  |  |  |  |  |

|   | 7.3   | Internal peripheral space            |  |  |  |  |  |

| 8 | Men   | nory subsystem                       |  |  |  |  |  |

|   | 8.1   | SRAM                                 |  |  |  |  |  |

| 9 | Exte  | rnal memory interface                |  |  |  |  |  |

|   | 9.1   | Pin functions                        |  |  |  |  |  |

|   | J. I  | I III IUIIUIIO                       |  |  |  |  |  |

|    | 9.2    | External bus evalos                      | 57  |

|----|--------|------------------------------------------|-----|

|    |        | External bus cycles                      |     |

|    | 9.3    | EMI Configuration                        | 63  |

|    | 9.4    | EMI initialization                       | 77  |

| 10 | Syste  | em services                              | 79  |

|    | 10.1   | Reset and Analyse                        | 79  |

|    | 10.2   | Bootstrap                                | 80  |

| 11 | Test   | access port                              | 82  |

|    | 11.1   | Boundary scan description                | 82  |

| 12 | Cloc   | ks and low power controller              | 83  |

|    | 12.1   | Clocks                                   | 83  |

|    | 12.2   | Low power control                        | 83  |

|    | 12.3   | Low power configuration registers        | 85  |

|    | 12.4   | Clocking                                 | 88  |

| 13 | Asyn   | chronous serial controller               | 89  |

|    | 13.1   | Operation                                | 93  |

|    | 13.2   | Hardware error detection capabilities    | 96  |

|    | 13.3   | Baud rate generation                     | 96  |

|    | 13.4   | Interrupt control                        | 98  |

|    | 13.5   | SmartCard mode specific operation        | 102 |

| 14 | Smar   | tCard interface                          | 103 |

|    | 14.1   | External interface                       | 103 |

|    | 14.2   | SmartCard clock generator                | 104 |

| 15 | I2C ii | nterfaces (SSC)                          | 106 |

|    | 15.1   | High-speed synchronous serial controller | 106 |

| 16 | PWM    | and counter module                       | 116 |

|    | 16.1   | External interface                       | 116 |

|    | 16.2   | PWM and counter control registers        | 116 |

| 17 | Paral  | lel input/output                         | 121 |

|    | 17.1   | PIO Ports0-4                             | 121 |

| 18 | Seria  | I link interface (OS-Link)               | 124 |

|    | 18.1   | OS-Link protocol                         | 124 |

|    | 18.2   | OS-Link speed                            | 124 |

|    | 18.3   | OS-Link connections                      | 125 |

## **ST20-TP2**

| 19 | Link   | IC interface                           | 126 |

|----|--------|----------------------------------------|-----|

|    | 19.1   | External interface                     | 126 |

|    | 19.2   | Link IC interface operation            |     |

| 20 | MPF    | G DMA controllers                      | 128 |

| 20 |        |                                        |     |

|    | 20.1   | External interface                     |     |

|    | 20.2   | MPEG DMA transfers                     |     |

|    |        |                                        |     |

| 21 | DVB    | decryption controller                  | 132 |

|    | 21.1   | Decrypting blocks of data              | 132 |

|    | 21.2   | Control registers                      | 133 |

| 22 | Bloc   | k move DMA                             | 134 |

|    | 22.1   | Moving blocks of data                  | 134 |

|    | 22.2   | Configuration register                 | 134 |

| 23 | Telet  | ext interface                          | 135 |

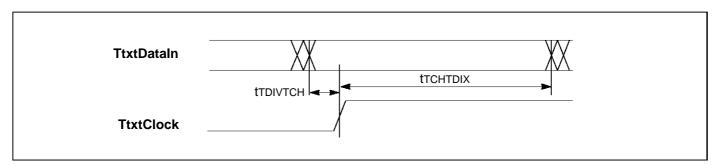

|    | 23.1   | Teletext interface pins                | 135 |

|    | 23.2   | Teletext data out                      | 135 |

|    | 23.3   | Teletext data in                       | 137 |

|    | 23.4   | Teletext interrupt control             | 137 |

|    | 23.5   | Control registers                      | 137 |

| 24 | Secti  | ion filter                             | 141 |

|    | 24.1   | Section filter configuration registers | 141 |

|    | 24.2   | DMA registers                          | 143 |

|    | 24.3   | Section filtering operation            | 147 |

| 25 | IEEE   | 1284 port (PC parallel port)           | 149 |

|    | 25.1   | 1284 port pins                         | 150 |

|    | 25.2   | 1284 Port modes of operation           | 151 |

|    | 25.3   | 1284 port control registers            | 156 |

|    | 25.4   | Signal Filtering                       | 165 |

| 26 | Conf   | iguration register addresses           | 167 |

| 27 | Devi   | ce configuration                       | 176 |

|    | 27.1   | PIO pins and alternate functions       |     |

|    | 27.1   | Interrupt assignments                  |     |

|    |        |                                        |     |

| 28 | Pin li | ist                                    | 179 |

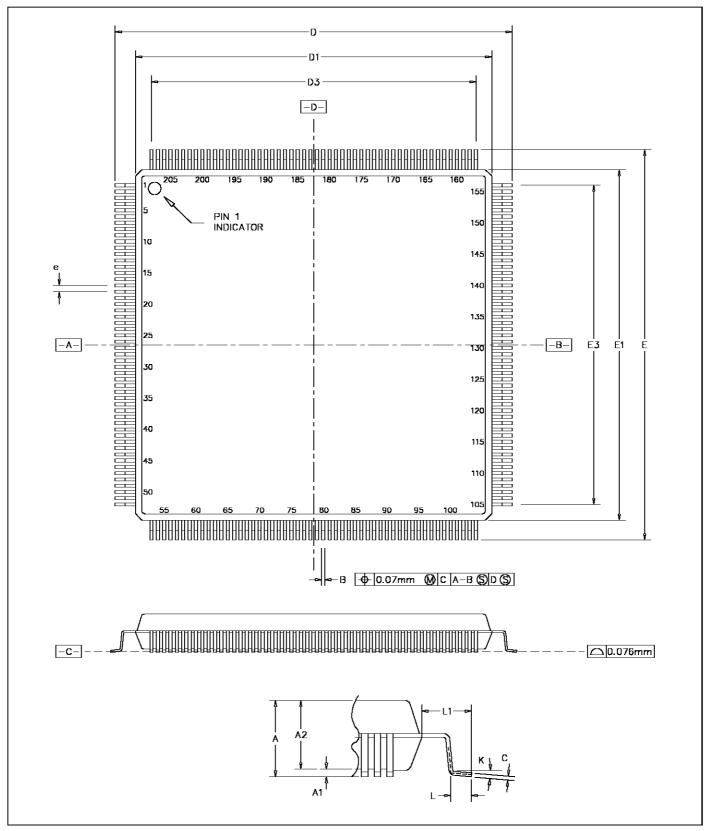

| 29 | Pack  | age specifications              | 183 |

|----|-------|---------------------------------|-----|

|    | 29.1  | ST20-TP2 package pinout         | 183 |

|    | 29.2  | 208 pin PQFP package dimensions |     |

| 30 | Elect | trical specifications           | 191 |

|    | 30.1  | Absolute maximum ratings        | 191 |

|    | 30.2  | Operating conditions            | 191 |

|    | 30.3  | DC specifications               | 192 |

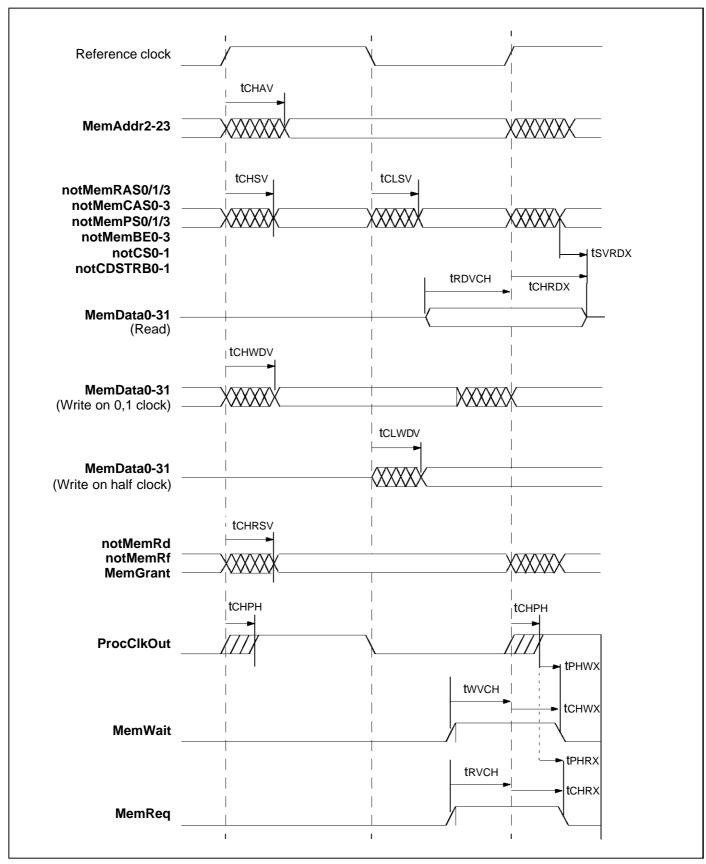

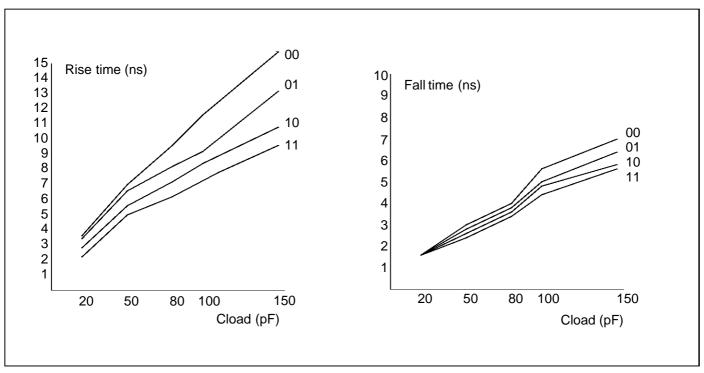

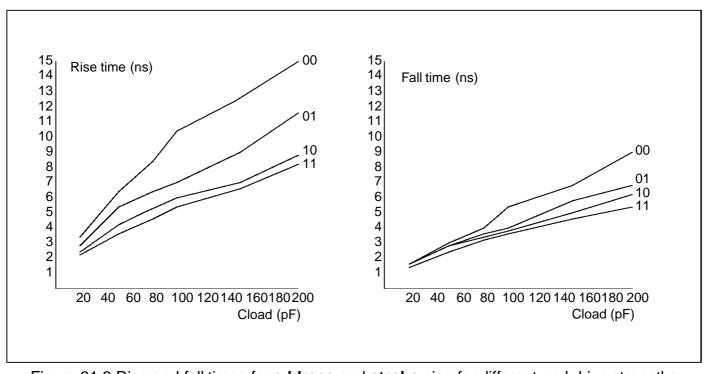

| 31 | Timiı | ng specifications               | 193 |

|    | 31.1  | EMI timings                     | 193 |

|    | 31.2  | PIO timings                     | 196 |

|    | 31.3  | Link timings                    |     |

|    | 31.4  | Reset and Analyse timings       | 198 |

|    | 31.5  | Clock timings                   | 199 |

|    | 31.6  | TAP timings                     | 200 |

|    | 31.7  | Link IC timings                 | 201 |

|    | 31.8  | Teletext timings                | 202 |

| 32 | Devi  | ce ID                           | 203 |

| 33 | Orde  | ring information                | 203 |

| ۸n | nondi | v AChannal madal                | 204 |

# 1 Introduction

The ST20-TP2 is a programmable transport IC designed to meet the transport layer specification for DVB set top box systems.

The ST20-TP2 combines the functionality of the set top box transport IC and system microcontroller in to a single device. The performance offered by the ST20 32-bit micro-core allows the following operations to be performed in software:

- 1 Transport layer demultiplexing,

- 2 Device drivers and synchronization,

- 3 Electronic program guide,

- 4 System management functions,

- 5 Conditional access module.

Note: Source code software licences are available from SGS-THOMSON for modules 1 and 2 above.

The advantages of using software versus dedicated hardware for these functions are two-fold:

- Flexibility it is quick and simple to modify software to adapt to a new system requirement or to a change in a standard.

- Upgradability the use of a 32-bit CPU enables the use of advanced graphics routines for on-screen display functions and enables fast turn-around of system upgrades.

The ST20 micro-core family has been developed by SGS-THOMSON Microelectronics to provide the tools and building blocks to enable the development of highly integrated application specific 32-bit devices at the lowest cost and fastest time to market. The ST20 macrocell library includes the ST20Cx family of 32-bit VL-RISC (variable length reduced instruction set computer) micro-cores, embedded memories, standard peripherals, I/O, controllers and ASICs.

The ST20-TP2 uses the ST20 macrocell library to provide all of the dedicated hardware modules required in a DVB set top box programmable transport-IC. These include:

- Link-IC interface to MPEG transport stream,

- I<sup>2</sup>C interface to other devices in the set top box,

- UART serial I/O interface to modem and auxiliary ports,

- Interrupt controller for internal and external interrupts,

- 8 Kbytes of internal SRAM,

- DMA module to MPEG audio and video device(s),

- Section filter module,

- External memory interface supporting DRAM, EPROM and peripherals,

- PWM/timer module for control of system clock VCXOs,

- Programmable I/O pins,

- DVB descrambler.

- Smart card interface,

- IEEE 1284 port.

The ST20-TP2 has been designed to minimize system costs. The memory interface module contains a zero glue logic DRAM controller, a low cost 8-bit EPROM interface and a port for connecting directly to the MPEG audio and video devices. Furthermore the ST20 VL-RISC micro-core has the highest code density of any 32-bit CPU, leading to the lowest cost program ROM.

The ST20-TP2 is supported by a range of software and hardware development tools for PC and UNIX hosts including an ANSI-C ST20 software toolset incorporating the ST20 INQUEST window based debugger.

# 2 ST20-TP2 architecture overview

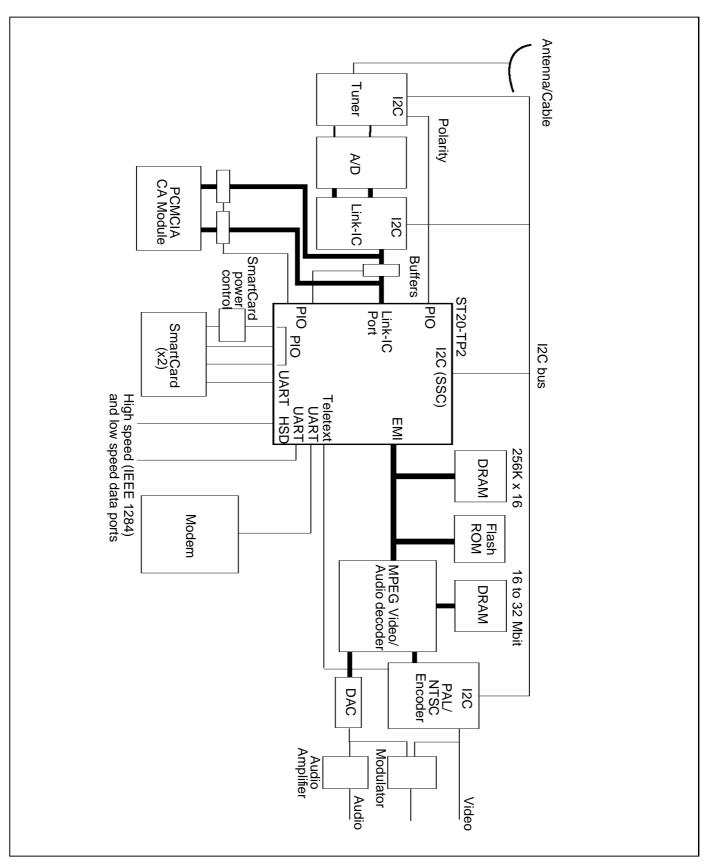

A block diagram of a digital set top receiver is shown in Figure 2.1.

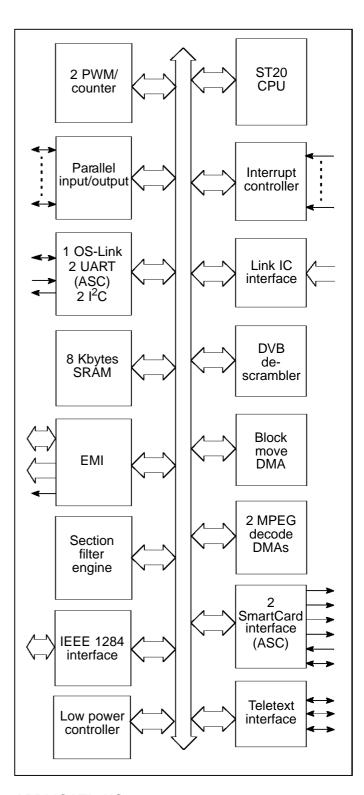

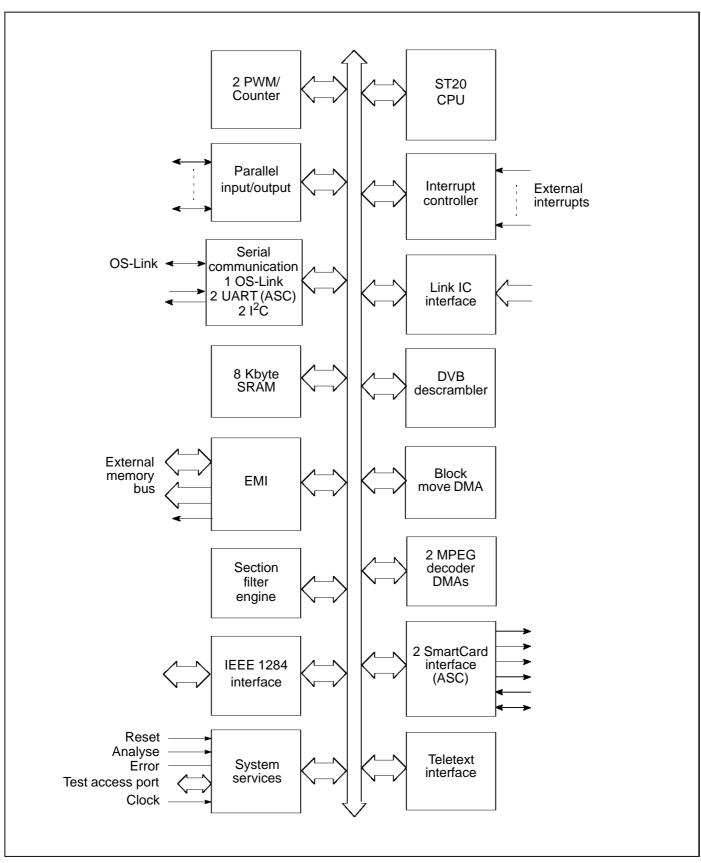

The ST20-TP2 performs the system microcontroller and transport demultiplexer functions. It has been designed to directly interface to external memory and peripherals with no extra glue logic, keeping the system cost to a minimum. The ST20-TP2 architectural block diagram is shown in Figure 2.2.

# 2.1 Transport demultiplexing

The transport demultiplexing function is performed in a mixture of hardware and software. Typical operation is as described below.

Data packets from the Link-IC are input into memory by the Link-IC interface using DMA. The packet is parsed in software to determine its type and to extract data from it. If the packet is encrypted using the DVB Standard, a memory to memory DMA operation through the DVB decryption controller (DVBC) is performed before the packet can be parsed.

After parsing the packet, the data is either transferred to buffers in external memory or passed to other software tasks as a message. The transfer from internal to external memory can also be performed as a memory to memory DMA operation using the block move module.

Audio or Video MPEG compressed data extracted from the input data packets is transferred to the decoders using two independent DMA controllers. These read data from memory and then write it to a decoder in response to a DMA request from the decoder.

The unique architecture of the ST20 family, in particular the scheduler implemented in microcode, allows the transport demultiplex functions to typically occupy less than half the available CPU cycles.

Figure 2.1 Digital set top box block diagram

#### 2.2 ST20-TP2 functional modules

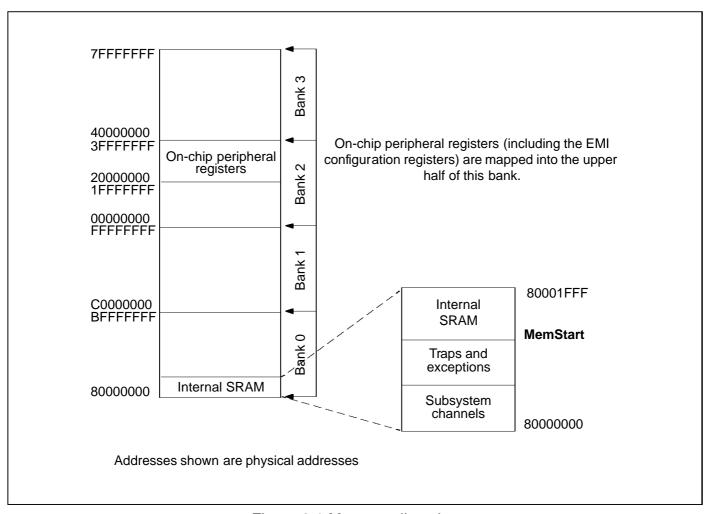

Figure 2.2 shows the subsystem modules that comprise the ST20-TP2. These modules are outlined below and more detailed information is given in the following chapters of this datasheet.

#### **CPU**

The Central Processing Unit (CPU) on the ST20-TP2 is the ST20 32-bit processor core. It contains instruction processing logic, instruction and data pointers, and an operand register. It directly accesses the high speed on-chip memory, which can store data or programs. Where larger amounts of memory are required, the processor can access memory via the External Memory Interface (EMI).

#### **Memory subsystem**

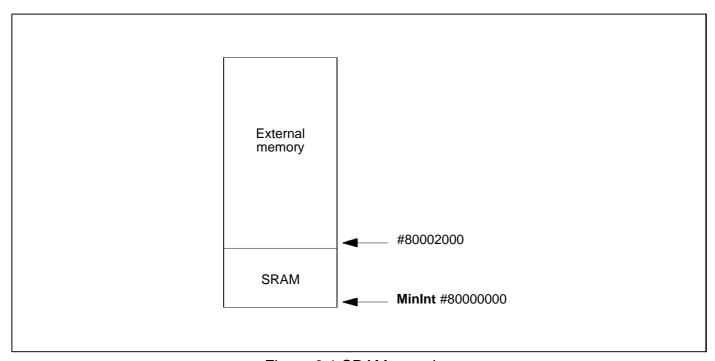

The ST20-TP2 on-chip memory system provides 200 Mbytes/s internal data bandwidth, supporting pipelined 2-cycle internal memory access at 20 ns cycle times. The ST20-TP2 memory system consists of SRAM and an external memory interface (EMI).

The ST20-TP2 product has 8 Kbytes of on-chip SRAM. The advantage of this is the ability to store time critical code on chip, for instance interrupt routines, software kernels or device drivers, and even frequently used data. Furthermore small systems could place all code and data on-chip, increasing performance and reducing system cost. For the transport layer demultiplexing functions calculations have shown that the code can fit in internal memory together with its stack and packet buffers. This gives the required performance for these functions.

The ST20-TP2 EMI controls access to the external memory and peripherals including the MPEG decoder registers and DMA data ports. Special strobes have been added to one of the banks of the EMI to allow a direct interface to the SGS-THOMSON Microelectronics range of MPEG2 audio and video decoders.

The ST20-TP2 EMI can access a 16 Mbyte (or greater if DRAM is used) physical address space in each of the three general purpose memory banks, and, for 50 MHz operation, provides sustained transfer rates of up to 100 Mbytes/s for SRAM, and up to 50 Mbytes/s using page-mode DRAM. The EMI includes programmable strobes to support direct interfacing to MPEG decoder devices.

#### System services module

The ST20-TP2 system services module includes:

- reset, initialization and error port,

- phase locked loop (PLL) accepts 27 MHz input and generates all the internal high frequency clocks needed for the CPU and the OS-Link,

- test access port JTAG compatible,

- low power modes.

Figure 2.2 ST20-TP2 architectural block diagram

#### Serial communications

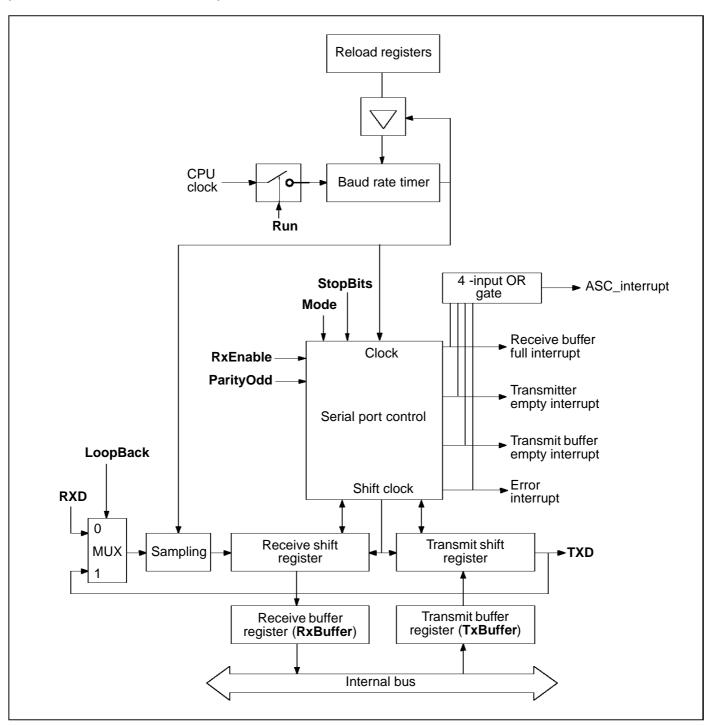

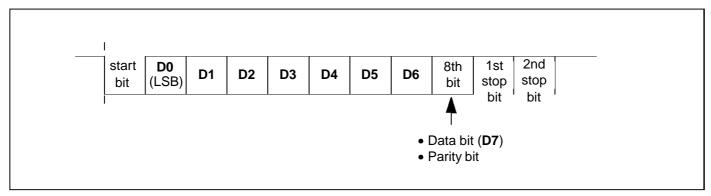

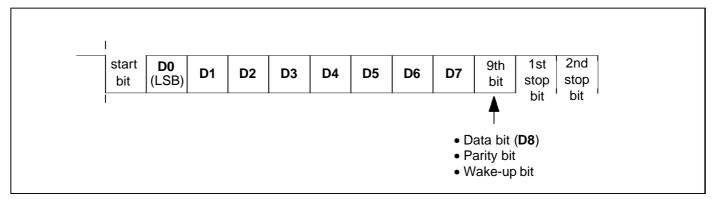

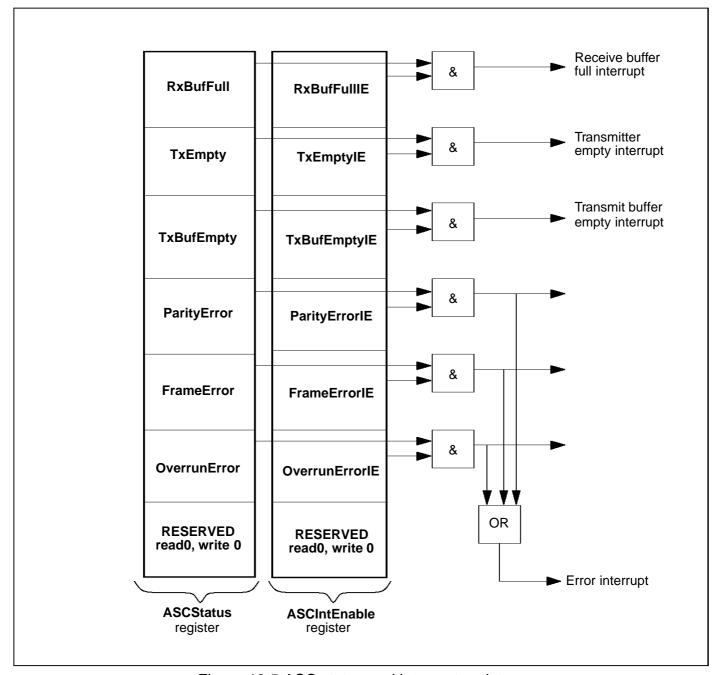

To facilitate the connection of this system to a modem for a pay-per-view type system and other peripherals, two UARTs (ASCs) are included in the device. The UARTs provide an asynchronous serial interface. The UART can be programmed to support a range of baud rates and data formats, for example, data size, stop bits and parity.

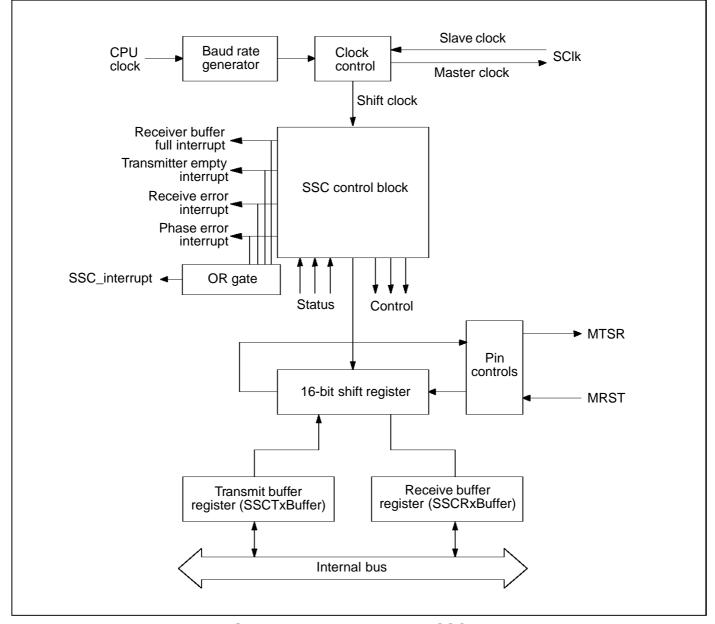

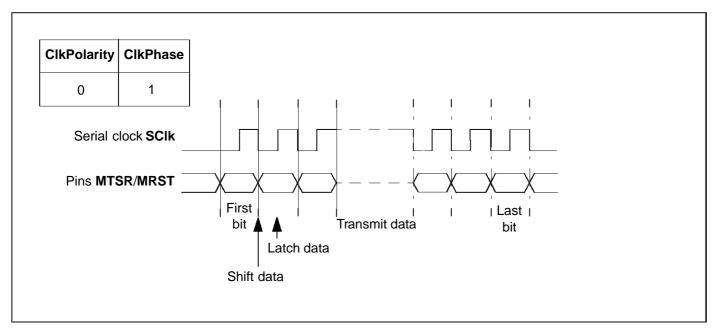

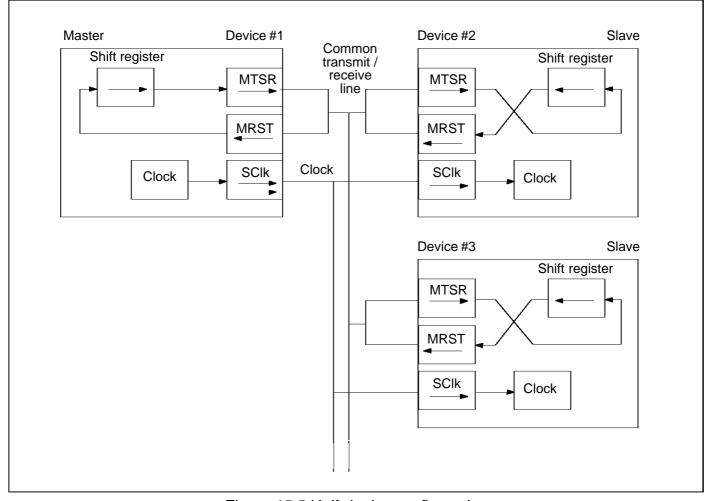

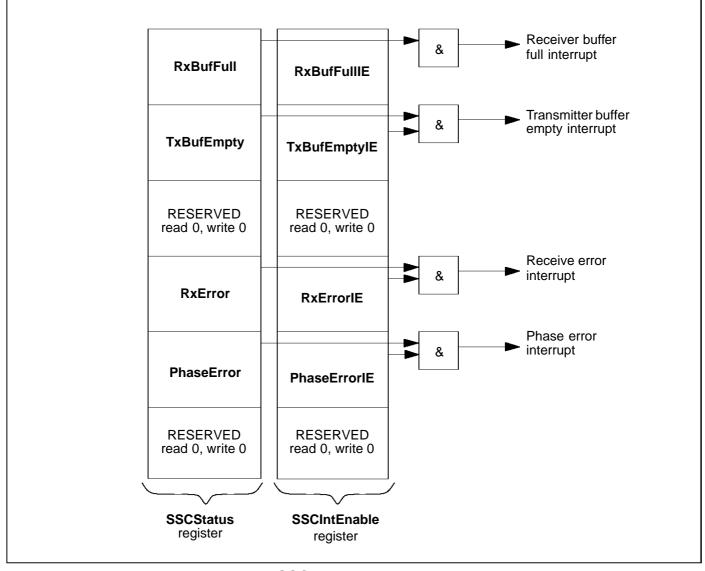

Two synchronous serial communications (SSC) interfaces are provided on the device. These can be used to control the Link-IC, PAL/NTSC encoder, and the remote control devices in the application via an I<sup>2</sup>C bus.

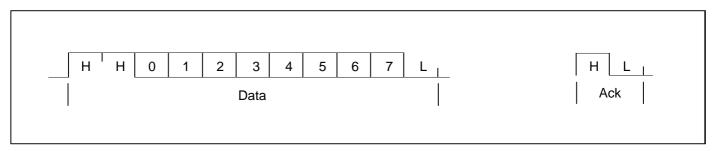

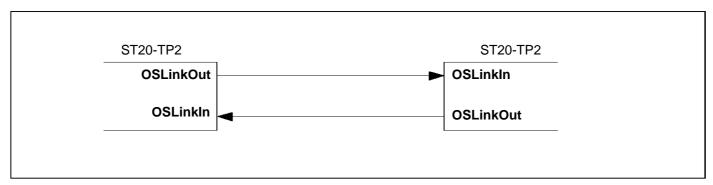

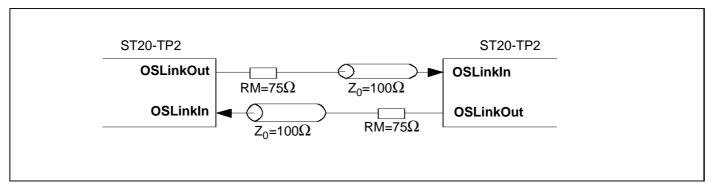

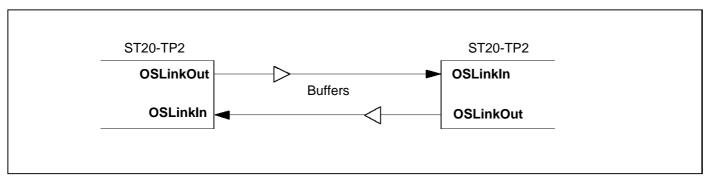

The ST20-TP2 has an OS-Link based serial communications subsystem. OS-Links use an asynchronous bit-serial (byte-stream) protocol, each bit received is sampled five times, hence the term *oversampled links* (OS-Links). Each OS-Link provides a pair of channels, one input and one output channel.

There is one OS-Link on the ST20-TP2 which acts as a DMA engine independent of the CPU. The link is used for:

- bootstrapping during development

- debugging.

#### Interrupt subsystem

The ST20-TP2 interrupt subsystem supports eight prioritized interrupt levels. Four external interrupt pins are provided. Level assignment logic allows any of the internal or external interrupts to be assigned, and if necessary share, any interrupt level.

#### Link IC interface

The Link-IC interface provides a byte wide data input from the Link-IC. The interface between the CPU and this module is provided using a channel interface allowing data transfer from the link IC to memory independently of the CPU. Using a channel interface requires a low CPU overhead at the start and end of each transfer.

#### **DVB** decryption

DVB standard decryption is supported by the DVBC module. This can be used to decrypt blocks of data from one area of memory to another using DMA operations.

#### **Block move engine**

The transfer from internal to external memory can also be performed as a memory to memory DMA operation using the block move module.

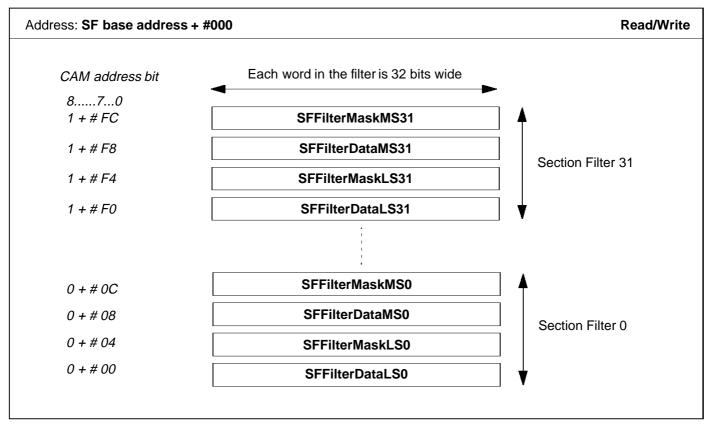

#### Section filter engine

Extraction of data contained in sections in the transport packet is supported by a section filtering engine. This contains a large bank of filters which are tested for a match against the table.id and subsequent bytes of a section. The engine is used to test each section of the packet for a match in sequence.

#### **MPEG DMA**

The two MPEG DMA controllers are used to transfer MPEG compressed data from the memory to the decoder chip. DMA strobes are provided by the EMI to support the direct connection of decoder ICs to the ST20-TP2.

#### **IEEE 1284 interface**

An 8-bit wide parallel interface (conforming to the IEEE 1284 standard) supports a high speed data input/output port to/from the set top receiver. The interface has a dedicated DMA controller to transfer data to or from memory to the port with little CPU overhead.

#### SmartCard interfaces

The SmartCard interfaces support SmartCards that are compliant with ISO7816-3 and use the asynchronous protocol. The interfaces are each implemented with a UART (ASC), dedicated programmable clock generator, and eight bits of parallel IO port.

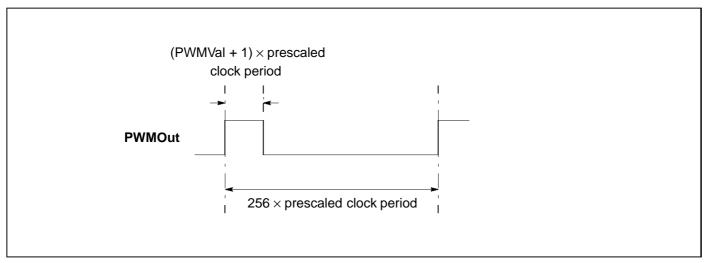

#### PWM and counter module

This unit includes two separate pulse width modulator (PWM) generators and two counters with capture registers. The counters can be clocked from a pre-scaled internal clock or from a pre-scaled external clock via the capture clock input and the event on which the timer value is captured is also programmable.

The PWM counters are 8-bit with 8-bit registers to set the output high time. The capture counters are 32-bit with 32-bit capture registers.

#### Parallel IO module

Forty bits of parallel IO are provided. Each bit is programmable as an output or an input. The output can be configured as a totem pole or open drain driver. Input compare logic is provided which can generate an interrupt on any change on any input bit.

Many pins of the ST20-TP2 device are multi-function and can either be configured as PIO or connected to an internal peripheral signal.

#### **Teletext**

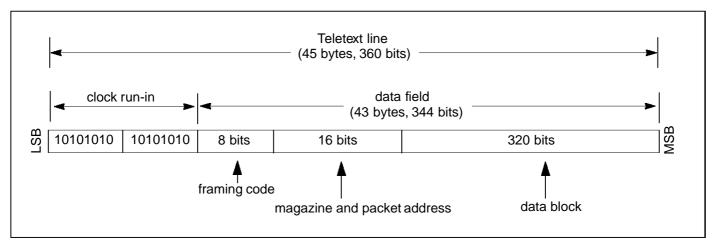

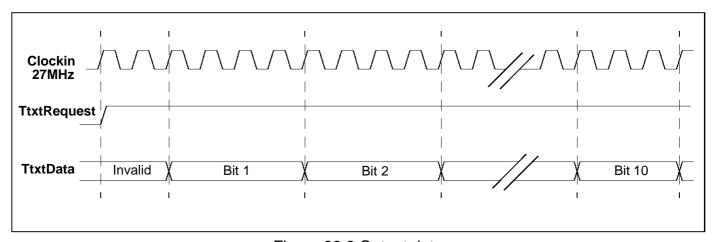

The teletext interface interfaces to a teletext peripheral. It translates teletext data to/from memory. It has two modes of operation, teletext data in and teletext data out.

In teletext data out mode, the teletext interface uses DMA to retrieve teletext data from memory, and serializes the data for transmission to a composite video encoder.

In teletext data in mode teletext data is extracted from the composite video signal and is fed into the teletext interface as a serial stream. The teletext interface assembles the data and uses DMA to pass this data to memory.

# 3 Central processing unit

The Central Processing Unit (CPU) is the ST20 32-bit processor core. It contains instruction processing logic, instruction and data pointers, and an operand register. It can directly access the high speed on-chip memory, which can store data or programs. Where larger amounts of memory are required, the processor can access memory via the External Memory Interface (EMI).

The processor provides high performance:

- Fast integer multiply 4 cycle multiply

- Fast bit shift single cycle barrel shifter

- Byte and part-word handling

- Scheduling and interrupt support

- 64-bit integer arithmetic support.

The scheduler provides a single level of pre-emption. In addition, multi-level pre-emption is provided by the interrupt subsystem, see Chapter 4 for details. Additionally, there is a per-priority trap handler to improve the support for arithmetic errors and illegal instructions, refer to section 3.6.

# 3.1 Registers

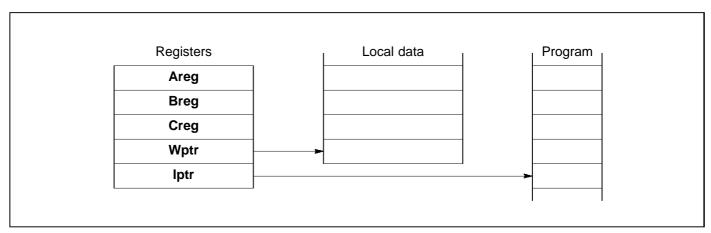

The CPU contains six registers which are used in the execution of a sequential integer process. The six registers are:

- The workspace pointer (Wptr) which points to an area of store where local data is kept.

- The instruction pointer (lptr) which points to the next instruction to be executed.

- The status register (Status).

- The Areg, Breg and Creg registers which form an evaluation stack.

The **Areg**, **Breg** and **Creg** registers are the sources and destinations for most arithmetic and logical operations. Loading a value into the stack pushes **Breg** into **Creg**, and **Areg** into **Breg**, before loading **Areg**. Storing a value from **Areg**, pops **Breg** into **Areg** and **Creg** into **Breg**. **Creg** is left undefined.

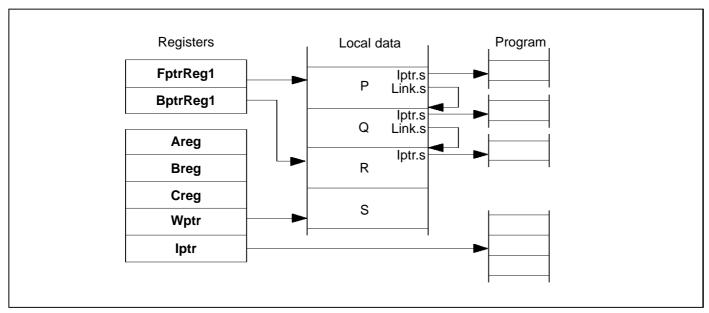

Figure 3.1 Registers used in sequential integer processes

Expressions are evaluated on the evaluation stack, and instructions refer to the stack implicitly. For example, the *add* instruction adds the top two values in the stack and places the result on the top of the stack. The use of a stack removes the need for instructions to explicitly specify the location of their operands. No hardware mechanism is provided to detect that more than three values have been loaded onto the stack; it is easy for the compiler to ensure that this never happens.

Note that a location in memory can be accessed relative to the workspace pointer, enabling the workspace to be of any size.

The use of shadow registers provides fast, simple and clean context switching.

# 3.2 Processes and concurrency

The following section describes 'default' behavior of the CPU and it should be noted that the user can alter this behavior, for example, by disabling timeslicing, installing a user scheduler, etc.

A process starts, performs a number of actions, and then either stops without completing or terminates complete. Typically, a process is a sequence of instructions. The CPU can run several processes in parallel (concurrently). Processes may be assigned either high or low priority, and there may be any number of each.

The processor has a microcoded scheduler which enables any number of concurrent processes to be executed together, sharing the processor time. This removes the need for a software kernel, although kernels can still be written if desired.

At any time, a process may be

active - bein

being executed,

interrupted by a higher priority process,

on a list waiting to be executed.

inactive - waiting to input,

waiting to output,

waiting until a specified time.

The scheduler operates in such a way that inactive processes do not consume any processor time. Each active high priority process executes until it becomes inactive. The scheduler allocates a portion of the processor's time to each active low priority process in turn (see section 3.3). Active processes waiting to be executed are held in two linked lists of process workspaces, one of high priority processes and one of low priority processes. Each list is implemented using two registers, one of which points to the first process in the list, the other to the last. In the linked process list shown in Figure 3.2, process *S* is executing and *P*, *Q* and *R* are active, awaiting execution. Only the low priority process queue registers are shown; the high priority process ones behave in a similar manner.

Figure 3.2 Linked process list

| Function                                | High priority | Low priority |

|-----------------------------------------|---------------|--------------|

| Pointer to front of active process list | FptrReg0      | FptrReg1     |

| Pointer to back of active process list  | BptrReg0      | BptrReg1     |

Table 3.1 Priority queue control registers

Each process runs until it has completed its action or is descheduled. In order for several processes to operate in parallel, a low priority process is only permitted to execute for a maximum of two timeslice periods. After this, the machine deschedules the current process at the next timeslicing point, adds it to the end of the low priority scheduling list and instead executes the next active process. The timeslice period is 1ms.

There are only certain instructions at which a process may be descheduled. These are known as descheduling points. A process may only be timesliced at certain descheduling points. These are known as timeslicing points and are defined in such a way that the operand stack is always empty. This removes the need for saving the operand stack when timeslicing. As a result, an expression evaluation can be guaranteed to execute without the process being timesliced part way through.

Whenever a process is unable to proceed, its instruction pointer is saved in the process workspace and the next process taken from the list.

The processor core provides a number of special instructions to support the process model, including *startp* (start process) and *endp* (end process). When a main process executes a parallel construct, *startp* is used to create the necessary additional concurrent processes. A *startp* instruction creates a new process by adding a new workspace to the end of the scheduling list, enabling the new concurrent process to be executed together with the ones already being executed. When a process is made active it is always added to the end of the list, and thus cannot pre-empt processes already on the same list.

The correct termination of a parallel construct is assured by use of the *endp* instruction. This uses a data structure that includes a counter of the parallel construct components which have still to ter-

minate. The counter is initialized to the number of components before the processes are started. Each component ends with an *endp* instruction which decrements and tests the counter. For all but the last component, the counter is non zero and the component is descheduled. For the last component, the counter is zero and the main process continues.

# 3.3 Priority

The following section describes 'default' behavior of the CPU and it should be noted that the user can alter this behavior, for example, by disabling timeslicing and priority interrupts.

The processor can execute processes at one of two priority levels, one level for urgent (high priority) processes, one for less urgent (low priority) processes. A high priority process will always execute in preference to a low priority process if both are able to do so.

High priority processes are expected to execute for a short time. If one or more high priority processes are active, then the first on the queue is selected and executes until it has to wait for a communication, a timer input, or until it completes processing.

If no process at high priority is active, but one or more processes at low priority are active, then one is selected. Low priority processes are periodically timesliced to provide an even distribution of processor time between computationally intensive tasks.

If there are *n* low priority processes, then the maximum latency from the time at which a low priority process becomes active to the time when it starts processing is the order of 2*n* timeslice periods. It is then able to execute for between one and two timeslice periods, less any time taken by high priority processes. This assumes that no process monopolizes the CPU's time; i.e. it has frequent timeslicing points.

The specific condition for a high priority process to start execution is that the CPU is idle or running at low priority and the high priority queue is non-empty.

If a high priority process becomes able to run whilst a low priority process is executing, the low priority process is temporarily stopped and the high priority process is executed. The state of the low priority process is saved into 'shadow' registers and the high priority process is executed. When no further high priority processes are able to run, the state of the interrupted low priority process is reloaded from the shadow registers and the interrupted low priority process continues executing. Instructions are provided on the processor core to allow a high priority process to store the shadow registers to memory and to load them from memory. Instructions are also provided to allow a process to exchange an alternative process queue for either priority process queue (see Table 6.21 on page 44). These instructions allow extensions to be made to the scheduler for custom runtime kernels.

A low priority process may be interrupted after it has completed execution of any instruction. In addition, to minimize the time taken for an interrupting high priority process to start executing, the potentially time consuming instructions are interruptible. Also some instructions are abortable and are restarted when the process next becomes active (refer to the Instruction Set chapter).

## 3.4 Process communications

Communication between processes takes place over channels, and is implemented in hardware. Communication is point-to-point, synchronized and unbuffered. As a result, a channel needs no process queue, no message queue and no message buffer.

A channel between two processes executing on the same CPU is implemented by a single word in memory; a channel between processes executing on different processors is implemented by point-to-point links. The processor provides a number of operations to support message passing, the most important being *in* (input message) and *out* (output message).

The *in* and *out* instructions use the address of the channel to determine whether the channel is internal or external. This means that the same instruction sequence can be used for both hard and soft channels, allowing a process to be written and compiled without knowledge of where its channels are implemented.

Communication takes place when both the inputting and outputting processes are ready. Consequently, the process which first becomes ready must wait until the second one is also ready. The inputting and outputting processes only become active when the communication has completed.

A process performs an input or output by loading the evaluation stack with, a pointer to a message, the address of a channel, and a count of the number of bytes to be transferred, and then executing an *in* or *out* instruction.

#### 3.5 Timers

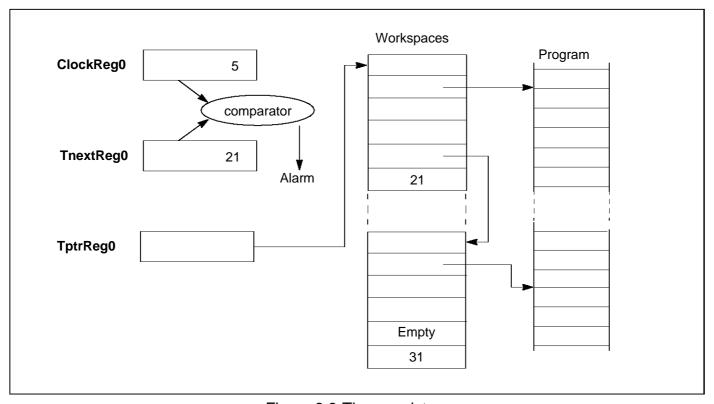

There are two 32-bit hardware timer clocks which 'tick' periodically. These are independent of any on-chip peripheral real time clock. The timers provide accurate process timing, allowing processes to deschedule themselves until a specific time.

One timer is accessible only to high priority processes and is incremented approximately every microsecond, cycling completely in approximately 4295 seconds. The other is accessible only to low priority processes and is incremented approximately every 64 microseconds, giving 15625 ticks in one second. It has a full period of approximately 76 hours. Timer frequencies are approximate and depend on the processor speed selection (see section 12.1 on page 83).

| Register  | Function                                                                 |

|-----------|--------------------------------------------------------------------------|

| ClockReg0 | Current value of high priority (level 0) process clock.                  |

| ClockReg1 | Current value of low priority (level 1) process clock.                   |

| TnextReg0 | Indicates time of earliest event on high priority (level 0) timer queue. |

| TnextReg1 | Indicates time of earliest event on low priority (level 1) timer queue.  |

| TptrReg0  | High priority timer queue.                                               |

| TptrReg1  | Low priority timer queue.                                                |

Table 3.2 Timer registers

The current value of the processor clock can be read by executing a *Idtimer* (load timer) instruction. A process can arrange to perform a *tin* (timer input), in which case it will become ready to execute after a specified time has been reached. The *tin* instruction requires a time to be specified. If this time is in the 'past' then the instruction has no effect. If the time is in the 'future' then the process is

descheduled. When the specified time is reached the process becomes active. In addition, the *Idclock* (load clock), *stclock* (store clock) instructions allow total control over the clock value and the *clockenb* (clock enable), *clockdis* (clock disable) instructions allow each clock to be individually stopped and re-started.

Figure 3.3 shows two processes waiting on the timer queue, one waiting for time 21, the other for time 31.

Figure 3.3 Timer registers

# 3.6 Traps and exceptions

A software error, such as arithmetic overflow or array bounds violation, can cause an error flag to be set in the CPU. The flag is directly connected to the **ErrorOut** pin. Both the flag and the pin can be ignored, or the CPU stopped. Stopping the CPU on an error means that the error cannot cause further corruption. As well as containing the error in this way it is possible to determine the state of the CPU and its memory at the time the error occurred. This is particularly useful for postmortem debugging where the debugger can be used to examine the state and history of the processor leading up to and causing the error condition.

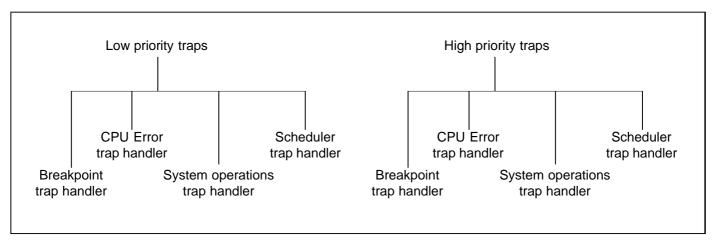

In addition, if a trap handler process is installed, a variety of traps/exceptions can be trapped and handled by software. A user supplied trap handler routine can be provided for each high/low process priority level. The handler is started when a trap occurs and is given the reason for the trap. The trap handler is not re-entrant and must not cause a trap itself within the same group. All traps are individually maskable.

#### 3.6.1 Trap groups

The trap mechanism is arranged on a per priority basis. For each priority there is a handler for each group of traps, as shown in Figure 3.4.

Figure 3.4 Trap arrangement

There are four groups of traps, as detailed below.

#### Breakpoint

This group consists of the *Breakpoint* trap. The breakpoint instruction (*j0*) calls the breakpoint routine via the trap mechanism.

#### Errors

The traps in this group are *IntegerError* and *Overflow*. *Overflow* represents arithmetic overflow, such as arithmetic results which do not fit in the result word. *IntegerError* represents errors caused when data is erroneous, for example when a range checking instruction finds that data is out of range.

#### System operations

This group consists of the *LoadTrap*, *StoreTrap* and *IllegalOpcode* traps. The *IllegalOpcode* trap is signalled when an attempt is made to execute an illegal instruction. The *LoadTrap* and *StoreTrap* traps allow a kernel to intercept attempts by a monitored process to change or examine trap handlers or trapped process information. It enables a user program to signal to a kernel that it wishes to install a new trap handler.

#### Scheduler

The scheduler trap group consists of the *ExternalChannel, InternalChannel, Timer, TimeSlice, Run, Signal, ProcessInterrupt* and *QueueEmpty* traps. The *ProcessInterrupt* trap signals that the machine has performed a priority interrupt from low to high. The *QueueEmpty* trap indicates that there is no further executable work to perform. The other traps in this group indicate that the hardware scheduler wants to schedule a process on a process queue, with the different traps enabling the different sources of this to be monitored.

The scheduler traps enable a software scheduler kernel to use the hardware scheduler to implement a multi-priority software scheduler.

Note that scheduler traps are different from other traps as they are caused by the microscheduler rather than by an executing process.

Trap groups encoding is shown in Table 3.3 below. These codes are used to identify trap groups to various instructions.

| Trap group        | Code |

|-------------------|------|

| Breakpoint        | 0    |

| CPU Errors        | 1    |

| System operations | 2    |

| Scheduler         | 3    |

Table 3.3 Trap group codes

In addition to the trap groups mentioned above, the **CauseError** flag in the **Status** register is used to signal when a trap condition has been activated by the *causeerror* instruction. It can be used to indicate when trap conditions have occurred due to the user setting them, rather than by the system.

## 3.6.2 Events that can cause traps

Table 3.4 summarizes the events that can cause traps and gives the encoding of bits in the trap **Status** and **Enable** words.

| Trap cause       | Status/Enable codes | Trap<br>group          | Comments                                                                                                                                                     |

|------------------|---------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Breakpoint       | 0                   | 0                      | When a process executes the breakpoint instruction $(j0)$ then it traps to its trap handler.                                                                 |

| IntegerError     | 1                   | 1                      | Integer error other than integer overflow - e.g. explicitly checked or explicitly set error.                                                                 |

| Overflow         | 2                   | 1                      | Integer overflow or integer division by zero.                                                                                                                |

| IllegalOpcode    | 3                   | 2                      | Attempt to execute an illegal instruction. This is signalled when opr is executed with an invalid operand.                                                   |

| LoadTrap         | 4                   | 2                      | When the trap descriptor is read with the <i>Idtraph</i> instruction or when the trapped process status is read with the <i>Idtrapped</i> instruction.       |

| StoreTrap        | 5                   | 2                      | When the trap descriptor is written with the <i>sttraph</i> instruction or when the trapped process status is written with the <i>sttrapped</i> instruction. |

| InternalChannel  | 6                   | 3                      | Scheduler trap from internal channel.                                                                                                                        |

| ExternalChannel  | 7                   | 3                      | Scheduler trap from external channel.                                                                                                                        |

| Timer            | 8                   | 3                      | Scheduler trap from timer alarm.                                                                                                                             |

| Timeslice        | 9                   | 3                      | Scheduler trap from timeslice.                                                                                                                               |

| Run              | 10                  | 3                      | Scheduler trap from runp (run process) or startp (start process).                                                                                            |

| Signal           | 11                  | 3                      | Scheduler trap from signal.                                                                                                                                  |

| ProcessInterrupt | 12                  | 3                      | Start executing a process at a new priority level.                                                                                                           |

| QueueEmpty       | 13                  | 3                      | Caused by no process active at a priority level.                                                                                                             |

| CauseError       | 15 (Status only)    | Any,<br>encoded<br>0-3 | Signals that the <i>causeerror</i> instruction set the trap flag.                                                                                            |

Table 3.4 Trap causes and **Status/Enable** codes

#### 3.6.3 Trap handlers

For each trap handler there is a trap handler structure and a trapped process structure. Both the trap handler structure and the trapped process structure are in memory and can be accessed via instructions, see section 3.6.4.

The trap handler structure specifies what should happen when a trap condition is present, see Table 3.5.

The trapped process structure saves some of the state of the process that was running when the trap was taken, see Table 3.6.

In addition, for each priority, there is an **Enables** register and a **Status** register. The **Enables** register contains flags to enable each cause of trap. The **Status** register contains flags to indicate which trap conditions have been detected. The **Enables** and **Status** register bit encodings are given in Table 3.4.

|         | Comments                                                                                                                                                                                |          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| lptr    | Iptr of trap handler process.                                                                                                                                                           | Base + 3 |

| Wptr    | Wptr of trap handler process. A null Wptr indicates that a trap handler has not been installed.                                                                                         | Base + 2 |

| Status  | Contains the <b>Status</b> register that the trap handler starts with.                                                                                                                  | Base + 1 |

| Enables | Contains a word which encodes the trap enable and global interrupt masks which will be ANDed with the existing masks to allow the trap handler to disable various events while it runs. | Base + 0 |

Table 3.5 Trap handler structure

|         | Comments                                                                |          |

|---------|-------------------------------------------------------------------------|----------|

| lptr    | Points to the instruction after the one that caused the trap condition. | Base + 3 |

| Wptr    | Wptr of the process that was running when the trap was taken.           | Base + 2 |

| Status  | The relevant trap bit is set, see Table 3.3 for trap codes.             | Base + 1 |

| Enables | Interrupt enables.                                                      | Base + 0 |

Table 3.6 Trapped process structure

A trap will be taken at an interruptible point if a trap is set and the corresponding trap enable bit is set in the **Enables** register. If the trap is not enabled then nothing is done with the trap condition. If the trap is enabled then the corresponding bit is set in the **Status** register to indicate the trap condition has occurred.

When a process takes a trap the processor saves the existing **lptr**, **Wptr**, **Status** and **Enables** in the trapped process structure. It then loads **lptr**, **Wptr** and **Status** from the equivalent trap handler structure and ANDs the value in **Enables** with the value in the structure. This allows the user to disable various events while in the handler, in particular a trap handler must disable all the traps of its trap group to avoid the possibility of a handler trapping to itself.

The trap handler then executes. The values in the trapped process structure can be examined using the *Idtrapped* instruction (see section 3.6.4). When the trap handler has completed its operation it returns to the trapped process via the *tret* (trap return) instruction. This reloads the values saved in the trapped process structure and clears the trap flag in **Status**.

Note that when a trap handler is started, **Areg**, **Breg** and **Creg** are not saved. The trap handler must save the **Areg**, **Breg**, **Creg** registers using *stl* (store local).

### 3.6.4 Trap instructions

Trap handlers and trapped processes can be set up and examined via the *Idtraph*, *sttraph*, *Idtrapped* and *sttrapped* instructions. Table 3.7 describes the instructions that may be used when dealing with traps.

| Instruction | Meaning            | Use                                                               |

|-------------|--------------------|-------------------------------------------------------------------|

| ldtraph     | load trap handler  | Load the trap handler from memory to the trap handler descriptor. |

| sttraph     | store trap handler | Store an existing trap handler descriptor to memory.              |

| Idtrapped   | load trapped       | Load replacement trapped process status from memory.              |

| sttrapped   | store trapped      | Store trapped process status to memory.                           |

| trapenb     | trap enable        | Enable traps.                                                     |

| trapdis     | trap disable       | Disable traps.                                                    |

| tret        | trap return        | Used to return from a trap handler.                               |

| causeerror  | cause error        | Program can simulate the occurrence of an error.                  |

Table 3.7 Instructions which may be used when dealing with traps

The first four instructions transfer data to/from the trap handler structures or trapped process structures from/to an area in memory. In these instructions **Areg** contains the trap group code (see Table 3.3) and **Breg** points to the 4 word area of memory used as the source or destination of the transfer. In addition **Creg** contains the priority of the handler to be installed/examined in the case of *Idtraph* or *sttraph*. *Idtrapped* and *sttrapped* apply only to the current priority.

If the *LoadTrap* trap is enabled then *Idtraph* and *Idtrapped* do not perform the transfer but set the **LoadTrap** trap flag. If the *StoreTrap* trap is enabled then *sttraph* and *sttrapped* do not perform the transfer but set the **StoreTrap** trap flag.

The trap enable masks are encoded by an array of bits (see Table 3.4) which are set to indicate which traps are enabled. This array of bits is stored in the lower half-word of the **Enables** register. There is an **Enables** register for each priority. Traps are enabled or disabled by loading a mask into **Areg** with bits set to indicate which traps are to be affected and the priority to affect in **Breg**. Executing *trapenb* ORs the mask supplied in **Areg** with the trap enables mask in the **Enables** register for the priority in **Breg**. Executing *trapdis* negates the mask supplied in **Areg** and ANDs it with the trap enables mask in the **Enables** register for the priority in **Breg**. Both instructions return the previous value of the trap enables mask in **Areg**.

#### 3.6.5 Restrictions on trap handlers

There are various restrictions that must be placed on trap handlers to ensure that they work correctly.

- 1 Trap handlers must not deschedule or timeslice. Trap handlers alter the **Enables** masks, therefore they must not allow other processes to execute until they have completed.

- 2 Trap handlers must have their **Enable** masks set to mask all traps in their trap group to avoid the possibility of a trap handler trapping to itself.

- 3 Trap handlers must terminate via the *tret* (trap return) instruction. The only exception to this is that a scheduler kernel may use *restart* to return to a previously shadowed process.

# 4 Interrupt controller

The ST20-TP2 supports external interrupts, enabling an on-chip subsystem or external interrupt pin to interrupt the currently running process in order to run an interrupt handling process.

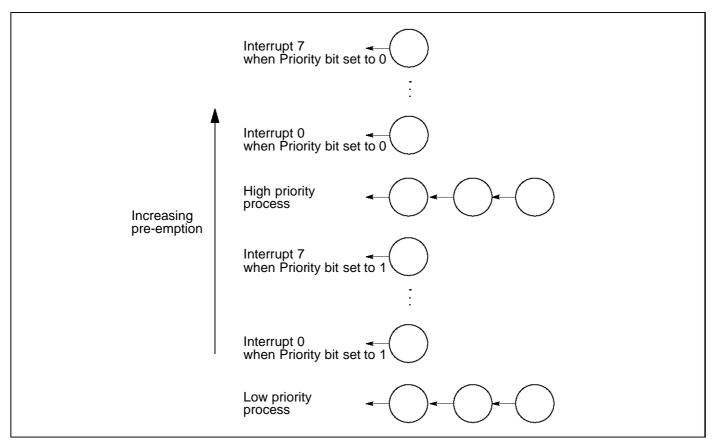

The ST20-TP2 interrupt subsystem supports eight prioritized interrupts. In addition, there is an interrupt level controller (refer to Chapter 5) which multiplexes incoming interrupts onto the eight programmable interrupt levels. This multiplexing is controllable by software.

Note: Interrupts (Interrupt0-7) which are specified as higher priority must be contiguous from the highest numbered interrupt downwards, i.e. if 4 interrupts are programmed as higher priority and 4 as lower priority the higher priority interrupts must be Interrupt7:4 and the lower priority interrupts Interrupt3:0.

Figure 4.1 Interrupt priority

Interrupts on the ST20-TP2 are implemented via an on-chip interrupt controller peripheral. An interrupt can be signalled to the controller by one of the following:

- a signal on an external Interrupt pin

- a signal from an internal peripheral or subsystem

- software asserting an interrupt in the **Pending** register

# 4.1 Interrupt vector table

The interrupt controller contains a table of pointers to interrupt handlers. Each interrupt handler is represented by its workspace pointer (**Wptr**). The table contains a workspace pointer for each level of interrupt.

The **Wptr** gives access to the code, data and interrupt save space of the interrupt handler. The position of the **Wptr** in the interrupt table implies the priority of the interrupt.

Run-time library support is provided for setting and programming the vector table.

# 4.2 Interrupt handlers

At any interruptible point in its execution the CPU can receive an interrupt request from the interrupt controller. The CPU immediately acknowledges the request.

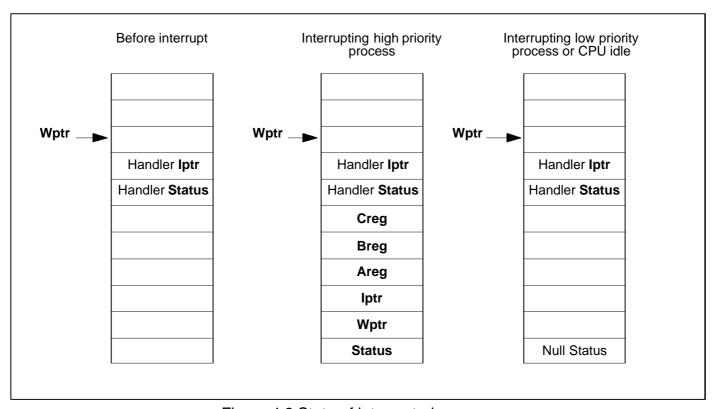

In response to receiving an interrupt the CPU performs a procedure call to the process in the vector table. The state of the interrupted process is stored in the workspace of the interrupt handler as shown in Figure 4.2. Each interrupt level has its own workspace.

Figure 4.2 State of interrupted process

The interrupt routine is initialized with space below **Wptr**. The **lptr** and **Status** word for the routine are stored there permanently. This should be programmed before the **Wptr** is written into the vector table. The behavior of the interrupt differs depending on the priority of the CPU when the interrupt occurs.

When an interrupt occurs when the CPU was running at high priority, and the interrupt is set at a higher priority than the high priority process queue, the CPU saves the current process state (Areg, Breg, Creg, Wptr, lptr and Status) into the workspace of the interrupt handler. The value

**HandlerWptr**, which is stored in the interrupt controller, points to the top of this workspace. The values of **Iptr** and **Status** to be used by the interrupt handler are loaded from this workspace and starts executing the handler. The value of **Wptr** is then set to the bottom of this save area.

When an interrupt occurs when the CPU was running at high priority, and the interrupt is set at a lower priority than the high priority process queue, no action is taken and the interrupt waits in a queue until all higher priority interrupts have been serviced (see section 4.4).

Interrupts always take priority over low priority processes. When an interrupt occurs when the CPU was idle or running at low priority, the **Status** is saved. This indicates that no valid process is running (*Null Status*). The interrupted processes (low priority process) state is stored in shadow registers. This state can be accessed via the *Idshadow* (load shadow registers) and *stshadow* (store shadow registers) instructions. The interrupt handler is then run at high priority.

When the interrupt routine has completed it must adjust **Wptr** to the value at the start of the handler code and then execute the *iret* (interrupt return) instruction. This restores the interrupted state from the interrupt handler structure and signals to the interrupt controller that the interrupt has completed. The processor will then continue from where it was before being interrupted.

# 4.3 Interrupt latency

The interrupt latency is dependent on the data being accessed and the position of the interrupt handler and the interrupted process. This allows systems to be designed with the best trade-off use of fast internal memory and interrupt latency.

# 4.4 Preemption and interrupt priority

Each interrupt channel has an implied priority fixed by its place in the interrupt vector table. All interrupts will cause scheduled processes of any priority to be suspended and the interrupt handler started. Once an interrupt has been sent from the controller to the CPU the controller keeps a record of the current executing interrupt priority. This is only cleared when the interrupt handler executes a return from interrupt (*iret*) instruction. Interrupts of a lower priority arriving will be blocked by the interrupt controller until the interrupt priority has descended to such a level that the routine will execute. An interrupt of a higher priority than the currently executing handler will be passed to the CPU and cause the current handler to be suspended until the higher priority interrupt is serviced.

In this way interrupts can be nested and a higher priority interrupt will always pre-empt a lower priority one. Deep nesting and placing frequent interrupts at high priority can result in a system where low priority interrupts are never serviced or the controller and CPU time are consumed in nesting interrupt priorities and not executing the interrupt handlers.

# 4.5 Restrictions on interrupt handlers

There are various restrictions that must be placed on interrupt handlers to ensure that they interact correctly with the rest of the process model implemented in the CPU.

- 1 Interrupt handlers must not deschedule.

- 2 Interrupt handlers must not execute communication instructions. However they may com-

municate with other processes through shared variables using the semaphore *signal* to synchronize.

- 3 Interrupt handlers must not perform block move instructions.

- 4 Interrupt handlers must not cause program traps. However they may be trapped by a scheduler trap.

# 4.6 Interrupt configuration register s

The interrupt controller is allocated a 4k block of memory in the internal peripheral address space. Information on interrupts is stored in registers as detailed in the following section. The registers can be examined and set by the *devlw* (device load word) and *devsw* (device store word) instructions. Note, they can not be accessed using memory instructions.

### HandlerWptr register

The **HandlerWptr** registers (1 per interrupt) contain a pointer to the workspace of the interrupt handler. It also contains the **Priority** bit which determines whether the interrupt is at a higher or lower priority than the high priority process queue.

Note, before the interrupt is enabled, by writing a 1 in the **Mask** register, the user (or toolset) must ensure that there is a valid **Wptr** in the register.

| HandlerWptr |             | Interrupt controller base address + #00 to #1C Read/Write                                                                                                                                                                       |

|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Bit field   | Function                                                                                                                                                                                                                        |

| 0           | Priority    | Sets the priority of the interrupt. If this bit is set to 0, the interrupt is a higher priority than the high priority process queue, if this bit is 1, the interrupt is a lower priority than the high priority process queue. |

|             |             | 0 high priority 1 low priority                                                                                                                                                                                                  |

| 31:2        | HandlerWptr | Pointer to the workspace of the interrupt handler.                                                                                                                                                                              |

| 1           |             | Reserved, write 0.                                                                                                                                                                                                              |

Table 4.1 HandlerWptr register format - one register per interrupt

#### TriggerMode register

Each interrupt channel can be programmed to trigger on rising/falling edges or high/low levels on the external **Interrupt**.

| TriggerMode |           | Interrupt con                                                          | troller base address + #40 to #5C                | Read/Write |

|-------------|-----------|------------------------------------------------------------------------|--------------------------------------------------|------------|

| Bit         | Bit field | Function                                                               |                                                  |            |

| 2:0 Trigger |           | Control the triggering condition of the <b>Interrupt</b> , as follows: |                                                  |            |

|             |           | Trigger2:0                                                             | Interrupt triggers on                            |            |

|             |           | 000                                                                    | No trigger mode                                  |            |

|             |           | 001                                                                    | High level - triggered while input high          |            |

|             |           | 010                                                                    | Low level - triggered while input low            |            |

|             |           | 011                                                                    | Rising edge - low to high transition             |            |

|             |           | 100                                                                    | Falling edge - high to low transition            |            |

|             |           | 101                                                                    | Any edge - triggered on rising and falling edges |            |

|             |           | 110                                                                    | No trigger mode                                  |            |

|             |           | 111                                                                    | No trigger mode                                  |            |

Table 4.2 **TriggerMode** register format - one register per interrupt

Note, level triggering is different to edge triggering in that if the input is held at the triggering level, a continuous stream of interrupts is generated.

#### Mask register

An interrupt mask register is provided in the interrupt controller to selectively enable or disable external interrupts. This mask register also includes a global interrupt disable bit to disable all external interrupts whatever the state of the individual interrupt mask bits.

To complement this the interrupt controller also includes an interrupt pending register which contains a pending flag for each interrupt channel. The **Mask** register performs a masking function on the **Pending** register to give control over what is allowed to interrupt the CPU while retaining the ability to continually monitor external interrupts.

On start-up, the **Mask** register is initialized to zeros, thus all interrupts are disabled, both globally and individually. When a 1 is written to the **GlobalEnable** bit, the individual interrupt bits are still

disabled and must also have a 1 individually written to the **InterruptEnable** bit to enable the respective interrupt.

| Mask |                                                                                                                                                   | Interrupt controller base address + #C0                                               | Read/Write |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------|

| Bit  | Bit field                                                                                                                                         | Function                                                                              |            |

| 0    | Interrupt0Enable                                                                                                                                  | When set to 1, interrupt 0 is enabled. When 0, interrupt 0 is disabled.               |            |

| 1    | Interrupt1Enable                                                                                                                                  | When set to 1, interrupt 1 is enabled. When 0, interrupt 1 is disabled.               |            |

| 2    | Interrupt2Enable                                                                                                                                  | When set to 1, interrupt 2 is enabled. When 0, interrupt 2 is disabled.               |            |

| 3    | Interrupt3Enable                                                                                                                                  | errupt3Enable When set to 1, interrupt 3 is enabled. When 0, interrupt 3 is disabled. |            |

| 4    | Interrupt4Enable                                                                                                                                  | When set to 1, interrupt 4 is enabled. When 0, interrupt 4 is disabled.               |            |

| 5    | Interrupt5Enable                                                                                                                                  | When set to 1, interrupt 5 is enabled. When 0, interrupt 5 is disabled.               |            |

| 6    | Interrupt6Enable                                                                                                                                  | When set to 1, interrupt 6 is enabled. When 0, interrupt 6 is disabled.               |            |

| 7    | Interrupt7Enable When set to 1, interrupt 7 is enabled. When 0, interrupt 7 is disabled.                                                          |                                                                                       |            |

| 16   | GlobalEnable  When set to 1, the setting of the interrupt is determined by the specific InterruptEnable bit. When 0, all interrupts are disabled. |                                                                                       |            |

| 15:8 |                                                                                                                                                   | Reserved, write 0.                                                                    |            |

Table 4.3 Mask register format

The **Mask** register is mapped onto two additional addresses so that bits can be set or cleared individually.

**Set\_Mask** (address 'interrupt base address + #C4') allows bits to be set individually. Writing a '1' in this register sets the corresponding bit in the **Mask** register, a '0' leaves the bit unchanged.

**Clear\_Mask** (address 'interrupt base address + #C8') allows bits to be cleared individually. Writing a '1' in this register resets the corresponding bit in the **Mask** register, a '0' leaves the bit unchanged.

### **Pending register**

The **Pending** register contains a bit per interrupt with each bit controlled by the corresponding interrupt. A read can be used to examine the state of the interrupt controller while a write can be used to explicitly trigger an interrupt.

A bit is set when the triggering condition for an interrupt is met. All bits are independent so that several bits can be set in the same cycle. Once a bit is set, a further triggering condition will have no effect. The triggering condition is independent of the **Mask** register.

The highest priority interrupt bit is reset once the interrupt controller has made an interrupt request to the CPU.

The interrupt controller receives external interrupt requests and makes an interrupt request to the CPU when it has a pending interrupt request of higher priority than the currently executing interrupt handler.

| Pending |             | Interrupt controller base address + #80 | Read/Write |

|---------|-------------|-----------------------------------------|------------|

| Bit     | Bit field   | Function                                |            |

| 0       | PendingInt0 | Interrupt 0 pending bit.                |            |

| 1       | PendingInt1 | Interrupt 1 pending bit.                |            |

| 2       | PendingInt2 | Interrupt 2 pending bit.                |            |

| 3       | PendingInt3 | Interrupt 3 pending bit.                |            |

| 4       | PendingInt4 | Interrupt 4 pending bit.                |            |

| 5       | PendingInt5 | Interrupt 5 pending bit.                |            |

| 6       | PendingInt6 | Interrupt 6 pending bit.                |            |

| 7       | PendingInt7 | Interrupt 7 pending bit.                |            |

Table 4.4 Bit fields in the **Pending** register

The **Pending** register is mapped onto two additional addresses so that bits can be set or cleared individually.

**Set\_Pending** (address 'interrupt base address + #84') allows bits to be set individually. Writing a '1' in this register sets the corresponding bit in the **Pending** register, a '0' leaves the bit unchanged.

**Clear\_Pending** (address 'interrupt base address + #88') allows bits to be cleared individually. Writing a '1' in this register resets the corresponding bit in the **Pending** register, a '0' leaves the bit unchanged.

Note, if the CPU wants to write or clear some bits of the **Pending** register, the interrupts should be masked (by writing or clearing the **Mask** register) before writing or clearing the **Pending** register. The interrupts can then be unmasked.

#### **Exec register**

The **Exec** register keeps track of the currently executing and pre-empted interrupts. A bit is set when the CPU starts running code for that interrupt. The highest priority interrupt bit is reset once the interrupt handler executes a return from interrupt (*iret*).

| Exec |                | Interrupt controller base address + #100                   | Read/Write |

|------|----------------|------------------------------------------------------------|------------|

| Bit  | Bit field      | Function                                                   |            |

| 0    | Interrupt0Exec | Set to 1 when the CPU starts running code for interrupt 0. |            |

| 1    | Interrupt1Exec | Set to 1 when the CPU starts running code for interrupt 1. |            |

| 2    | Interrupt2Exec | Set to 1 when the CPU starts running code for interrupt 2. |            |

| 3    | Interrupt3Exec | Set to 1 when the CPU starts running code for interrupt 3. |            |

| 4    | Interrupt4Exec | Set to 1 when the CPU starts running code for interrupt 4. |            |

| 5    | Interrupt5Exec | Set to 1 when the CPU starts running code for interrupt 5. |            |

| 6    | Interrupt6Exec | Set to 1 when the CPU starts running code for interrupt 6. |            |

| 7    | Interrupt7Exec | Set to 1 when the CPU starts running code for interrupt 7. |            |

Table 4.5 Bit fields in the **Exec** register

The **Exec** register is mapped onto two additional addresses so that bits can be set or cleared individually.

**Set\_Exec** (address 'interrupt base address + #104') allows bits to be set individually. Writing a '1' in this register sets the corresponding bit in the **Exec** register, a '0' leaves the bit unchanged.

**Clear\_Exec** (address 'interrupt base address + #108') allows bits to be cleared individually. Writing a '1' in this register resets the corresponding bit in the **Exec** register, a '0' leaves the bit unchanged.

# 5 Interrupt level controller

The interrupt level controller extends the number of possible interrupts to eighteen.

There are 18 interrupts (of which 4 are external) generated in the ST20-TP2 system and each of these is assigned to one of the interrupt controller's 8 inputs. Thus each of the interrupt controller's inputs responds to zero or more of the 18 system interrupts.

An interrupt handler routine is able to ascertain the source of an interrupt where two or more system interrupts are assigned to one handler by doing a device read from the **InputInterrupts** register (see Table 5.2) and examining the bits that correspond to the system interrupts assigned to that handler.

The assignment of interrupts to peripherals and external pins is given in the *Device Configuration* chapter.

The interrupt level controller has additional functionality to support the low power controller. The external interrupts are monitored and a signal is generated for the low power controller which tells it when any of them goes to a pre-determined level. This level is programmable for each external interrupt, and in addition each interrupt can be selectively masked.

# 5.1 Interrupt level controller registers

The interrupt level controller is programmable via configuration registers. These registers can be examined and set by the *devlw* (device load word) and *devsw* (device store word) instructions.

### **IntPriority registers**

The priority assigned to each of the input interrupts is programmable via the **IntPriority** registers.

The interrupt level controller asserts interrupt output *N* when one or more of the input interrupts with programmed priority equal to *N* are high. It is level sensitive and re-timed at the input, thus incurring one cycle of latency.

| IntPriority I   |           | Interrupt level co | ontroller base address + #00 to #44 | Read/Write |

|-----------------|-----------|--------------------|-------------------------------------|------------|

| Bit             | Bit field | Function           |                                     |            |

| 2:0 IntPriority |           | Determines the     |                                     |            |

|                 |           | IntPriority2:0     | Asserts output interrupt            |            |

|                 |           | 000                | 0 (lowest priority)                 |            |

|                 |           | 001                | 1                                   |            |

|                 |           | 010                | 2                                   |            |

|                 |           | 011                | 3                                   |            |

|                 |           | 100                | 4                                   |            |

|                 |           | 101                | 5                                   |            |

|                 |           | 110                | 6                                   |            |

|                 |           | 111                | 7 (highest priority)                |            |

Table 5.1 **IntPriority** register format - 1 register per interrupt

#### InputInterrupts register

The **InputInterrupts** register is a read only register. It contains a vector which shows all of the input interrupts, so bit 0 of the read data corresponds to **InterruptIn0**, bit 1 corresponds to **InterruptIn1**, etc.

| Inputinterrupts |                 | Interrupt level controller base address + #44 + #04 | Read only |

|-----------------|-----------------|-----------------------------------------------------|-----------|

| Bit             | Bit field       | Function                                            |           |

| 17:0            | InterruptIn17-0 | Input interrupt levels.                             |           |

Table 5.2 InputInterrupts register format

#### Selectnotlnv

Each of the four external interrupts can be programmed to be not inverting or inverting, depending on whether the interrupt is active high or active low.

| SelectnotInv |              | Interrupt level controller base address + #44 + #08 | Read/Write |

|--------------|--------------|-----------------------------------------------------|------------|

| Bit          | Bit field    | Function                                            |            |

| 3:0          | Selectnotlnv | External interrupt sense for low power controller.  |            |

Table 5.3 **Selectnotinv** register format

#### **ExtIntEnable**

The **ExtIntEnable** register enables each of the four external interrupts to be selectively enabled or disabled.

| ExtIntEnable |              | nterrupt level controller base address + #44 + #0C  | Read/Write |

|--------------|--------------|-----------------------------------------------------|------------|

| Bit          | Bit field    | Function                                            |            |

| 3:0          | ExtIntEnable | Enable external interrupt for low power controller. |            |

Table 5.4 ExtIntEnable register format

# 6 Instruction set

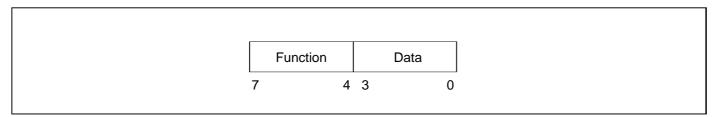

This chapter provides information on the instruction set. It contains tables listing all the instructions, and where applicable provides details of the number of processor cycles taken by an instruction.

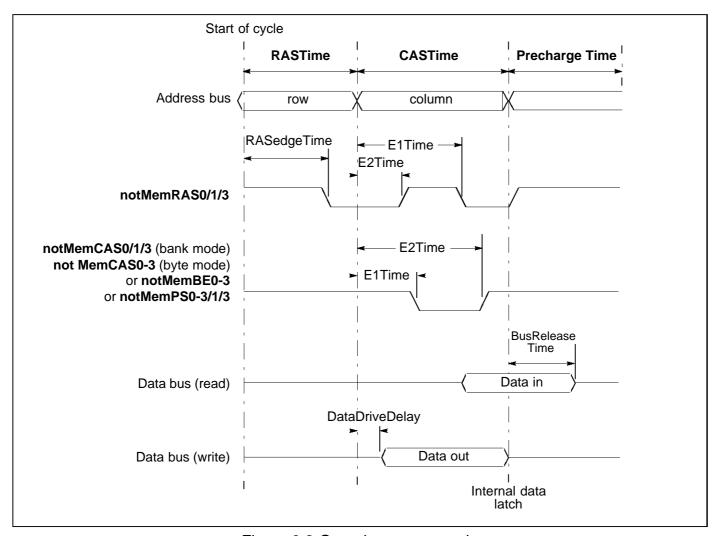

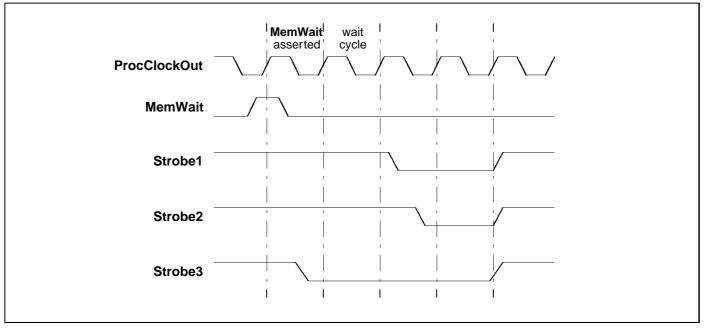

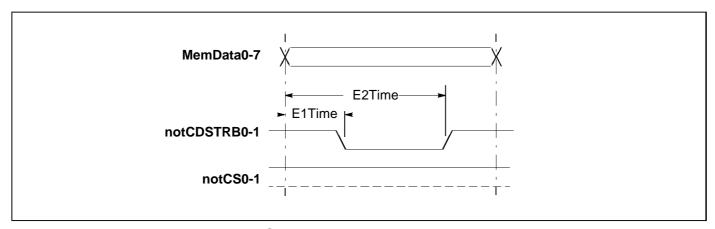

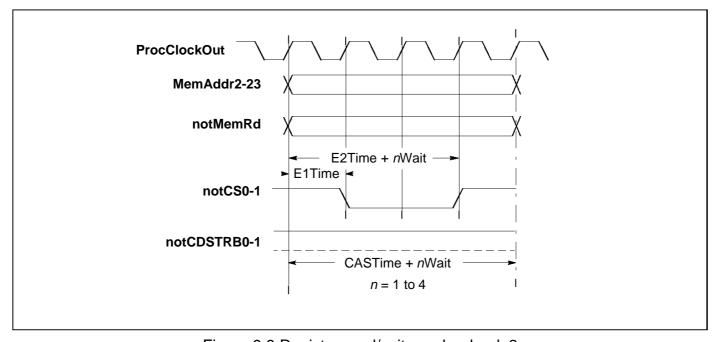

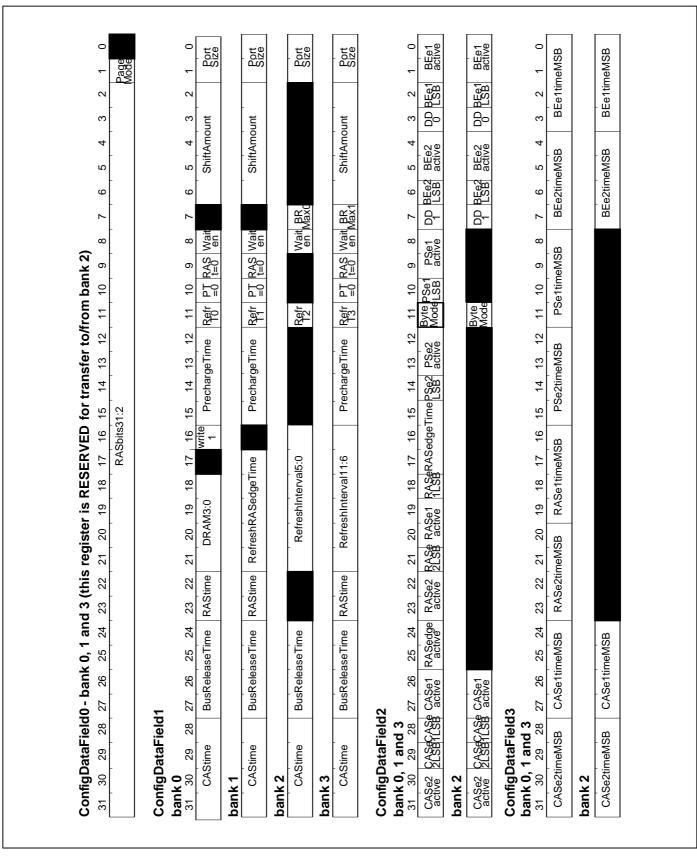

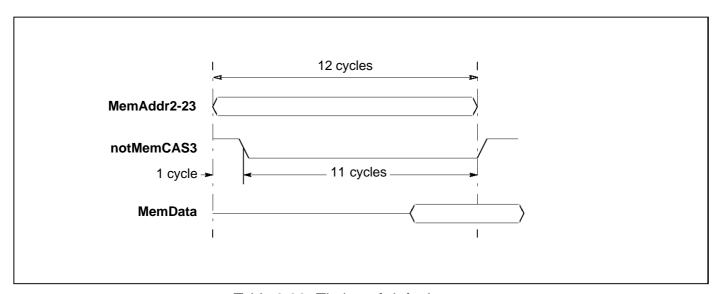

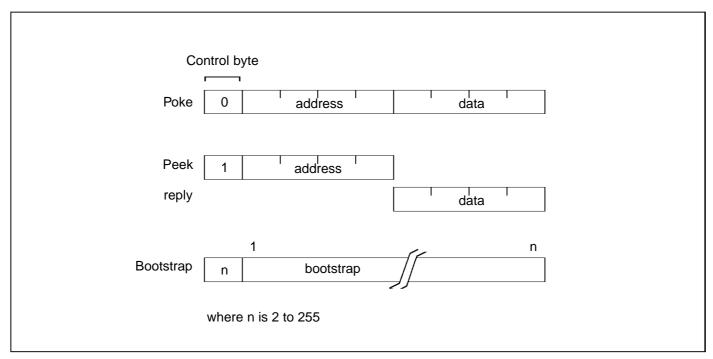

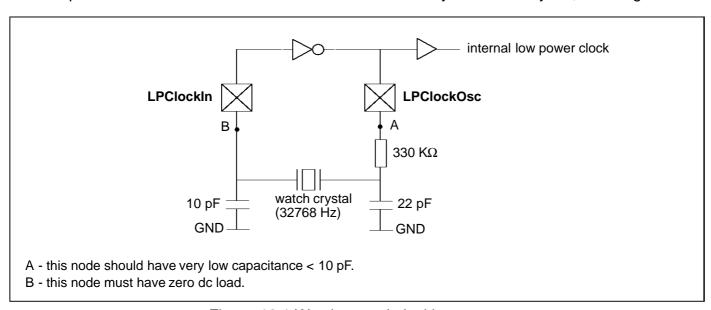

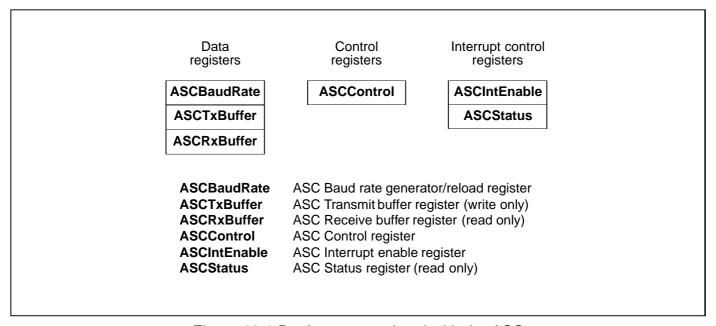

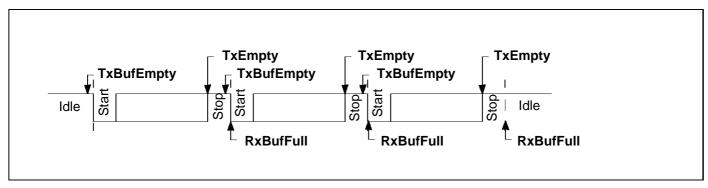

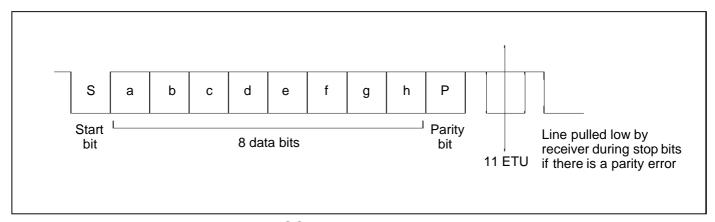

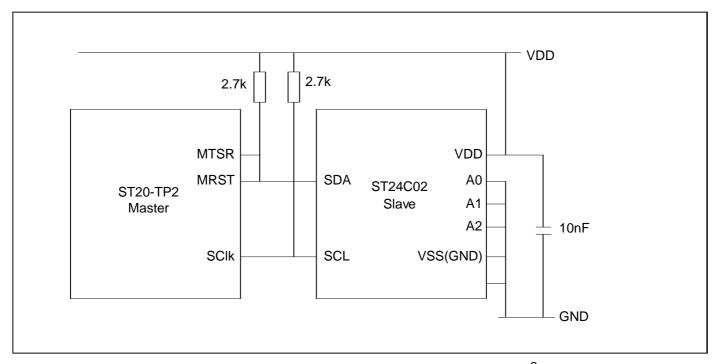

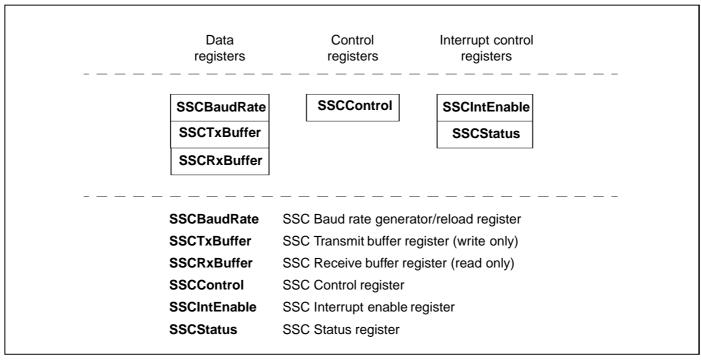

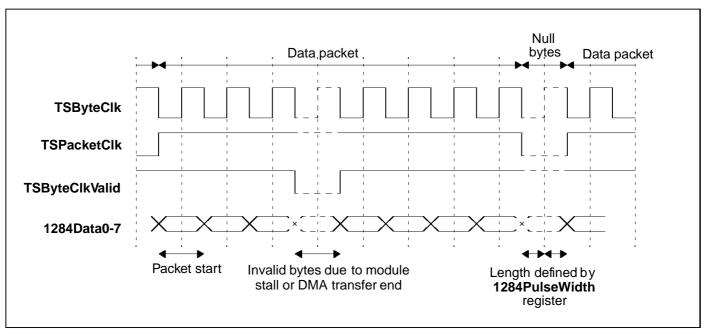

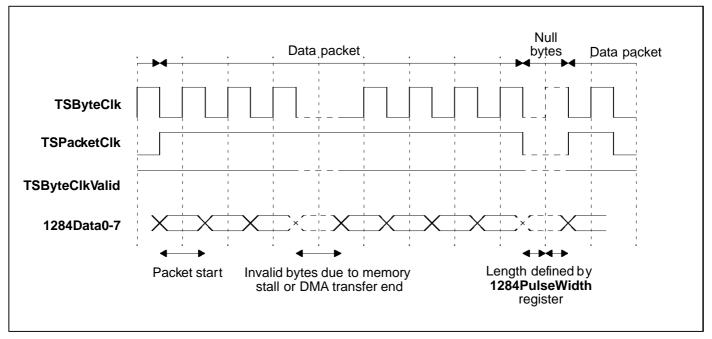

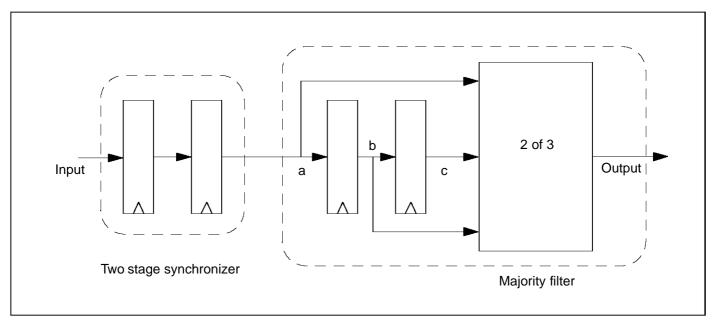

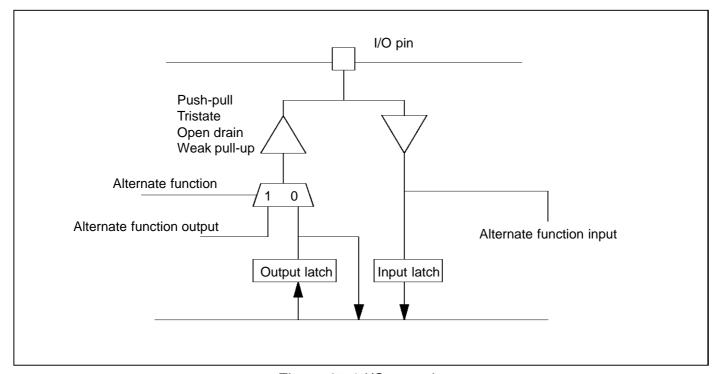

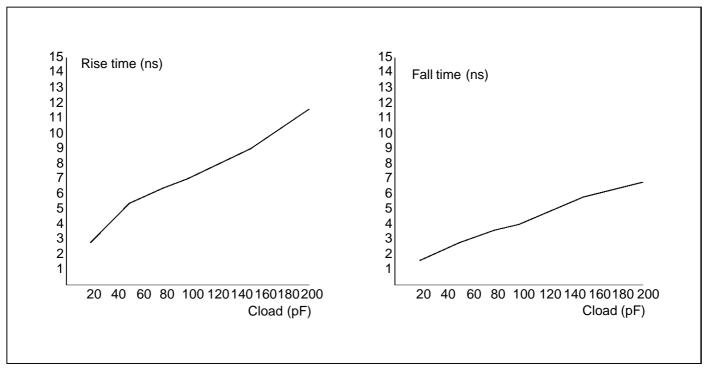

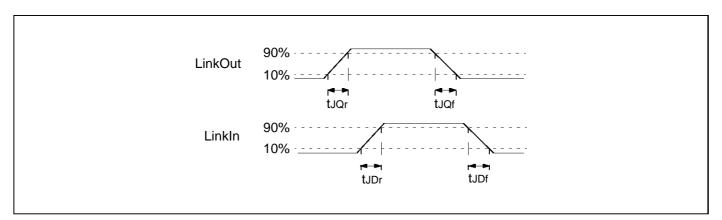

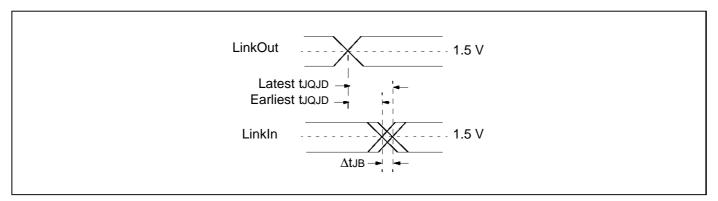

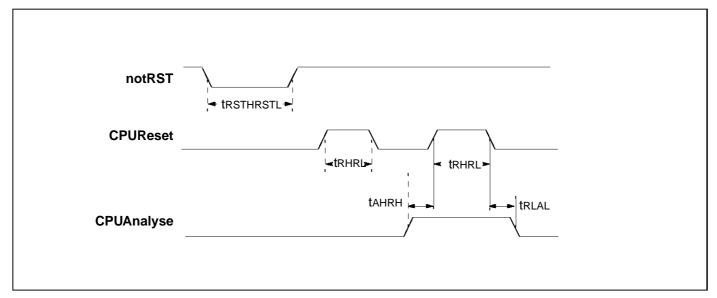

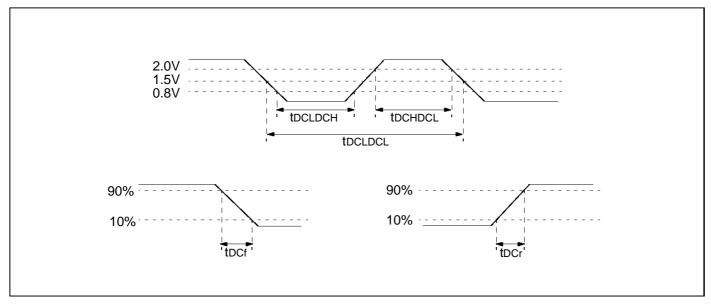

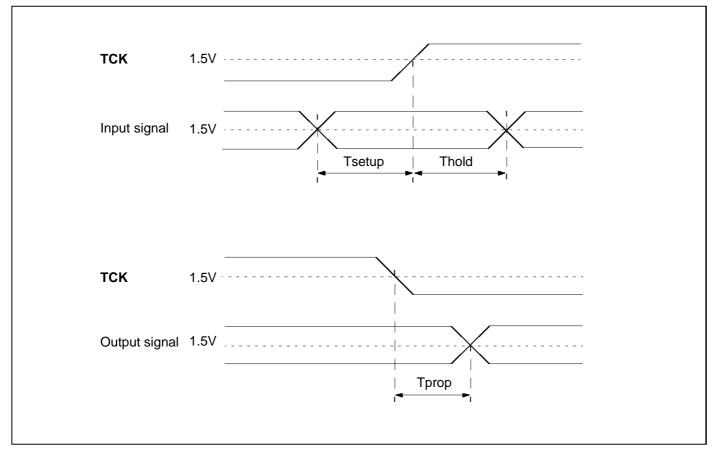

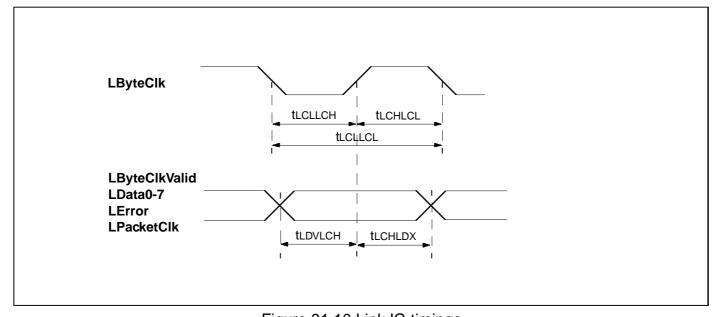

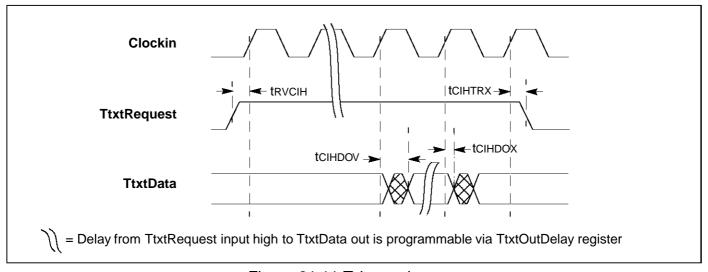

The instruction set has been designed for simple and efficient compilation of high-level languages. All instructions have the same format, designed to give a compact representation of the operations occurring most frequently in programs.