C-Programmable Controller User's Manual

Revision D

## PK2500 User's Manual

Part Number 019-0063 • Revision D Last revised on February 11, 2000 • Printed in U.S.A.

## Copyright

© 1999 Z-World, Inc. • All rights reserved.

Z-World reserves the right to make changes and improvements to its products without providing notice.

## Trademarks

- Dynamic  $C^{^{(0)}}$  is a registered trademark of Z-World, Inc.

- Windows<sup>®</sup> is a registered trademark of Microsoft Corporation

- $PLCBus^{TM}$  is a trademark of Z-World, Inc.

## Notice to Users

When a system failure may cause serious consequences, protecting life and property against such consequences with a backup system or safety device is essential. The buyer agrees that protection against consequences resulting from system failure is the buyer's responsibility.

This device is not approved for life-support or medical systems.

All Z-World products are 100 percent functionally tested. Additional testing may include visual quality control inspections or mechanical defects analyzer inspections. Specifications are based on characterization of tested sample units rather than testing over temperature and voltage of each unit. Z-World may qualify components to operate within a range of parameters that is different from the manufacturer's recommended range. This strategy is believed to be more economical and effective. Additional testing or burn-in of an individual unit is available by special arrangement.

## **Company Address**

#### Z-World, Inc.

2900 Spafford Street Davis, California 95616-6800 USA

Telephone: (530)757-3737 Facsimile: (530)753-5141 Web Site: http://www.zworld.com E-Mail: zworld@zworld.com

23

| Chapter 1: <b>Overview</b>                | 11 |

|-------------------------------------------|----|

| PK2500 Overview                           | 12 |

| Features                                  | 13 |

| Core Module                               | 13 |

| Other Features                            | 13 |

| Optional Accessories                      | 14 |

| Software Development and Evaluation Tools | 14 |

| CE Compliance                             | 15 |

|                                           |    |

| Chapter 2: Getting Started                        | 17 |

|---------------------------------------------------|----|

| Initial PK2500 Setup                              |    |

| Parts Required                                    |    |

| Connecting the PK2500 to a Host PC                |    |

| Running Dynamic C                                 |    |

| Test the Communication Line                       | 20 |

| Selecting Communications Rate, Port, and Protocol |    |

| Running a Sample Program                          |    |

| Chapter 3: | Input/Output | Configuration |

|------------|--------------|---------------|

|------------|--------------|---------------|

| PK2500 Inputs and Outputs                            | 24 |

|------------------------------------------------------|----|

| Flexible Inputs/Outputs                              |    |

| Configuring Serial Communications                    | 27 |

| Configuring Inputs and Outputs                       | 28 |

| Protected Digital Inputs vs. High-Current Outputs    | 28 |

| RS-485 vs. Protected Digital Inputs                  | 29 |

| A/D Converter Input vs. A/D Voltage Reference Output | 29 |

| PK2500 Subsystems                                    | 30 |

| Chapter 4: System Development        | 31 |

|--------------------------------------|----|

| PK2500 Operating Modes               | 32 |

| Changing the PK2500's Operating Mode |    |

| Running a Program                    | 34 |

| Using Digital Inputs/Outputs                  |

|-----------------------------------------------|

| Protected Digital Inputs                      |

| How to Read the Inputs                        |

| High-Current Outputs                          |

| How to Use the Outputs                        |

| Serial Communication                          |

| RS-232 Communication                          |

| RS-232 Connector Pinouts                      |

| RS-485 Network                                |

| Termination and Bias Resistors                |

| Relay Outputs                                 |

| How to Use the Relay Outputs                  |

| Analog-to-Digital Converter Inputs 46         |

| Scaling Input Range                           |

| Theory of Operation                           |

| The VOFF Voltage Divider                      |

| DC Gain                                       |

| Finding VOFF                                  |

| Practical Considerations                      |

| Input Impedance                               |

| Frequency Response                            |

| How to Use the Analog-to-Digital Converter 55 |

| Using the Analog Inputs 55                    |

| Using the A/D Voltage Reference               |

| Additional Features                           |

| Pulse-Width Modulated (PWM) Outputs 57        |

| How to Use the PWM Feature 57                 |

| User-Programmable LEDs 60                     |

| Real-Time Clock (RTC)                         |

| Power Supervisor                              |

| +5 V Output                                   |

## Chapter 5: Software Reference

| 1                                          |    |

|--------------------------------------------|----|

| Input/Output Software Drivers              | 64 |

| Digital Inputs/Outputs                     | 64 |

| Level-Sensitive Interrupts                 |    |

| Interrupt Service Routines                 |    |

| Pulse-Width Modulation Outputs             |    |

| References to Additional Software Features |    |

|                                            |    |

#### 63

| Advanced Input/Output Programming                         | . 70 |

|-----------------------------------------------------------|------|

| Digital Input Addressing Details                          |      |

| Digital Output and Relay Output Addressing Details        | . 72 |

| Analog-to-Digital Converter Addressing Details            | . 73 |

| LED Addressing Details                                    | . 74 |

| RS-485 Driver Addressing Details                          | 74   |

| PWM Addressing Details                                    | . 74 |

| PWM Advanced Programming Functions                        | . 78 |

| Appendix A: Troubleshooting                               | 81   |

| Out of the Box                                            | . 82 |

| Dynamic C Will Not Start                                  |      |

| Dynamic C Loses Serial Link                               |      |

| PK2500 Repeatedly Resets                                  |      |

| Common Programming Errors                                 |      |

| Appendix B: Specifications                                | 85   |

| Electrical and Mechanical Specifications                  |      |

| Factory Default Jumper Positions                          |      |

| Protected Digital Inputs                                  |      |

| Frequency Response for IN-00 to IN-05, and IN-08 to IN-15 |      |

| Frequency Response for IN-06 and IN-07                    |      |

| Customization                                             |      |

| Frequency Response and Input Range                        |      |

| Default Pull-Up Assignments                               |      |

| High-Current Drivers                                      |      |

| "KA" and "KB"                                             |      |

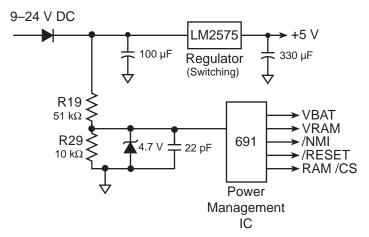

| Appendix C: Power Management                              | 95   |

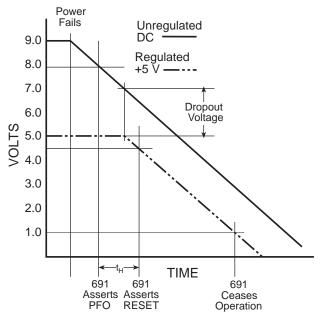

| Power Failure Sequence of Events                          | . 96 |

| Power-Failure Detection Circuitry                         |      |

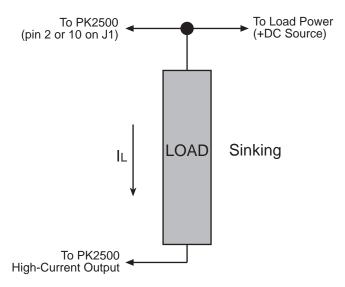

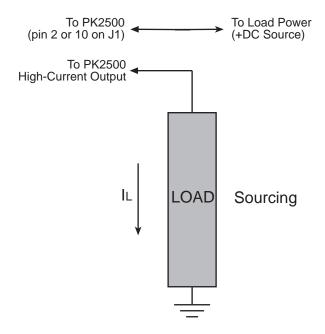

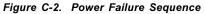

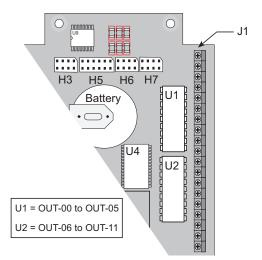

| Appendix D: Sinking vs. Sourcing Drivers                  | 99   |

| Selecting Sourcing or Sinking Drivers                     | 101  |

| Sinking Driver (Low-Side Drive)                           |      |

| Sourcing Driver (High-Side Drive)                         |      |

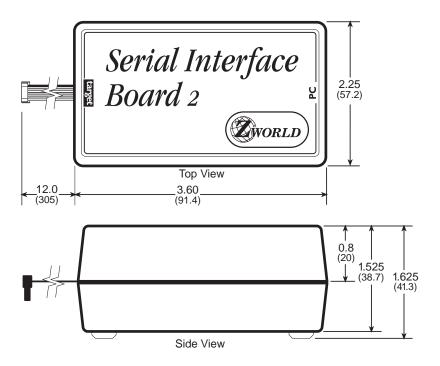

| Appendix E: Serial Interface Board 2                      | 03   |

| Introduction                                              | 104  |

| External Dimensions                                       |      |

|                                                           |      |

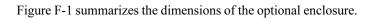

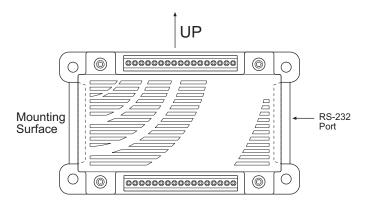

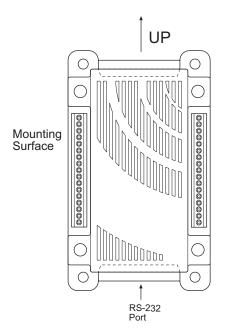

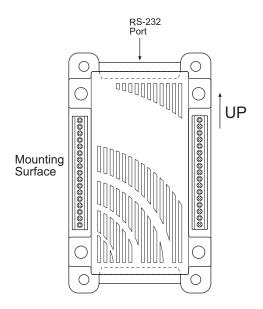

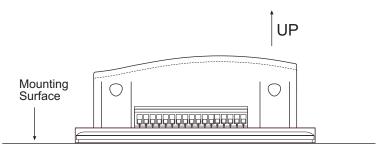

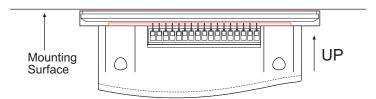

| Appendix F: Enclosure Mounting                 | 107 |

|------------------------------------------------|-----|

| Appendix G: Nonvolatile Storage                | 111 |

| Appendix H: I/O Map and Interrupt Vectors      | 113 |

| PK2500 Input/Output Map                        | 114 |

| Real-Time Clock Registers                      |     |

| Other Input/Output Addresses                   | 117 |

| Interrupt Vectors                              |     |

| Interrupt Priorities                           |     |

| Appendix I: Battery                            | 121 |

| Storage Conditions and Shelf Life              | 122 |

| Instructions for Replacing the Lithium Battery | 122 |

| Battery Cautions                               |     |

|                                                |     |

#### Index

125

# ABOUT THIS MANUAL

This manual provides instructions for installing, testing, configuring, and interconnecting the Z-World PK2500 controller. Instructions are also provided for using Dynamic  $C^{\text{(B)}}$  functions.

#### Assumptions

Assumptions are made regarding the user's knowledge and experience in the following areas.

- Ability to design and engineer the target system that a PK2500 will control.

- Understanding of the basics of operating a software program and editing files under Windows on a PC.

- Knowledge of the basics of C programming.

$\bigcirc$  For a full treatment of C, refer to the following texts.

*The C Programming Language* by Kernighan and Ritchie and/or

C: A Reference Manual by Harbison and Steel

• Knowledge of basic Z80 assembly language and architecture.

$\bigcirc$  For documentation from Zilog, refer to the following texts.

Z180 MPU User's Manual Z180 Serial Communication Controllers Z80 Microprocessor Family User's Manual

### Acronyms

Table 1 lists and defines the acronyms that may be used in this manual.

| Acronym | Meaning                                                                   |

|---------|---------------------------------------------------------------------------|

| EPROM   | Erasable Programmable Read-Only Memory                                    |

| EEPROM  | Electronically Erasable Programmable Read-Only Memory                     |

| LCD     | Liquid Crystal Display                                                    |

| LED     | Light-Emitting Diode                                                      |

| NMI     | Nonmaskable Interrupt                                                     |

| PIO     | Parallel Input/Output Circuit<br>(Individually Programmable Input/Output) |

| PRT     | Programmable Reload Timer                                                 |

| RAM     | Random Access Memory                                                      |

| RTC     | Real-Time Clock                                                           |

| SIB     | Serial Interface Board                                                    |

| SRAM    | Static Random Access Memory                                               |

| UART    | Universal Asynchronous Receiver Transmitter                               |

Table 1. Acronyms

### lcons

Table 2 displays and defines icons that may be used in this manual.

| lcon         | Meaning         | lcon | Meaning      |

|--------------|-----------------|------|--------------|

| <del>6</del> | Refer to or see |      | Note         |

| T            | Please contact  | Tip  | Tip          |

| $\triangle$  | Caution         | A    | High Voltage |

|              | Factory Default |      |              |

Table 2. Icons

## Conventions

Table 3 lists and defines the typographic conventions that may be used in this manual.

| Example   | Description                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| while     | Courier font (bold) indicates a program, a fragment of a program, or a Dynamic C keyword or phrase.                                                  |

| // IN-01  | Program comments are written in Courier font, plain face.                                                                                            |

| Italics   | Indicates that something should be typed instead of the italicized words (e.g., in place of <i>filename</i> , type a file's name).                   |

| Edit      | Sans serif font (bold) signifies a menu or menu selection.                                                                                           |

|           | An ellipsis indicates that (1) irrelevant program text is<br>omitted for brevity or that (2) preceding program text may<br>be repeated indefinitely. |

| []        | Brackets in a C function's definition or program segment indicate that the enclosed directive is optional.                                           |

| < >       | Angle brackets occasionally enclose classes of terms.                                                                                                |

| a   b   c | A vertical bar indicates that a choice should be made from among the items listed.                                                                   |

Table 3. Typographic Conventions

#### Pin Number 1

A black square indicates pin 1 of all headers.

#### Measurements

All diagram and graphic measurements are in inches followed by millimeters enclosed in parenthesis. Blank

## CHAPTER 1: **OVERVIEW**

Chapter 1 provides a comprehensive overview and description of the PK2500. The following sections are included.

- PK2500 Overview

- Features

- Flexibility and Customization

- Optional Accessories

- Software Development and Evaluation Tools

- CE Compliance

## PK2500 Overview

The PK2500 is a small, powerful, and extremely flexible system controller. The PK2500 consists of a main board with a core module to provide the processing power. The core module provides the processor, real time clock, supervisor, memory, and control of the various inputs/outputs.

A rugged enclosure houses the PK2500. The base plate is compatible with multiple mounting options, including DIN rail.

The PK2500 is programmed using Dynamic C, Z-World's version of the C programming language.

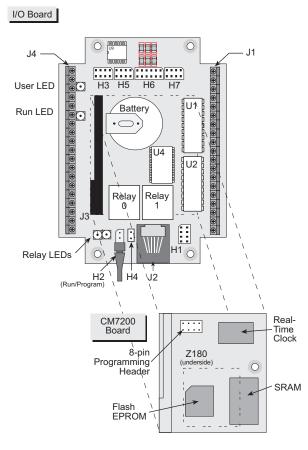

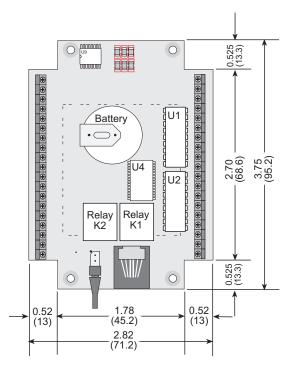

Figure 1-1 illustrates the PK2500 component layout.

Figure 1-1. PK2500 Component Layout (Top View, Case Removed)

## Features

The PK2500 offers the following features.

#### Core Module

• Z180 microprocessor operating at 18.432 MHz, 128K SRAM, and 128K flash EPROM.

The core module used on the PK2500 is a CM7200 that has been modified to include a header at location H1 on the CM7200. The BIOS is also different from that supplied with regular stock CM7200s.

#### Other Features

- Thirty pins (out of the 38 total) are available for assigning various I/O combinations. One RJ-12 modular jack is also provided for RS-232 communication.

- Factory-configured with 10 protected digital inputs, two of which have software-assignable level-sensitive interrupts, and two of which may be configured as an RS-485 serial port. Up to six additional protected digital inputs are available by changing the configuration of the high-current outputs.

- Factory-configured with 12 high-current driver outputs in two banks of six each. The outputs normally have sinking drivers, but sinking and optional sourcing drivers may be mixed between the two banks for push-pull or H-bridge operation. Three of the outputs on each of the two banks may be configured as protected digital inputs.

- Four 12-bit analog/digital converter inputs.

- Two SPST relay outputs.

- Two RS-232 serial communication ports are available. One RS-485 serial port is available by reconfiguring two protected digital inputs.

- One bank of six of the digital outputs can optionally provide pulsewidth modulation under software control.

- Switching +5 V voltage regulator with some excess capacity for external loads.

- Two programmable LEDs.

- Quick-disconnect screw terminal blocks with a 3.5 mm pitch.

Table 1-1 lists the versions of the PK2500 that are available.

| Model  | Features                                                    |  |  |

|--------|-------------------------------------------------------------|--|--|

| PK2500 | Standard full-featured model                                |  |  |

| PK2510 | PK2500 with 9.216 MHz clock, 32K SRAM, and fixed connectors |  |  |

Table 1-1. PK2500 Series Features

The PK2500 is also available without the enclosure.

The PK2500 was designed with flexibility in mind. Nine of the input/output assignments are assignable via jumpers, allowing quick tailoring to specific I/O configurations.

The circuit layout of the PK2500 has been optimized for quick-turn custom manufacturing. Automated surface-mount manufacturing can deliver a PK2500 controller with the *exact* hardware configuration required by the application.

$\triangle$  Appendix B provides detailed specifications for the PK2500.

## **Optional Accessories**

The following accessories are available for the PK2500.

- Development Kit containing manual with schematics, programming cable, AC adapter, and sourcing high-current driver chip.

- DIN Rail mounting kit.

- Sourcing driver kit.

- Serial Interface Board 2 to allow programming through a special programming port, leaving the serial channels available for the application.

For ordering information, or for more details about the various options and prices, call your Z-World Sales Representative at (530)757-3737.

## Software Development and Evaluation Tools

Dynamic C, Z-World's Windows-based real-time C language development system, is used to develop software for the PK2500. The host PC down-loads the executable code through the Serial Interface Board 2 or one of the serial ports to the flash EPROM.

Z-World's Dynamic C reference manuals provide complete software descriptions and programming instructions.

## **CE** Compliance

The PK2500 has been tested by an approved competent body, and was found to be in conformity with applicable EN and equivalent standards. Note the following requirements for incorporating the PK2500 in your application to comply with CE requirements.

# CE

- The power supply provided with the Development Kit if for development purposes only. It is the customer's responsibility to provide a clean DC supply to the controller for all applications in end-products.

- The PK2500 has been tested to Light Industrial Immunity standards. Additional shielding or filtering may be required for an industrial environment.

- The PK2500 has been tested to EN55022 Class A emission standards. Additional shielding or filtering may be required to meet Class B emission standards.

Visit the "Technical Reference" pages of the Z-World Web site at http://www.zworld.com for more information on shielding and filtering.

#### Blank

# CHAPTER 2: GETTING STARTED

Chapter 2 provides instructions for connecting the PK2500 to a host PC, and running a sample program. The following sections are included.

- Initial PK2500 Setup

- Connecting the PK2500 to a Host PC

- Running Dynamic C

- Running a Sample Program

## Initial PK2500 Setup

#### Parts Required

- 12 V, 500 mA unregulated DC power supply

- Programming cable

## Connecting the PK2500 to a Host PC

The PK2500 may be programmed directly through its serial port or through a Serial Interface Board 2 (SIB2).

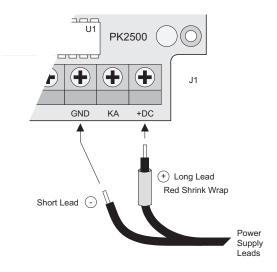

1. Connect the power supply to the +DC and GND terminals as shown in Figure 2-1.

Figure 2-1. Power Supply Connections

Do not plug the transformer into the wall until all the connections and jumpers have been set.

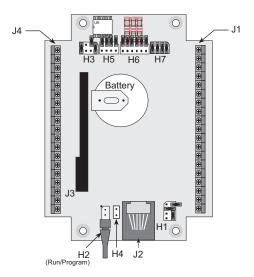

If a transformer other than the one supplied with the Developer's Kit is used, ensure that the input voltage specifications (9 V to 40 V DC) are not exceeded. Appendix B contains complete specifications for the PK2500. 2. Ensure that the Run/Program jumper (H2) is installed as shown in Figure 2-2.

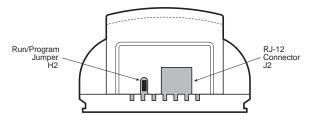

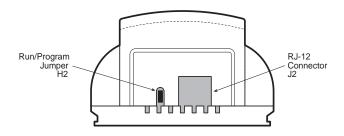

Figure 2-2. H2 Run/Program Jumper Location

Pay particular attention to the installation of the Run/Program jumper at H2. It is possible to install the jumper so that the pins are not connected. The PK2500 will not change modes if this jumper is installed incorrectly.

3. Establish a serial communication link

#### Option 1—Via RS-232 Serial Port

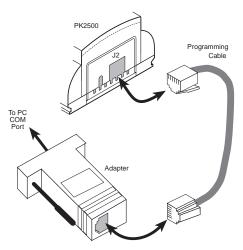

Use the adapter and the programming cable supplied with the developer's kit to connect the PK2500's RJ-12 (J2) socket to the appropriate computer COM port as shown in Figure 2-3.

Figure 2-3. Programming Connections to RS-232 Port

Use the programming cable supplied with the Developer's Kit to avoid problems with mismatched plugs.

#### Option 2—Via Optional Serial Interface Board 2 (SIB2)

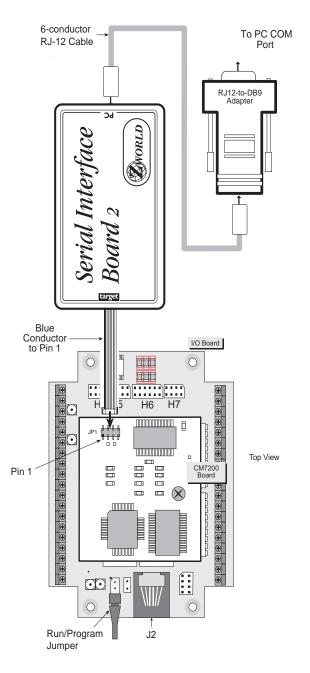

The SIB2 is an optional development tool that allows both serial ports to be available to an application. The PK2500 uses a Z-World CM7200 core module as the microprocessor core. The CM7200 has an additional programming port, JP1, that connects to the SIB via a 2 mm, 8-pin connector, bypassing the PK2500's RJ-12 modular jack (J2).

Connect an RJ-12 cable between the SIB2 and the RJ-12/DB9 adapter attached to the host PC (see Figure 2-4).

Plug the SIB2's 8-pin connector into header JP1 located on the CM7200.

Observe the polarity of the cable used to connect the SIB2 to JP1. The side of the cable closest to Pin 1 is marked in blue, as indicated in Figure 2-4.

4. The PK2500 is now ready for programming. The transformer may be plugged in.

## **Running Dynamic C**

#### Test the Communication Line

Double-click the Dynamic C icon to start the software. Note that the PC attempts to communicate with the PK2500 each time Dynamic C is started. No error messages are displayed once communication is established.

See Appendix A, "Troubleshooting," if an error message such as **Target Not Responding** or **Communication Error** appears.

Once the necessary changes have been made to establish communication between the host PC and the PK2500, use the Dynamic C shortcut **<Ctrl Y>** to reset the controller and initiate communication.

Figure 2-4. Programming Connections to Serial Interface Board 2

#### Selecting Communications Rate, Port, and Protocol

The communication rate, port, and protocol are all selected by choosing **Serial Options** from the Dynamic C **OPTIONS** menu.

The PK2500 supports a communication baud rate up to 57,600 bps. However, the Dynamic C software shipped by Z-World may be initialized for a different baud rate. To begin, select a communication rate of 57,600 bps. A slower rate may be required, in which case the PK2500 should be reset with a **<Ctrl Y>** after the lower rate is selected. The SIB2 automatically adjusts to the PC's communication baud rate to 9600 bps, 19,200 bps, 28,800 bps, or 57,600 bps.

Make sure that the PC serial port used to connect the serial cable (COM1 or COM2) is the one selected in the Dynamic C **OPTIONS** menu. Select the 1-stop-bit protocol.

## **Running a Sample Program**

The sample program **FLASHLED**. **C** is supplied in the Dynamic C **SAMPLES**\**PK25xx** subdirectory. This program flashes the LED on the board.

Prior to running this test, be sure to set the communications parameters in Dynamic C so that the PC and the PK2500 are handshaking properly.

- 1. Compile the program by pressing **F3** or by choosing **Compile** from the **COMPILE** menu. Dynamic C compiles and downloads the program.

- 2. Run the program by pressing **F9** or by choosing **Run** from the **RUN** menu. The LEDs on the PK2500 will begin flashing at differing rates.

- 4. Press **<Ctrl Z>** to stop execution of the program.

- 5. If needed, press **F9** to restart execution of the program.

The Dynamic C **SAMPLES\PK25xx** subdirectory contains other sample programs that illustrate the features of the PK2500. These programs may be used as a basis for new applications.

## CHAPTER 3:

# INPUT/OUTPUT CONFIGURATION

Chapter 3 describes the built-in flexibility of the PK2500 controller and describes how to configure the available inputs/outputs. The following sections are included.

- PK2500 Inputs and Outputs

- Configuring Serial Communications

- Configuring Inputs and Outputs

- PK2500 Subsystems

## PK2500 Inputs and Outputs

The PK2500 provides six types of inputs/outputs (I/O).

- Protected digital inputs

- High-current driver outputs

- Analog to digital converter inputs

- Serial communication channels

- Relay outputs

- LEDs

#### Flexible Inputs/Outputs

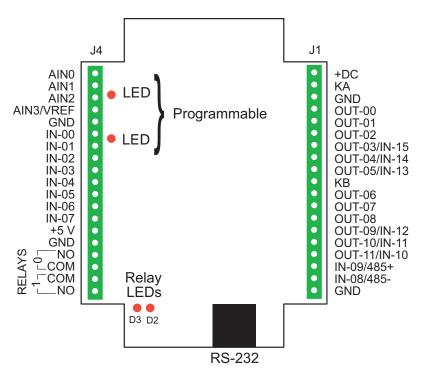

The PK2500 has 30 pins dedicated to I/O. Some pins have fixed functions, others can be configured using jumpers. The inputs and outputs may be mixed and matched to suit a particular application. Figure 3-1 shows the signal names for the pins and Table 3-1 and Table 3-2 list all possible I/O function combinations.

Figure 3-1. PK2500 Pinout

| Pin | Label        | Function 1                 | Function 2<br>(user assignable)                                         |

|-----|--------------|----------------------------|-------------------------------------------------------------------------|

| 1   | AIN0         | A/D Converter Input 0      | n/a                                                                     |

| 2   | AIN1         | A/D Converter Input 1      | n/a                                                                     |

| 3   | AIN2         | A/D Converter Input 2      | n/a                                                                     |

| 4   | AIN3/VREF    | A/D Converter Input 3      | A/D Voltage Reference<br>Output                                         |

| 5   | GND          | Analog Ground              | n/a                                                                     |

| 6   | IN-00        | Protected Digital Input 0  | n/a                                                                     |

| 7   | IN-01        | Protected Digital Input 1  | n/a                                                                     |

| 8   | IN-02        | Protected Digital Input 2  | n/a                                                                     |

| 9   | IN-03        | Protected Digital Input 3  | n/a                                                                     |

| 10  | IN-04        | Protected Digital Input 4  | n/a                                                                     |

| 11  | IN-05        | Protected Digital Input 5  | n/a                                                                     |

| 12  | IN-06        | Protected Digital Input 6  | Protected Digital Input 6<br>with level-sensitive<br>interrupt (/INT0)* |

| 13  | IN-07        | Protected Digital Input 7  | Protected Digital Input 7<br>with level-sensitive<br>interrupt (/INT1)* |

| 14  | +5 V         | +5 V                       | n/a                                                                     |

| 15  | GND          | Ground                     | n/a                                                                     |

| 16  | RELAYS-0-NO  | Relay 0, normally open n/a |                                                                         |

| 17  | RELAYS-0-COM | Relay 0, common            | n/a                                                                     |

| 18  | RELAYS-1-COM | Relay 1, common n/a        |                                                                         |

| 19  | RELAYS-1-NO  | Relay 2, normally open     | n/a                                                                     |

Table 3-1. PK2500 Header J4 I/O Functions

\* These interrupts are software-assignable. See Chapter 5, "Software Reference," for further details.

| Pin | Label        | Function 1                                     | Function 2<br>(user assignable)   |

|-----|--------------|------------------------------------------------|-----------------------------------|

| 1   | +DC          | Power Supply Input                             | n/a                               |

| 2   | KA           | High-Current Driver 0-5<br>Supply              | n/a                               |

| 3   | GND          | Ground n/a                                     |                                   |

| 4   | OUT-00       | High-Current Output 0 n/a                      |                                   |

| 5   | OUT-01       | High-Current Output 1 n/a                      |                                   |

| 6   | OUT-02       | High-Current Output 2 n/a                      |                                   |

| 7   | OUT-03/IN-15 | High-Current Output 3                          | Protected Digital Input 15        |

| 8   | OUT-04/IN-14 | High-Current Output 4                          | Protected Digital Input 14        |

| 9   | OUT-05/IN-13 | High-Current Output 5                          | Protected Digital Input 13        |

| 10  | KB           | High Current Driver 6-11 supply                | n/a                               |

| 11  | OUT-06       | High-Current Output 6                          | n/a                               |

| 12  | OUT-07       | High-Current Output 7 n/a                      |                                   |

| 13  | OUT-08       | High-Current Output 8                          | n/a                               |

| 14  | OUT-09/IN-12 | High-Current Output 9 Protected Digital In     |                                   |

| 15  | OUT-10/IN-11 | High-Current Output 10 Protected Digital Input |                                   |

| 16  | OUT-11/IN-10 | High-Current Output 11 Protected Digital Input |                                   |

| 17  | IN-09/485+   | Protected Digital Input 09                     | +RS-485 Serial Commu-<br>nication |

| 18  | IN-08/485-   | Protected Digital Input 08                     | -RS-485 Serial Commu-<br>nication |

| 19  | GND          | Ground                                         | n/a                               |

Table 3-2. PK2500 Header J1 I/O Functions

## **Configuring Serial Communications**

The PK2500 has two serial-communication ports. Table 3-3 provides the three *mutually exclusive* combinations of the RS-232 and RS-485 serial protocols that can be applied to the ports.

| Header Jumpers                                                                                                                        | Configurations                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Configuration I<br>H1 H3<br>1<br>3<br>4<br>5<br>7<br>6<br>8<br>6<br>4<br>2<br>7<br>5<br>3<br>1<br>1<br>6<br>8<br>6<br>4<br>2          | Two 3-wire RS-232<br>(no handshaking)                        |

| Configuration II<br>H1 H3<br>1 4 7 5 3 1<br>4 6 8 6 4 2                                                                               | One 5-wire RS-232<br>(RTS/CTS handshaking)<br>and one RS-485 |

| Configuration III<br>H1 H3<br>$1 \\ 4 \\ 6 \\ 8 \\ 8 \\ 6 \\ 4 \\ 6 \\ 8 \\ 8 \\ 6 \\ 4 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1$ | One 3-wire RS-232<br>(no handshaking) and<br>one RS-485      |

Table 3-3. PK2500 Serial Communication Configurations

## **Configuring Inputs and Outputs**

This section describes how to configure the I/O to specific application requirements.

#### Protected Digital Inputs vs. High-Current Outputs

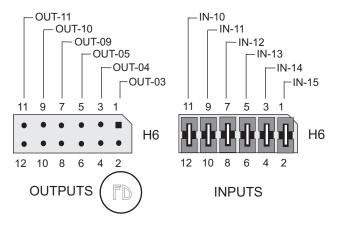

This section provides information for setting the jumpers on header H6 to configure pins 7–9 and 14–16 on header J1 as high-current outputs (OUT-03 to OUT-05 and OUT-09 to OUT-11) or as protected digital inputs (IN-10 to IN-15).

Figure 3-2 illustrates the jumper settings for header H6.

- When a jumper is installed, the corresponding pin is configured as a protected digital input.

- When a jumper is *not* installed, the corresponding pin is configured as a high-current output.

Each channel may be set up individually as desired.

Figure 3-2. Setting PK2500 Header H6 for Protected Digital Inputs or High-Current Outputs

The high-current driver output remains hardwired to the header J1 pins when a jumper is installed on header H6 to configure these pins as protected digital inputs. Do not enable the output drivers on any of the channels configured as protected digital inputs via header H6 unless the appropriate jumpers have been removed to configure these pins as high-current outputs.

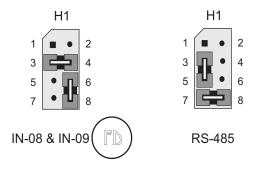

#### RS-485 vs. Protected Digital Inputs

This section provides information for setting the jumpers on header H1 to configure pins 17 and 18 on header J1 as protected digital inputs (IN-08 and IN-09) or as an RS-485 communications port (RS-485+ and RS-485-).

Figure 3-3 illustrates the jumper settings for header H1.

Figure 3-3. Setting PK2500 Header H1 for Protected Digital Inputs or RS-485

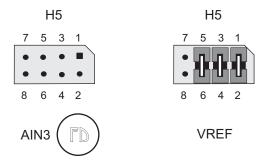

#### A/D Converter Input vs. A/D Voltage Reference Output

This section provides information for setting the jumpers on header H5 to configure pin 4 on header J4 as an A/D converter input (AIN3) or as an A/D voltage reference output (VREF).

Figure 3-4 illustrates the jumper settings for header H5.

Figure 3-4. Setting PK2500 Header H5 for A/D Converter Input or A/D Voltage Reference Output

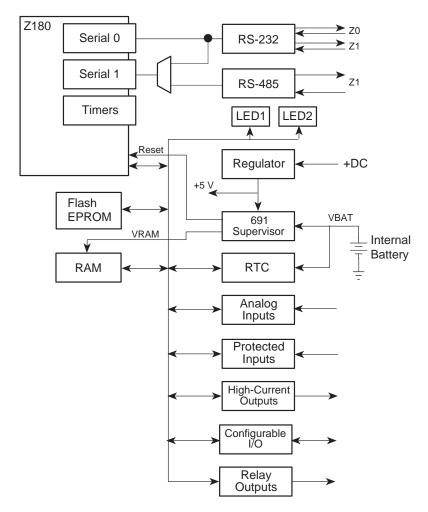

## PK2500 Subsystems

Figure 3-5 summarizes the PK2500's subsystems.

Figure 3-5. PK2500 Subsystems

# CHAPTER 4: SYSTEM DEVELOPMENT

Chapter 4 describes how to use the features of the PK2500 controller. The following major sections are included.

- PK2500 Operating Modes

- Running a Program

- Using Digital Inputs/Outputs

- Protected Digital Inputs

- High-Current Outputs

- Serial Communication

- Relay Outputs

- Analog-to-Digital Converter Inputs

- Additional Features

- Pulse-Width Modulated Outputs

- User-Programmable LEDs

- Real-Time Clock (RTC)

- · Power Supervisor

- +5 V Output

## PK2500 Operating Modes

The PK2500 has two *mutually exclusive* operating modes, only one of which responds to Dynamic C. Each mode is explained in detail below.

#### • Program Mode

In Program Mode, the PK2500 runs under the control of the PC, which is running Dynamic C. The PK2500 must be in this mode to compile a program or to debug a program.

In Program Mode, the PK2500 matches the baud rate of the PC COM port up to 57,600 bps. Baud rates of 9600 bps, 19,200 bps, 28,800 bps, and 57,600 bps are possible. The User LED, shown in Figure 4-1, is enabled to remain on continuously; the Run LED is disabled, or off. Both LEDs are available for the application being developed.

Figure 4-1. Run and User LED Locations

#### • Run Mode

In Run Mode, the PK2500 controller runs *standalone*. At power-up, the PK2500 checks to see if its onboard memory contains a program. If such a program exists, the PK2500 executes the program immediately after power-up.

Both LEDs are under the control of the application while the PK2500 is in Run Mode. The default is for the Run LED to be off and for the User LED to be on.

The PK2500 in Run Mode will not respond to Dynamic C running on a PC. Programs cannot be compiled or debugged while the PK2500 is in Run Mode.

In Run Mode, the PK2500 takes approximately 60 ms to boot up and begin execution of a program in the flash EPROM.

Table 4-1 lists the PK2500 activities in the two modes.

| Operating<br>Mode | Jumper<br>H2 | Activities                                                                                           |  |

|-------------------|--------------|------------------------------------------------------------------------------------------------------|--|

| Program Mode      | Installed    | • Compile a program                                                                                  |  |

|                   |              | • Run a program under debugger control                                                               |  |

|                   |              | • Run a program without "polling."<br>See Dynamic C manuals for a<br>description of program polling. |  |

| Run Mode          | Removed      | Run program (application)                                                                            |  |

Table 4-1. PK2500 Activities While in Program Mode

or in Run Mode

#### Changing the PK2500's Operating Mode

These steps describe how to change the PK2500's operating mode.

- 1. Disconnect power from the PK2500.

- 2. Locate the Run/Program jumper at H2 that protrudes from the board next to the RJ-12 connector (J2). Figure 4-2 shows the location of jumper H2.

Figure 4-2. Location of Run/Program Jumper at H2

- 3. Select Run Mode or Program Mode.

- Install the jumper **a**t H2 to select Program Mode.

- Remove jumper at H2 to select Run Mode.

- 4. Reapply power to restart the PK2500 in the selected mode.

Pay particular attention to the installation of the Run/Program jumper at H2. It is possible to install the jumper so that the pins are not connected. The PK2500 will not change modes if the Run/Program jumper is installed incorrectly.

## **Running a Program**

- 1. Place the PK2500 in Program Mode (with the Run/Program jumper installed at H2) and cycle the unit's power.

- 2. Open a program if one is not already open.

- 3. Select the **Compile** command from the **Compile** menu, or press **F3**.

- If no errors are detected, Dynamic C compiles the program and automatically downloads it into the PK2500's onboard flash EPROM memory.

- 5. Remove power from the PK2500.

- 6. Remove the Run/Program jumper.

- 7. Reapply power to the PK2500. This resets the PK2500 in the Run Mode, and the downloaded program begins to run.

The program is now loaded permanently in the PK2500's onboard flash EPROM. This program will now run automatically every time the PK2500 powers up in Run Mode until another program is loaded.

The flash EPROM has a rated lifetime of only 100,000 writes (unlimited reads). Do not write the flash EPROM from within a loop. The flash EPROM should be written to only in response to a human request for each write.

Follow these steps to return to Program Mode.

- 1. Disconnect power from the PK2500.

- 2. Reinstall the Run/Program jumper on header H2. Refer to Figure 4-2 for the jumper location.

- 3. Reapply power to the PK2500.

## **Using Digital Inputs/Outputs**

#### Protected Digital Inputs

The PK2500 provides up to 16 protected digital inputs. These inputs are designed as logical data inputs, returning either a Boolean 1 (ON) or 0 (OFF). The inputs accept voltages in the range of -20 V DC to +24 V DC, with a logic threshold of 2.5 V DC. This means that a protected digital input returns a 0 (OFF) if the input voltage is below 2.5 V DC, and it returns a 1 (ON) if the input voltage is above 2.5 V DC.

Protected digital inputs can be used with +5 V DC CMOS or TTL compatible hardware drivers and sensors. This compatibility allows a system to interface directly with other electronic hardware such as peripheral controllers and various mechanical switches, including relay contacts.

The PK2500 also provides two level-sensitive interrupts that are wired in parallel with protected inputs IN-06 and IN-07. The level-sensitive interrupts are software-assignable.

See Chapter 5, "Software Reference," for additional details on level-sensitive interrupts.

Appendix B, "Specifications," provides complete specifications for the PK2500's protected digital inputs.

#### How to Read the Inputs

The following Dynamic C software driver reads the status of a specified protected digital input.

#### int eioBrdDI ( unsigned chanNum )

Reads the state of an input channel.

PARAMETER: **chanNum** must be a number ranging from 0 (for IN-00) through 15 (for IN-15).

RETURN VALUE:

- 0 if and only if the input channel reads low.

- 1 if and only if the input channel reads high.

- -1 if and only if **chanNum** is out of range (**eioErrorCode** is bitored with **EIO\_NODEV**).

The sample input demonstration program DI.C in the SAMPLES\PK25xx subdirectory illustrates the use of the eioBrdDI driver.

DI.C

```

#use eziopk25.lib

// Use the PK2500 I/O

// library

// Assign INPUT0 protected

#define INPUT0

0

// digital input IN-00

main() {

int I;

// Create integer I

eioBrdInit(0);

// Initialize the PK2500

I = eioBrdDI(INPUT0); // Assign integer I the

// status of INPUTO

printf("IN-00 Status: %d\n", I);

// Print status of IN-00

// to the STDIO window

A-

I = eioBrdDI(INPUT0); // Assign integer I the

// status of INPUTO

printf("IN-00 Status: %d\n", I);

// Print status of IN-00

// to the STDIO window

// End of program

B٠

ו ∢

```

The following steps explain how to use the sample input demonstration program.

- 1. Open the sample program.

- 2. Compile the program by pressing **F3** or by choosing **Compile** from the **Compile** menu.

- 3. Connect a wire from pin 1, header J1, on the PK2500 (+DC) to pin 6, header J4 (IN-00). This connection provides a logic level 1 at IN-00.

Check to make sure that +DC does not exceed +24 V, the limit on the protected digital inputs, before completing Step 4. The power supply included with the Developer's Kit may exceed 24 V.

4. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **A**. At this point, the Dynamic C **STDIO** window opens and displays the status of IN-00. The status of IN-00 should be 1. If the status is not 1, or the **STDIO** window did not open, check the hardware connections and the program.

The PK2500's protected inputs are factory-configured to be pull-up. The inputs then return a logic level of 1 when not connected to ground.

- 5. Remove the wire from pin 1, header J1 (+DC), and connect this end to pin 3, header J1 (GND). Leave the end of the wire at pin 6, header J4 (IN-01) connected.

- 6. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **B**. At this point, the Dynamic C **STDIO** window opens and displays the status of IN-00. The status of IN-00 should be 0. If the status is not 0, or the **STDIO** window did not open, check the hardware connections and the program.

- 7. Continue to press **F8** until the program terminates.

- 8. Repeat steps 3 through 7 as desired for the other protected inputs.

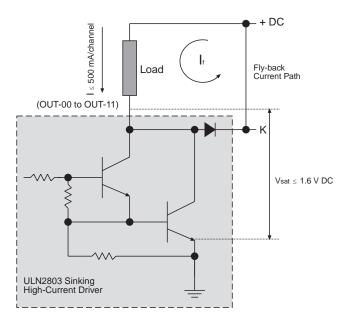

# High-Current Outputs

The PK2500 provides up to 12 high-current driver outputs in two banks of six. Each group of six outputs is factory-configured with "sinking" drivers, and can optionally be configured with "sourcing" drivers. By configuring one bank as sourcing and the other as sinking, it is possible to create push-pull or bidirectional drivers to control loads such as small reversible DC motors. Each bank of high-current driver outputs can provide up to 500 mA, with a maximum output of 75 mA per output channel.

Appendix D, "Sinking vs. Sourcing Drivers," provides more information on sinking and sourcing drivers.

### How to Use the Outputs

The following Dynamic C software turns a specified high-current driver ON or OFF.

int eioBrdDO( unsigned chanNum, char state )

Changes the state of an output channel.

PARAMETERS: **chanNum** must range from 0 (for OUT-00) through 11 (for OUT-11).

**state** is 0 if and only if the corresponding output is to be disabled (OFF); 1 if and only if the corresponding output is to be enabled (ON) RETURN VALUE:

- 0 if and only if **chanNum** is within range.

- -1 if and only if **chanNum** is out of range (**eioErrorCode** is bitored with **EIO\_NODEV**).

The sample input demonstration program DO.C in the SAMPLES\PK25xx subdirectory illustrates the use of the eioBrdDO driver.

DO.C

|        | #use eziopk25.lib                     | //   | Use the PK2500 I/O    |

|--------|---------------------------------------|------|-----------------------|

|        |                                       | //   | library               |

|        | #define OUTPUT0 0                     | 11   | Assign OUTPUT0 high-  |

|        |                                       | 11   | current output OUT-00 |

|        | #define ON 1                          | 11   | Assign ON the logic   |

|        |                                       | 11   | value 1               |

|        | #define OFF 0                         | 11   | Assign OFF the logic  |

|        |                                       | 11   | value 0               |

|        | <pre>main() {</pre>                   |      |                       |

|        | eioBrdInit(0);                        | 11   | initialize the PK2500 |

|        |                                       | FF); | // Turn-off OUT-00    |

| Δ      | eioBrdDO (OUTPUTO, O                  | •    | // Turn-on OUT-00     |

| В—     | →eioBrdDO(OUTPUT0,O                   | •    |                       |

| -<br>- |                                       | ,,   | End of program        |

| 5      | , , , , , , , , , , , , , , , , , , , | , ,  | Ena of program        |

The following steps explain how to use the sample output demonstration program.

- 1. Open the sample program.

- 2. Compile the program by pressing **F3** or by choosing **Compile** from the **Compile** menu.

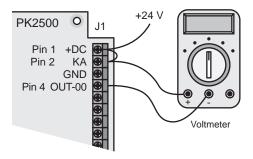

- 3. Connect a wire from pin 1, header J1, on the PK2500 (+DC) to pin 2, header J1 (KA). Connect a device such as a voltmeter between pin 4, header J1 (OUT-00) and pin 2 (KA), as shown in Figure 4-3, to monitor the status of the driver.

Figure 4-3. OUT-00 Status Example

Exercise caution when connecting any device to a highcurrent driver. Do not exceed the voltage and current limitations of the high-current driver. Appendix B contains complete specifications.

- 4. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **A**. At this point, the device should be "OFF." The voltmeter will read approximately 0 V because the output is not pulled to ground. If the device is not OFF, check the hardware connections and the program.

- 5. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **B**. At this point, the device should be "ON." The voltmeter will read approximately +24 V (+DC) because the output is pulled to ground. If the device is not ON, check the hardware connections and the program.

- 6. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **C**. At this point, the device should be "OFF" again (the voltmeter will read approximately 0 V). If the device is not OFF, check the hardware connections and the program.

- 7. Continue to press **F8** until the program terminates.

- 8. Repeat steps 3 through 7 as desired for the other outputs.

# **Serial Communication**

The PK2500 provides two serial communication ports that can be configured as RS-232 and/or RS-485.

See Chapter 3, "Input/Output Configuration," for further details on serial channel configurations.

# RS-232 Communication

RS-232 is an asynchronous serial communication protocol that is fullduplex (simultaneous bidirectional data transfer). The RS-232 ports and the Dynamic C software allow the PK2500 to communicate with other computers or controllers. A modem allows remote communication (including remote downloading) by using the X-modem protocol. RS-232 software drivers can be found in the Dynamic C SAMPLES\AASC subdirectory.

Refer to the Dynamic C manuals for additional information on remote downloading.

The optional Serial Interface Board 2 leaves both serial ports available to the application during software development. A special cable has to be made to access J2 if both RS-232 ports are needed.

### **RS-232** Connector Pinouts

The 6-pin RJ-12 modular phone jack (J2) facilitates all RS-232 connections. Table 4-2 lists the pin assignments for connector J2.

| J2 Pin | Handshaking<br>(Configuration II) | No Handshaking<br>(Configuration I or III) |

|--------|-----------------------------------|--------------------------------------------|

| 1      | RTS RS-232 (0)                    | Transmit RS-232 (1)                        |

| 2      | GND                               | GND                                        |

| 3      | Transmit RS-232 (0)               | Transmit RS-232 (0)                        |

| 4      | Receive RS-232 (0)                | Receive RS-232 (0)                         |

| 5      | CTS RS-232 (0)                    | Receive RS-232 (1)                         |

| 6      | +5 V regulated                    | +5 V regulated                             |

Table 4-2. J2 Pin Assignments

Do not pull more than 150 mA from pin 6 of J2.

### RS-485 Network

The PK2500 can be configured to provide one channel of RS-485 communication. RS-485 is an asynchronous multidrop half-duplex standard that provides multidrop networking with maximum cable lengths up to 1000 m.

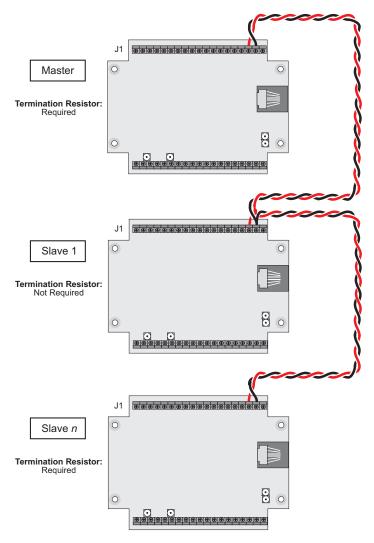

Figure 4-4. RS-485 Multidrop Network

The RS-485 drivers support up to 32 nodes. The transmission bandwidth may be reduced if more than 32 nodes are added. Contact Z-World Technical Support for assistance with large-scale network design. Dynamic C provides library functions for master-slave two-wire half-duplex RS-485 9-bit binary communications.

This RS-485 hardware standard supports up to 32 controllers on one network. The software supports one master unit, plus up to 255 slave units (which may consist of any combination of Z-World controllers that support the RS-485 protocol).

The resulting multidrop network (shown in Figure 4-4) can span up to a kilometer, facilitating the design of a robust distributive control system.

Follow these steps to configure a multidrop network.

- Configure pins 17 and 18 on header J1 for RS-485 communications, as outlined in the "Configuring Serial Communications" section in Chapter 3.

- 2. Connect RS-485+ to RS-485+ and RS-485- to RS-485- on all networked controllers, using single twisted-pair wires. Use Figure 4-4 for reference.

Refer to the Dynamic C manuals for additional information on master-slave networking.

### **Termination and Bias Resistors**

Termination and bias resistors are required in a multidrop network to minimize reflections (echoing) and to keep the network line active when it is in an idle state.

Bias resistors are required in most cases on the master controller to keep the network line reliable. The PK2500 is factory-configured with 10 k $\Omega$  bias resistors installed.

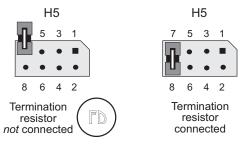

An external termination resistor is not required. A jumper on header H5 determines whether the onboard termination resistor is connected to the network. The termination resistor is needed only at the physical ends of the network, as shown in Figure 4-4. The resistor is disconnected by removing the jumper. Figure 4-5 summarizes the jumper configuration.

Figure 4-5. PK2500 Jumper Settings on Header H5 for Termination Resistor

# **Relay Outputs**

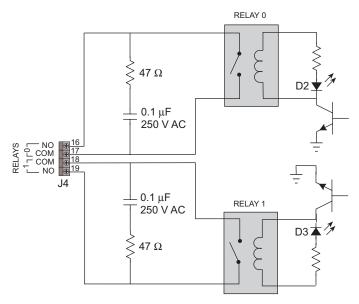

The PK2500 has two relays to drive external loads. The two contacts for Relay 0 are available at pins 16 and 17 on header J4, while those for Relay 1 are available at pins 18 and 19 on header J4. Both sets of contacts are normally open. The relays are rated for a 60 W load, for example, 2 A at 30 V DC or 0.5 A at 125 VAC. The maximum switching voltage is 125 V.

For CE compliance, the maximum relay switching voltage is less than 50 VAC or 75 VDC.

Two LEDs are provided to provide a visual aid for development or for field diagnostics. LED D3 turns on when Relay 1 is activated. LED D2 does the same for Relay 0.

Figure 4-6 shows the relay outputs.

Figure 4-6. Relay Outputs

An onboard snubber network is provided for each relay to attenuate switching transients that develop when inductive loads are driven. Each network consists of a 47  $\Omega$  resistor in series with a 0.1  $\mu F$  capacitor. It is remotely possible for some switching transients to be large enough to cause disruptive interference to the PK2500 logic. This depends to a large degree on the size and reactance of the load. This should not be a problem because the relays are only rated for 60 W resistive loads. Inductive loads should be derated. External transient suppressors, such as metal oxide

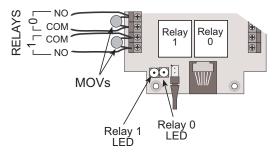

varistors (MOVs) may be added in parallel with the relay contacts if there are problems despite the built-in snubber circuitry. MOVs come in a range of protective-voltage ratings. Select one with a voltage rating slightly higher than that of the load.

Figure 4-7 shows the MOVs installed across the relay outputs.

Figure 4-7. Installation of Metal Oxide Varistors to Suppress Transients

Use heat-shrink tubing over the exposed portions of the MOV leads, especially if high voltages (over 48 V) are being switched.

# How to Use the Relay Outputs

The following Dynamic C software turns a specified relay ON or OFF.

### int eioBrdRelay( unsigned chan, char onOff )

Changes the state (whether the relays are energized) of the two relays on the PK2500.

PARAMETERS: **chan** identifies which relay to switch—0 for Relay 0 or 1 for Relay 1.

**onOff** specifies whether the relay should be energized (non-zero) or de-energized (zero).

RETURN VALUE:

- 0 if the operation was successful.

- -1 if and only if **chan** is out of range (**eioErrorCode** is bit-ored with **EIO\_NODEV**).

The sample relay output demonstration program **REL**. **C** in the **SAMPLES\PK25xx** subdirectory illustrates the use of the **eioBrdRelay** driver.

| REL. | С |

|------|---|

|------|---|

|          | #use eziopk25.lib         |    | //     | Use the PK2500 I/O    |

|----------|---------------------------|----|--------|-----------------------|

|          |                           |    | 11     | library               |

|          | #define OUTPUT0 (         | C  | //     | Assign OUTPUT0        |

|          |                           |    | 11     | relay output RELO     |

|          | #define ON 1              | 1  | //     | Assign ON the logic   |

|          |                           |    | 11     | value 1               |

|          | #define OFF (             | C  | //     | Assign OFF the logic  |

|          |                           |    | 11     | value 0               |

|          | main() {                  |    |        |                       |

|          | <pre>eioBrdInit(0);</pre> |    | //     | initialize the PK2500 |

|          | eioBrdRelay(OUTPU         | т0 | , off) | ; // Turn off RELO    |

| Α —      | 🗕 eioBrdRelay (OUTPU      | т0 | ,ON);  | // Turn on RELO       |

| в—       |                           | то | ,OFF)  | ; // Turn off RELO    |

| <u> </u> | →}                        |    |        | End of program        |

| 0        | <i>,</i>                  |    | , ,    |                       |

The following steps explain how to use the Relay Output Demonstration Program.

- 1. Open the sample program.

- 2. Compile the program by pressing **F3** or by choosing **Compile** from the **Compile** menu.

- 3. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **A**. At this point, the relay should be "OFF." If the relay is not OFF, check the hardware connections and the program.

- 4. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **B**. At this point, the relay should be "ON," and LED D2 should flash. If the relay is not ON, check the hardware connections and the program.

- 5. Use the Dynamic C command **F8** (run/step over) to single-step through the program to the line marked **C**. At this point, the relay should be "OFF" again. If the relay is not OFF, check the hardware connections and the program.

- 6. Continue to press **F8** until the program terminates.

- 7. Repeat steps 3 through 6 as desired for the other relay output.

# Analog-to-Digital Converter Inputs

The PK2500 has four analog input channels that are brought out on header J4. The analog inputs are designated AIN0 to AIN3, and are listed in Table 4-3.

| Header J4<br>Pin No. | Signal | Dynamic C Channel<br>No. |

|----------------------|--------|--------------------------|

| 1                    | AIN0   | 0                        |

| 2                    | AIN1   | 1                        |

| 3                    | AIN2   | 2                        |

| 4                    | AIN3   | 3                        |

| 5                    | GND    | Analog Ground            |

Table 4-3. Analog Input Channel Numbers

Use pin 5 on header J4 for analog ground only. Do not use this pin as a ground for any other signals.

The analog input channels can be configured for a wide range of input voltages. The default input range of the analog inputs is 0 V to 10 V. The analog inputs can be configured for almost any input range by replacing two resistors in the input amplifier circuit.

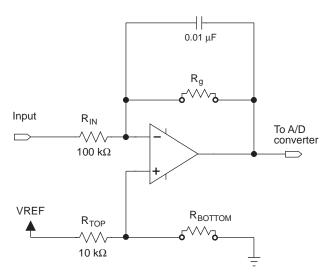

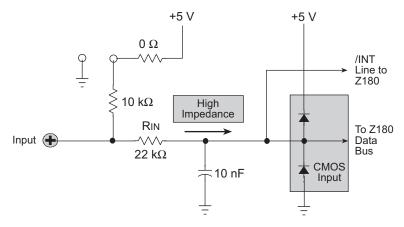

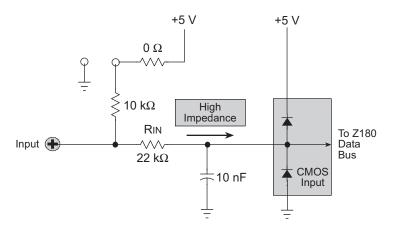

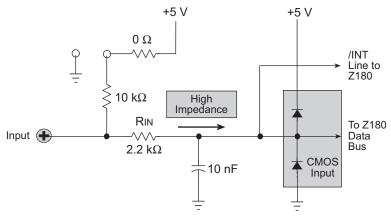

Each analog channel consists of an inverting amplifier referenced to a userdefined offset voltage, as shown in Figure 4-8.

Figure 4-8. Analog Input Amplifier

Table 4-4 shows the analog input amplifier components.

| Channel | R <sub>IN</sub> | R <sub>g</sub> | R <sub>TOP</sub> | <b>R</b> BOTTOM | CAP |

|---------|-----------------|----------------|------------------|-----------------|-----|

| AIN0    | R3              | R2             | R5               | R4              | C1  |

| AIN1    | R17             | R16            | R14              | R15             | C21 |

| AIN2    | R22             | R23            | R18              | R19             | C25 |

| AIN3    | R25             | R24            | R20              | R21             | C26 |

Table 4-4. Analog Input Component References

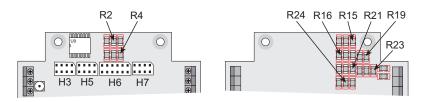

Changing the values of  $R_{\rm g}$  and  $R_{\rm BOTTOM}$  sets the gain and offset of the channel. Figure 4-9 shows the locations of the  $R_{\rm g}$  and  $R_{\rm BOTTOM}$  resistors.

Figure 4-9. Locations of  $R_g$  and  $R_{BOTTOM}$  Resistors

Table 4-5 shows resistor values for some common analog input voltage ranges.

| Channel Input<br>Range (V) | R <sub>g</sub> (kΩ) | R <sub>воттом</sub> (kΩ) |

|----------------------------|---------------------|--------------------------|

| -10.0 to +10               | 11.8                | 8.06                     |

| - 5.0 to + 5.0             | 23.7                | 6.65                     |

| - 2.5 to + 2.5             | 47.5                | 4.99                     |

| - 2.0 to + 2.0             | 59.0                | 4.53                     |

| - 1.0 to + 1.0             | 118                 | 2.87                     |

| - 0.5 to + 0.5             | 237                 | 1.69                     |

| - 0.25 to + 0.25           | 464                 | 0.953                    |

| - 0.10 to + 0.10           | 1180                | 0.392                    |

| 0 to +10.0                 | 23.7                | 39.2                     |

| 0 to + 5.0                 | 46.4                | 19.6                     |

| 0 to + 2.5                 | 93.1                | 10.0                     |

| 0 to + 1.0                 | 226                 | 4.02                     |

| +1 to + 2.0                | 237                 | 13.3                     |

| +2 to + 7.0                | 47.5                | 140.0                    |

| +0.020 to + 0.100          | 3010                | 0.402                    |

Table 4-5. Resistor Values for Common Input Ranges

If the application requires an input voltage range not shown in Table 4-5, the correct values of  $R_g$  and  $R_{BOTTOM}$  can be determined using the formulas presented in the next section.

$\rm R_g$  and  $\rm R_{\rm BOTTOM}$  are both 1206-size surface-mount technology (SMT) resistors.

The analog input resistors and capacitors are surface-mounted. Use proper SMT techniques (see Z-World Technical Note 106, *Soldering and Desoldering Surface-Mount Chip Components*) to remove and replace these parts.

# Scaling Input Range

Once the input range has been determined, the appropriate resistor values must be selected. The steps below describe this process.

1. The first step in setting up the channel is to choose a gain resistor. Use Equation (4-1) to determine the value of the gain resistor.

$$R_g = \frac{2.5 \times 10^5}{V_{IN_{\rm max}} - V_{IN_{\rm min}}}$$

(4-1)

2. Next, select R<sub>BOTTOM</sub> using Equation (4-2).

$$R_{BOTTOM} = \frac{R_g \cdot V_{IN_{\text{max}}} \cdot 10^4}{R_g \cdot (2.5 - V_{IN_{\text{max}}}) + (2.5 \times 10^5)}$$

(4-2)

- Select the appropriate resistor values. Standard resistor values can be found in many electronics references and catalogs. Using 1% resistors will give better accuracy and a greater number of choices than using 5% resistors.

- For R<sub>g</sub>, select the next standard value less than the standard value closest to the computed value. Choosing a lower value helps insure that the input signal does not exceed the 2.5 V reference voltage for the ADC.

- For R<sub>BOTTOM</sub>, select the nearest standard value.

4. To verify that the calculated values provide the correct gain and offset, plug  $V_{IN_{min}}$  and  $V_{IN_{max}}$  into Equation (4-3).

$$V_{OUT} = \left(\frac{R_{BOTTOM}}{R_{BOTTOM} + 10^4} \cdot 2.5 - V_{IN}\right) \cdot \frac{R_g}{10^5} + \frac{R_{BOTTOM}}{R_{BOTTOM} + 10^4} \cdot 2.5$$

$$(4-3)$$

$V_{\rm IN_{min}}$  should yield a positive  $V_{\rm OUT}$  just less (within 50 mV) than 2.5 V.  $V_{\rm IN_{max}}$  should yield a positive  $V_{\rm OUT}$  just greater (within 50 mV) than zero.

5. Test the circuit to verify it works properly.

#### Example

Given a sensor that has an output of -1 to 2 V,  $V_{\rm IN_{min}}$  and  $V_{\rm IN_{max}}$  are as follows.

$$V_{IN_{max}} = 2 V, V_{IN_{min}} = -1 V$$

1. Determine the value of the gain resistor using Equation (4-1).

$$R_g = \frac{2.5 \times 10^5}{(2) - (-1)}$$

= 83.3 k\Omega (ideal value).

2. Select  $R_{\text{BOTTOM}}$  using Equation (4-2).

$$R_{BOTTOM} = \frac{83.3 \times 10^3 \cdot 2 \cdot 10^4}{(8.33 \times 10^3) \cdot (2.5 - (2)) + (2.5) \cdot (10^5)}$$

= 5.71 k\Omega (ideal value).

- 3. Select resistor values.

- The next lower standard 1% value for  $R_{g}$  is 80.6 k $\Omega$ .

- The closest standard 1% value for  $R_{BOTTOM}$  is 5.76 k $\Omega$ .

- 4. Now, check values by plugging  $V_{INmin}$  and  $V_{INmax}$  into Equation (4-3).

- Check  $V_{\text{OUT}}$  for  $V_{\text{INmin}}$ .

$$V_{OUT} = \left(\frac{5.76 \times 10^3}{5.76 \times 10^3 + 10^4} \cdot 2.5 - (-1)\right) \cdot \frac{80.6 \times 10^3}{10^4} \\ + \frac{5.76 \times 10^3}{5.76 \times 10^3 + 10^4} \cdot 2.5$$

= 2.456 V.

This value of  $V_{OUT}$  is within 50 mV of 2.5 V using  $V_{INmin}$ .

• Check V<sub>OUT</sub> for V<sub>INmax</sub>.

$$V_{OUT} = \left(\frac{5.76 \times 10^{3}}{5.76 \times 10^{3} + 10^{4}} \cdot 2.5 - (2)\right) \cdot \frac{80.6 \times 10^{3}}{10^{4}} + \frac{5.76 \times 10^{3}}{5.76 \times 10^{3} + 10^{4}} \cdot 2.5$$

= 0.038 V.

This value of  $V_{OUT}$  is within 50 mV of 0 V using  $V_{INmax}$ .

Both  $V_{OUT}$  numbers fall within the acceptable output range.

In this example, with  $R_g = 80.6 \text{ k}\Omega$  and  $R_{BOTTOM} = 5.76 \text{ k}\Omega$ , the analog channel will accept inputs from -1 V to 2 V. The amplifier output is then in the range from 0 V to 2.5 V, with a little margin (~30 mV) for system error (for example, ADC or op-amp offset).

# Theory of Operation

This section presents a complete analysis of the analog input circuit (see Figure 4-8).

The initial first-order approximation of the op amp assumes the following:

- Infinite open-loop gain,

- Zero output impedance,

- Zero voltage offset,

- Infinite input impedance,

- Zero input bias currents, and

- Noiseless components.

### The $V_{OFF}$ Voltage Divider

The voltage divider formed by  $R_{TOP}$  and  $R_{BOTTOM}$  provides an offset voltage for the amplifier. The offset voltage  $V_{OFF}$  is given by Equation (4-4).

$$V_{OFF} = \frac{R_{BOTTOM}}{R_{BOTTOM} + R_{TOP}} \cdot V_{REF}$$

(4-4)

$V_{REF}$  for the PK2500 is 2.5 V.

### DC Gain

Now, examine the DC gain of the circuit.

An amplifier in a negative feedback topology will force the error between the amplifier's inputs to zero. This implies the following:

$$V_{(\text{INVERTING})} = V_{(\text{NONINVERTING})} = V_{\text{OFF}}$$

.

Since there is infinite impedance at the op amp's inputs, the current through  $R_{IN}$  must equal the current through  $R_g$ . The current through  $R_{IN}$  is determined by Equation (4-5).

$$I_{R_{IN}} = \frac{V_{IN} - V_{OFF}}{R_{IN}}$$

(4-5)

The current through  $R_g$ ,  $I_{Rg}$ , is

$$I_{R_g} = \frac{V_{OFF} - V_{OUT}}{R_g} \quad . \tag{4-6}$$

Setting Equation (4-5) and Equation (4-6) equal and solving for  $\rm V_{_{OUT}}$  yields the following:

$$V_{OUT} = \left(\frac{V_{OFF} - V_{IN}}{R_{IN}}\right) \cdot R_g + V_{OFF} \quad . \tag{4-7}$$

When  $V_{OFF}$  is zero, the circuit scales  $V_{IN}$  by a factor of  $-R_g/R_{IN}$ . This is the DC gain. The DC gain can be determined by Equation (4-8).

$$g = \frac{-R_g}{R_{IN}} \Longrightarrow |g| = \frac{R_g}{R_{IN}}$$

(4-8)

This result agrees with the gain of a classic op amp inverting amplifier.

Given a desired input range, it is possible to compute the required circuit gain.

The amplifier needs to map the input voltage range to the  $0-\mathrm{V}_{\mathrm{REF}}$  input range of the ADC. Thus

$$g = \frac{V_{REF}}{V_{IN_{\text{max}}} - V_{IN_{\text{min}}}} \quad . \tag{4-9}$$

The PK2500 has  $V_{REF} = 2.5 \text{ V}$  and  $R_{IN}$  is shipped as 10 k $\Omega$ .

Once the gain has been computed, Equation (4-8) can be used to compute  $R_{g}$ .

### Finding V<sub>OFF</sub>

Once the gain is known,  $V_{\rm OFF}$  required to center the output in the range between 0 V and  $V_{\rm RFF}$  can be determined.

Examine  $V_{\text{OFF}}$  when  $V_{\text{IN}}$  is at minimum and maximum.

First, take the case of a maximum  $V_{_{\rm IN}}$ . Because the circuit is an inverting amplifier,  $V_{_{\rm IN}}$  must map  $V_{_{\rm OUT}}$  to zero.

Start with Equation (4-7) and substitute  $V_{OUT} = 0$  and  $V_{IN} = V_{IN_{max}}$  to get

$$0 = \left(\frac{V_{OFF} - V_{IN_{\max}}}{R_{IN}}\right) \cdot R_g + V_{OFF}$$

$$= \left(V_{OFF} - V_{IN_{\max}}\right) \cdot \frac{R_g}{R_{IN}} + V_{OFF} \quad .$$

(4-10)

Now, simplify using Equation (4-8). Substitute Equation (4-8) into Equation (4-10).

$$0 = (V_{OFF} - V_{IN_{max}}) \cdot (-g) + V_{OFF}$$

=  $(V_{IN_{max}} - V_{OFF}) \cdot g + V_{OFF}$  (4-11)

Then,

$$V_{OFF} = V_{IN_{\text{max}}} \cdot \frac{g}{g+1} \quad . \tag{4-12}$$

Do the same thing for  $V_{IN} = V_{INmin}$ . When  $V_{INmin}$  is presented at  $V_{IN}$ ,  $V_{OUT} = V_{REF}$ . has to be true. Start with Equation (4-7) and substitute  $V_{OUT} = V_{REF}$  and  $V_{IN} = V_{INmin}$  to get

$$V_{REF} = \left(\frac{V_{OFF} - V_{IN_{\min}}}{R_{IN}}\right) \cdot R_g + V_{OFF}$$

$$= \left(V_{OFF} - V_{IN_{\min}}\right) \cdot \frac{R_g}{R_{IN}} + V_{OFF}$$

$$= \left(V_{OFF} - V_{IN_{\min}}\right) \cdot (-g) + V_{OFF}$$

$$= \left(V_{IN_{\min}} - V_{OFF}\right) \cdot g + V_{OFF}$$

$$= V_{IN_{\min}} \cdot g + V_{OFF} \left(1 - g\right) .$$

(4-13)

Rearrange and solve for  $V_{OFF}$ ..

$$V_{OFF} = \frac{V_{IN_{\min}} \cdot (g) - V_{REF}}{(g-1)}$$

(4-14)

Either Equation (4-12) or Equation (4-14) may be used to calculate  $V_{OFF}$ .

### Practical Considerations

Resistors are available only in discrete standard values. Once ideal values are computed, a standard value must be selected. There are more 1% resistor values to choose from than there are 5% resistor values. Also, 1% resistors have a lower temperature drift. There is only a slight difference in cost between 1% and 5% resistors.

Resistors over 3 M $\Omega$  should be avoided. Two reasons to avoid large resistor values are circuit noise susceptibility and part availability. Reducing R<sub>IN</sub> or adding an external preamp are alternative methods of increasing gain if a large DC gain is needed.

The op amp in the PK2500 has a  $\pm$ 7.5 mV maximum offset voltage (at 25°C). This offset is multiplied by the D.C. gain and added to V<sub>OUT</sub>. This means if the DC gain is 10, V<sub>OUT</sub> may have an offset in it of up to 75 mV.

The input bias currents of the op amp will also produce error voltages at the inputs that get multiplied by the DC gain, and will show up as an offset in  $V_{OUT}$ . Fortunately, the input bias currents are very low, of the order of picoamperes, and so this effect should be negligible.

To avoid these offsets pushing  $V_{OUT}$  beyond the  $0-V_{REF}$  range of the ADC, select R<sub>g</sub> to be a smaller standard value than computed. This will sacrifice some dynamic range of the ADC for improved reliability.

Selecting  $\mathbf{R}_{_{\rm BOTTOM}}$  is a matter of picking the standard value closest to the computed value.

### Input Impedance

The input impedance looking into the circuit from  $V_{IN}$  is just  $R_{IN}$ . Note also that  $R_{IN}$  is connected to the inverting input, which is maintained (by the op amp's negative feedback) at  $V_{OFF}$ .

Gain can be increased by sacrificing input impedance. A fixed value of  $R_{_{IN}}$  will produce a larger DC gain if  $R_{_{IN}}$  is reduced. However, a smaller  $R_{_{IN}}$  will require the source of  $V_{_{IN}}$  (often a transducer) to provide additional current, as shown in Equation (4-15).

$$I_{R_{IN}} = \frac{V_{IN} - V_{OFF}}{R_{IN}}$$

(4-15)

#### **Frequency Response**

The capacitor in the feedback loop fixes a pole as shown in Equation (4-16).  $F_c$ , the 3 dB point for the single-pole filter is in hertz, and C is capacitance.

$$F_C = \frac{1}{2\pi \cdot R_g \cdot C} \tag{4-16}$$

The filter will roll off at the 20 dB decade after  $F_c$ .

This low-pass filter helps eliminate noise in the channel. The pole should be set as low as possible for the application. The standard capacitor shipped is  $0.01 \ \mu\text{F}$ .

### How to Use the Analog-to-Digital Converter

The best way to use the A/D converter is with the Z-World Dynamic C drivers. This helps to ensure that the code will be compatible with future versions of the PK2500 as well as other Z-World products.

### Using the Analog Inputs

The factory calibrates each PK2500, storing each unit's individual zero offset and actual gain for each channel in simulated EEPROM. The library function **eioBrdAI** uses these calibration values to provide adjusted readings for the analog inputs.

### float eioBrdAI( unsigned int eioAddr )

Reads an input and performs analog-to-digital conversion.

PARAMETERS: **eioAddr** specifies an input of 0 to 3 or 16 to 19 to be read. **eioAddr** values 0 through 3 represent analog inputs 0 through 3 and cause the function to return the voltage read at an input. **eioAddr** values 16 through 19 also represent analog inputs 0 through 3, but cause the function to return a 12-bit raw data value for the analog input.

#### RETURN VALUE:

- Voltage read for **eioAddr** values 0 through 3, if the read is successful.

- 12-bit raw data value read from the A/D converter for **eioAddr** values 16 through 19, if the read is successful.

- Sets eioErrorCode if eioAddr is out of range.

#### int eioBrdACalib( int chanNum, int d1, int d2, float f1, float f2)

Sets up the calibration constants needed by **eioBrdAI** when called with **chanNum** equal to 0.

The function computes the calibration coefficients and stores them in reserved locations in nonvolatile memory. The function **eioBrdInit** loads these constants from nonvolatile memory.

PARAMETERS: **chanNum** must range from 0 (for AIN0) through 3 (for AIN3).

**d1** is the raw, digital reading corresponding to the applied analog resistance **f1**.

**d2** is the raw, digital reading corresponding to the applied analog resistance **f2**.

The sample input demonstration program AI.C in the SAMPLES\PK25xx subdirectory illustrates the use of the eioBrdAI driver.

```

AI.C

```

```

#use eziopk25.lib

#define INPUTCHAN 0

main() {

float raw, analog;

eioBrdInit(0); // initialize the I/O driver

eioErrorCode = 0; // clear error flag

raw = eioBrdAI(INPUTCHAN+16);

// read the raw chan.

/* read channel, scale with calibration constants */

eioErrorCode = 0; // clear error flag

analog = eioBrdAI (INPUTCHAN) ;

if (eioErrorCode & EIO_NODEV)

{

printf("analog input channel %d doesn't

exist!\n", INPUTCHAN);

}

else

{

printf("analog input channel %d reads 0x%04x,

interpreted to %f\n", INPUTCHAN,

(int) raw, analog);

}

}

```

### Using the A/D Voltage Reference

The jumpers on header H5 are used to configure pin 4 of header J4 to provide a buffered copy of the internal reference voltage used by the A/D converter. This is useful in applications such as ratiometric measurements if the sensors need to track the same voltage reference used by the A/D converter.

The Channel 3 op-amp serves as the buffer. Do not draw more than 2 mA to 3 mA since the op-amp's current drive is limited.

Chapter 3, "Input/Output Configuration," provides the exact jumper configurations for header H5 to serve as either an A/D converter input or and A/D voltage reference.

# **Additional Features**

This section provides information on the PK2500's additional features including pulse-width modulated outputs, user-programmable LEDs, the real-time clock, the power supervisor, and a +5 V output.

# Pulse-Width Modulated (PWM) Outputs

The 12 high-current outputs on the PK2500 are driven by two driver chips in two banks of six outputs each. The PWM feature is available on up to six of the outputs in either group at any one time.

The supplied software provides two levels of support. The first level provides easy-to-use fixed PWM functions for only four of the outputs. The periods of the PWM signals are fixed at 13.3 ms (75 Hz), with a resolution of 256 divisions per period (8-bit resolution). Dynamic C consumes about 8% of the PK2500's processing power when used to generate PWM signals. The second PWM support level allows custom PWM functions to be created for six of the outputs.

Serial-communication baud rates may be affected when PWM functions are used because the microprocessor's functions may get overloaded. Serial data rates become limited and fixed at 4800 bps for Serial Port 1. Be sure to reset the Dynamic C baud rate to 4800 bps.

Contact Z-World Technical Support at (530)757-3737 for assistance with PWM functions.

See Chapter 5, "Software Reference," for advanced PWM programming information.

### How to Use the PWM Feature

The PK2500 can produce fixed-frequency, fixed-phase, variable-duty-cycle square waves from up to six of its high-current outputs. This section first presents a simple, easy-to-use PWM function that drives only four of the PK2500's outputs. A more complex set of functions that require more indepth understanding of DMA and PWM generation is presented later.

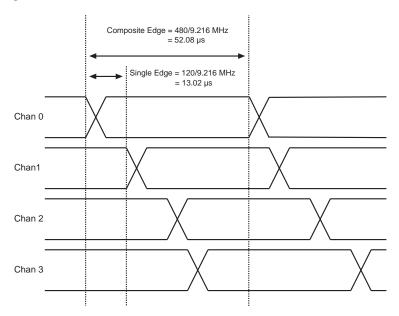

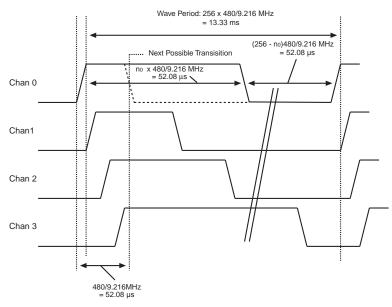

Figure 4-10 and Figure 4-11 provide PWM transition and DMA timing diagrams.

### int eioBrdAO( unsigned chanNum, unsigned state )

Specifies the duty cycle for a particular output channel.

- **chanNum** is a number ranging from 0 (for OUT-00) to 3 (for OUT-03).