LP3100

C-Programmable Controller User's Manual

Revision E

#### LP3100 User's Manual

Part Number 019-0049 • Revision E Last revised on February 3, 2000 • Printed in U.S.A.

## Copyright

© 1999 Z-World, Inc. • All rights reserved.

Z-World reserves the right to make changes and improvements to its products without providing notice.

## **Trademarks**

- Dynamic  $C^{\mathbb{R}}$  is a registered trademark of Z-World, Inc.

- Windows® is a registered trademark of Microsoft Corporation

- Hayes Smart Modem<sup>®</sup> is a registered trademark of Hayes Microcomputer Products, Inc.

#### **Notice to Users**

When a system failure may cause serious consequences, protecting life and property against such consequences with a backup system or safety device is essential. The buyer agrees that protection against consequences resulting from system failure is the buyer's responsibility.

This device is not approved for life-support or medical systems.

All Z-World products are 100 percent functionally tested. Additional testing may include visual quality control inspections or mechanical defects analyzer inspections. Specifications are based on characterization of tested sample units rather than testing over temperature and voltage of each unit. Z-World may qualify components to operate within a range of parameters that is different from the manufacturer's recommended range. This strategy is believed to be more economical and effective. Additional testing or burn-in of an individual unit is available by special arrangement.

# **Company Address**

## Z-World, Inc.

2900 Spafford Street Davis, California 95616-6800 USA

Telephone: (530) 757-3737 Facsimile: (530) 757-5141

Web site: http://www.zworld.com E-mail: zworld@zworld.com

# TABLE OF CONTENTS

## **About This Manual**

| Chapter 1: Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 1.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                             |

| 1.2 Standard Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |

| 1.3 Flexibility and Customization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                               |

| 1.4 Subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| 1.4.1 Microprocessor, Memory, and Support Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                               |

| 1.4.2 Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |

| 1.4.3 Digital Inputs/Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| 1.4.4 Analog Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                             |

| 1.4.5 Serial Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |

| 1.4.7 LPBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

| 1.4.8 LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |

| 1.5 Development and Evaluation Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |

| 1.5.1 Development Kit Packing List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                               |

| 1.6 Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| 1.7 CE Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               |

| Chapter 2: Getting Started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | g                                                                             |

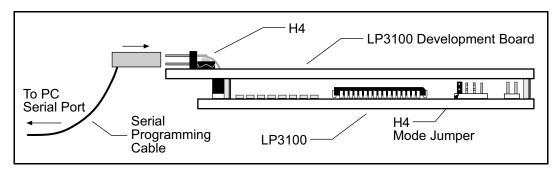

| 2.1 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                                            |

| 2.1.1 Changing Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                            |

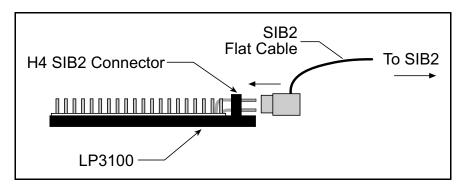

| 2.1.2 Using a SIB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11                                                                            |

| 2.2 Connecting an LP3100 to a PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                               |

| 2.3 Establishing Communication with an LP3100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               |

| 2.4 Running a Sample Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                               |

| Chapter 3: Subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                            |

| 3.1 Subsystems Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18                                                                            |

| 3.1 Subsystems Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18                                                                            |

| 3.1 Subsystems Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               |

| 3.1 Subsystems Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode                                                                                                                                                                                                                                                                                                             |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown                                                                                                                                                                                                                                                                                    | 18 19 19 19 19 19 19 19 19 19 19 19 19 19                                     |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output                                                                                                                                                                                                                                                           | 18 19 19 19 19 19 19 19 19 19 19 19 19 19                                     |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4.1 Digital I/O Operating Modes and Configuration                                                                                                                                                                                                                                |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4.1 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs                                                                                                                                                                                |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4.1 Digital Input/Output 3.4.1 Digital Inputs 3.4.2 Digital Inputs 3.4.3 Digital Outputs                                                                                                                                                                                         |                                                                               |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs                                                                                                                               | 18 19 19 19 19 21 21 22 22 22 22 22 22 25 28 28 28 28 30                      |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4.1 Digital Input/Output 3.4.1 Digital Inputs 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs 3.4.5 Analog Inputs 3.5 Analog Inputs 3.5 Analog Inputs 3.5 Analog Inputs                                                                                  | 18 19 19 19 21 22 22 22 22 22 25 25 28 28 28 28 28 30 33                      |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs                                                                                                                               | 18 19 19 19 20 21 22 22 22 22 22 25 28 28 28 28 28 28 28 28 28 28 28 28 28    |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM. 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs 3.5.5 Analog Inputs 3.5.1 Scaling Input Range                                                                                | 18 19 19 19 19 20 21 22 22 22 22 25 25 28 28 28 28 28 28 28 28 28 28 28 28 28 |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs 3.5.5 Analog Inputs 3.5.1 Scaling Input Range 3.6.0 Operation 3.6.1 The VOFF Voltage Divider 3.6.2 DC Gain                    | 18 19 19 19 19 20 21 22 22 22 22 25 28 28 28 28 28 28 28 28 28 28 28 28 28    |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs 3.5.5 Analog Inputs 3.5.1 Scaling Input Range 3.6 Operation 3.6.1 The VOFF Voltage Divider 3.6.2 DC Gain 3.6.3 Finding VOFF   | 18 19 19 19 19 20 21 22 22 22 22 25 28 28 28 28 28 28 28 28 28 28 28 28 28    |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs 3.5.5 Analog Inputs 3.5.6 Coperation 3.6.7 Food of the VOFF Voltage Divider 3.6.8 Finding VOFF 3.6.9 Practical Considerations | 18 19 19 19 19 20 21 22 22 22 22 25 28 28 28 28 28 28 28 28 28 28 28 28 28    |

| 3.1 Subsystems Overview 3.2 Microprocessor, Memory, and Support Circuits 3.2.1 Microprocessor Supervisor 3.2.2 Flash EPROM 3.3 Power Control 3.3.1 Power Supplies 3.3.2 Power Supply Control 3.3.3 Shutting Down VCC 3.3.4 Clock Speed 3.3.5 Microprocessor Operating Modes and Shutdown Mode 3.3.6 Component Shutdown 3.4 Digital Input/Output 3.4.1 Digital I/O Operating Modes and Configuration 3.4.2 Digital Inputs 3.4.3 Digital Outputs 3.4.4 Digital Inputs/Outputs 3.5.5 Analog Inputs 3.5.6 Operation 3.6.1 The VOFF Voltage Divider 3.6.2 DC Gain 3.6.3 Finding VOFF                           | 18 19 19 19 19 21 22 22 22 22 22 25 28 28 28 28 28 28 28 28 28 28 28 28 28    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 3.6.8 Using the Analog Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47                                                               |

| 3.7 Serial Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |

| 3.7.1 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |

| 3.7.3 RS-485 Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |

| 3.7.4 Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                               |

| 3.8 Real-Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 3.8.1 Real-Time Clock Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |

| 3.8.2 Periodic Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |

| 3.8.3 Alarm Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54<br>51                                                         |

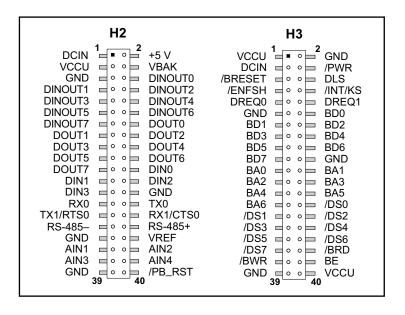

| 3.9 LPBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |

| 3.9.1 LPBus Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 3.9.2 Board ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  |

| Chapter 4: Software Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                               |

| 4.1 Using Dynamic C Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62                                                               |

| 4.2 Digital Input/Output Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                  |

| 4.3 Analog Input Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68                                                               |

| 4.4 Serial Communication Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                  |

| 4.4.1 RS-485 Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                  |

| 4.4.2 RS-232 Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73                                                               |

| 4.5 Power Control Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                  |

| 4.6 RTC Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |

| 4.7 Flash EPROM Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |

| 4.8 LED Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |

| 4.9 LCD Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |

| 4.10 Keypad Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |

| 4.11 Additional Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |

| Appendix A: Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89                                                               |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b><br>90                                                  |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b><br>90                                                  |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b><br>90<br>90                                            |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b><br>90<br>90                                            |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b><br>90<br>90                                            |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b>                                                        |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b>                                                        |

| Appendix A: Troubleshooting  A.1 Out of the Box  A.2 Dynamic C Does Not Start  A.3 LP3100 Repeatedly Resets  A.4 Dynamic C Loses Link with Application Program  Appendix B: Specifications  B.1 General Specifications                                                                                                                                                                                                                                                                                                                 | <b>89</b> 90 90 91 91 91 93 94                                   |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b> 90 90 91 91 91 93 94 97                                |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b> ————————————————————————————————————                   |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b> ————————————————————————————————————                   |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>89</b> 90 90 91 91 91 93 94 97 98 99 100                      |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 90 90 91 91 91 93 94 97 98 99 100 101                         |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 90 90 91 91 91 93 94 97 98 99 100 101                         |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 90 90 91 91 91 93 94 97 98 99 100 101                         |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 90 90 91 91 91 93 94 97 98 99 100 101                         |

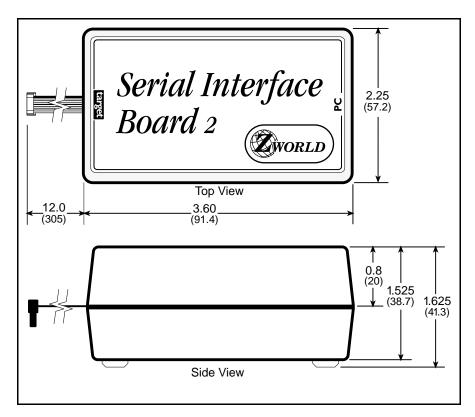

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 90 90 91 91 93 94 97 98 99 100 101 102                        |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 90 90 91 91 91 93 94 97 98 99 100 101 102 105 105             |

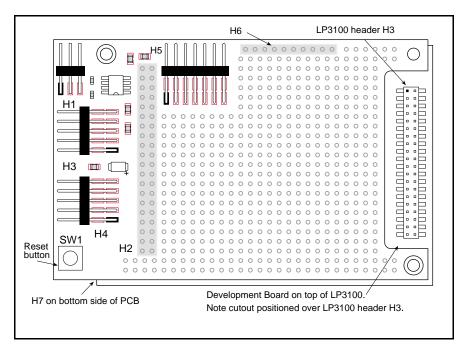

| Appendix A: Troubleshooting  A.1 Out of the Box A.2 Dynamic C Does Not Start A.3 LP3100 Repeatedly Resets A.4 Dynamic C Loses Link with Application Program  Appendix B: Specifications B.1 General Specifications B.2 Analog Inputs B.3 Mechanical Specifications B.3.1 LP3100 Mounting Plate Dimensions B.4 Header Pinouts 2.4.1 LCD Connections B.5 Jumper Settings  Appendix C: Serial Interface Board C.1 Features C.2 External Dimensions  Appendix D: Development Board D.1 Overview D.1.1 LCD Interface D.1.2 Keypad Interface | 89 90 90 91 91 91  93 94 97 98 99 100 101 102  103 104 105       |

| Appendix A: Troubleshooting  A.1 Out of the Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 90 90 91 91 91 93 94 97 98 99 100 101 102 105 107 108 109 110 |

| D.1.5 Power Supply Input Connector            | 112 |

|-----------------------------------------------|-----|

| D.1.6 Reset Switch                            |     |

| D.1.7 Prototyping Area                        |     |

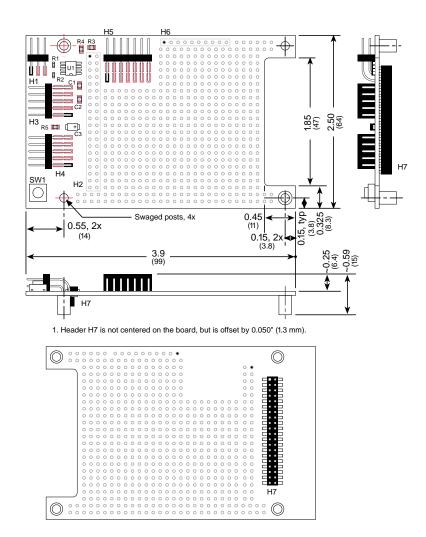

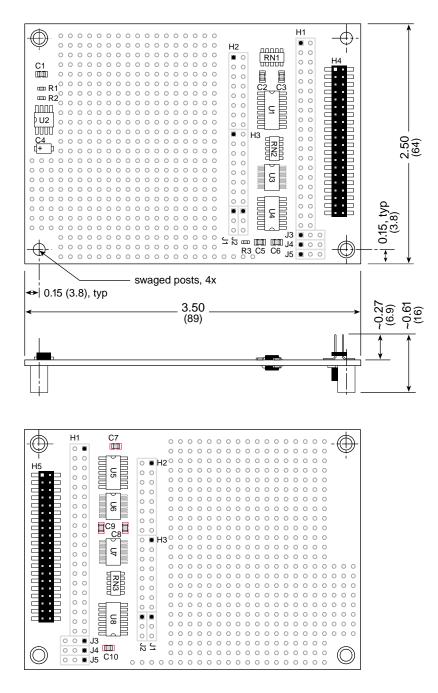

| D.2 Dimensions                                | 113 |

| Appendix E: LPBus Prototyping Board           | 115 |

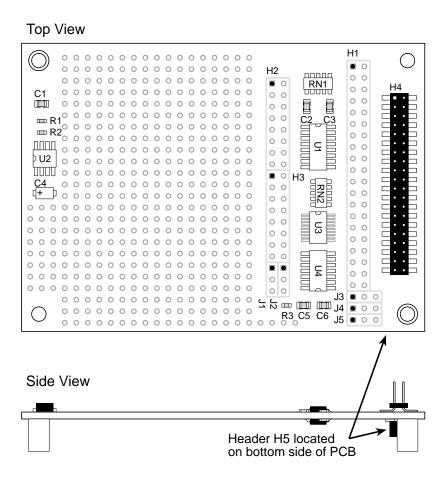

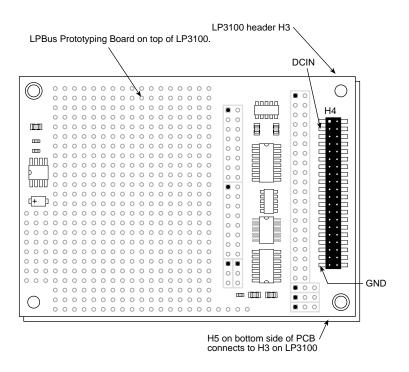

| E.1 Overview                                  | 116 |

| E.1.1 Installation of LPBus Prototyping Board |     |

| E.1.2 Prototyping Area                        |     |

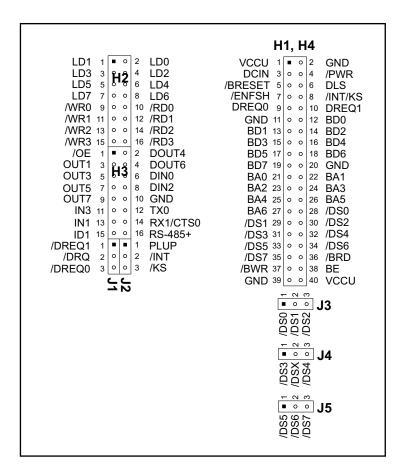

| E.1.3 LPBus Signals                           | 118 |

| E.2 Design Considerations                     |     |

| E.2.1 Electrical                              |     |

| E.2.2 Board ID                                |     |

| E.2.3 No Connect Pins                         |     |

| E.2.4 Use of DS Lines<br>E.2.5 DMA            |     |

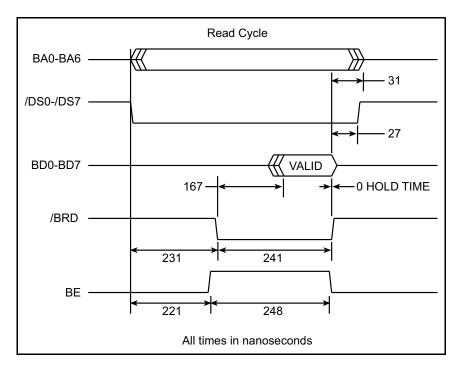

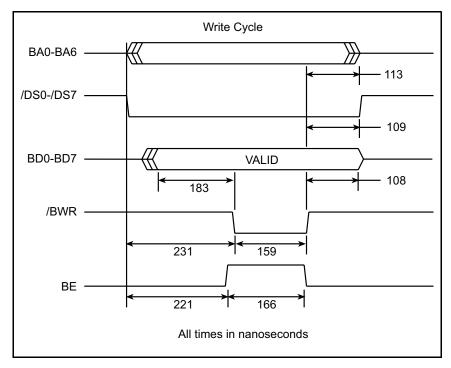

| E.2.3 DMA<br>E.3 LPBus Timing                 |     |

| E.4 LPBus DMA                                 |     |

| E.5 Dimensions                                |     |

| E.5 Difficustoffs                             | 123 |

| Appendix F: Power Management                  | 127 |

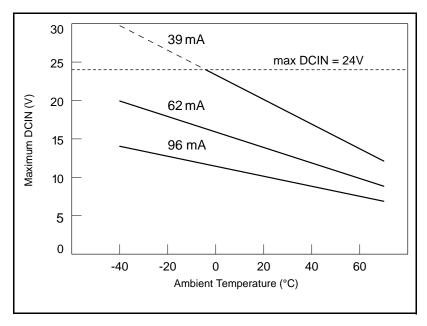

| F.1 Input Voltage                             | 128 |

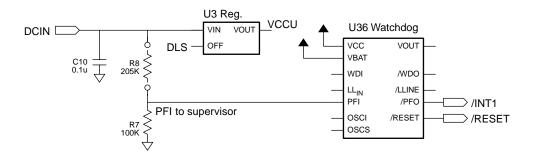

| F.2 Power-Failure Detection                   | 130 |

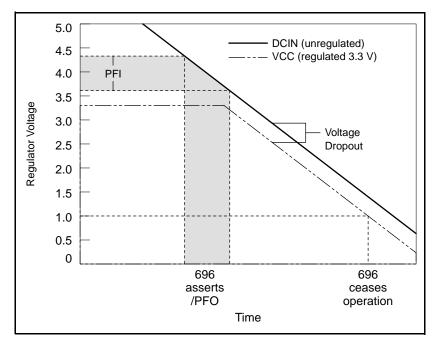

| F.2.1 Power Failure Sequence of Events        | 130 |

| Appendix G: Interrupts                        | 133 |

| G.1 Enabling/Disabling Interrupts             |     |

| G.2 Interrupt Service Routines                |     |

| G.3 Interrupt Vectors                         |     |

|                                               |     |

| G.4 Jump Vectors                              | 130 |

| Appendix H: Addresses                         | 137 |

| H.1 Simulated EEPROM Addresses                | 138 |

| H.2 Microprocessor Register Addresses         | 138 |

| H.3 LP3100 Peripheral Addresses               |     |

| Appendix I: Optional Second Flash EPROM       | 141 |

|                                               |     |

| I.1 Optional Flash EPROM                      |     |

| I.2 Sample Program                            | 143 |

| Index                                         | 145 |

|                                               |     |

# **ABOUT THIS MANUAL**

This manual provides instructions for installing, testing, configuring, and interconnecting the LP3100 low-power controller.

Instructions to get started using Dynamic C software programming functions as well as complete C and Dynamic C references and programming resources are referenced when necessary.

## **Assumptions**

Assumptions are made regarding the user's knowledge and experience in the following areas:

- Ability to design and engineer the target system that an LP3100 will control.

- Understanding of the basics of operating a software program and editing files under Windows on a PC.

- Knowledge of the basics of C programming.

For a full treatment of C, refer to the following texts:

The C Programming Language by Kernighan and Ritchie (published by Prentice-Hall).

and/or

C: A Reference Manual by Harbison and Steel (published by Prentice-Hall).

• Knowledge of basic Z80 assembly language and architecture..

For documentation from Zilog, refer to the following texts:

Z180 MPU User's Manual **Z180 Serial Communication Controllers** Z80 Microprocessor Family User's Manual.

# Acronyms

Table 1 lists and defines the acronyms that may be used in this manual.

Table 1. Acronyms

| Acronym | Meaning                                                           |

|---------|-------------------------------------------------------------------|

| EPROM   | Erasable Programmable Read-Only Memory                            |

| EEPROM  | Electronically Erasable Programmable Read-Only<br>Memory          |

| LCD     | Liquid Crystal Display                                            |

| LED     | Light-Emitting Diode                                              |

| NMI     | Nonmaskable interrupt                                             |

| PIO     | Parallel Input/Output<br>(Individually programmable input/output) |

| PRT     | Programmable Reload Timer                                         |

| RAM     | Random Access Memory                                              |

| RTC     | Real-Time Clock                                                   |

| SIB     | Serial Interface Board                                            |

| SRAM    | Static Random Access Memory                                       |

| UART    | Universal Asynchronous Receiver Transmitter                       |

# **Icons**

Table 2 displays and defines icons that may be used in this manual.

Table 2. Icons

| Icon        | Meaning         | lcon | Meaning      |

|-------------|-----------------|------|--------------|

| 66          | Refer to or see |      | Note         |

| <b>a</b>    | Please contact  | Tip  | Tip          |

| $\triangle$ | Caution         | A    | High Voltage |

|             | Factory Default |      |              |

## **Conventions**

Table 3 lists and defines the typographic conventions that may be used in this manual.

Table 3. Typographic Conventions

| Example   | Description                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| while     | Bold Courier font indicates a program, a fragment of a program, or a Dynamic C keyword or phrase.                                                   |

| // IN-01  | Program comments are in normal Courier font.                                                                                                        |

| Italics   | Courier italics indicate that something should be typed instead of the italicized words (e.g., type a file name where <i>filename</i> is shown).    |

| Edit      | Bold sans serif font indicates a menu or menu selection.                                                                                            |

|           | An ellipsis indicates that (1) irrelevant program text is omitted for brevity, or that (2) the preceding program text may be repeated indefinitely. |

| [ ]       | Square brackets in a C function's definition or program segment indicate that the enclosed directive is optional.                                   |

| < >       | Angle brackets are used to enclose classes of terms.                                                                                                |

| a   b   c | A vertical bar indicates that a choice should be made from among the items listed.                                                                  |

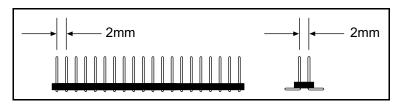

## Pin Number 1

A black square indicates pin 1 of all headers. Pin 1

### Measurements

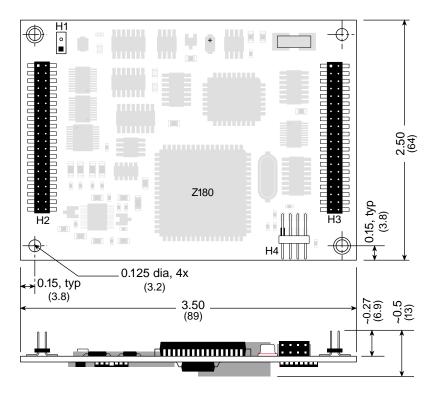

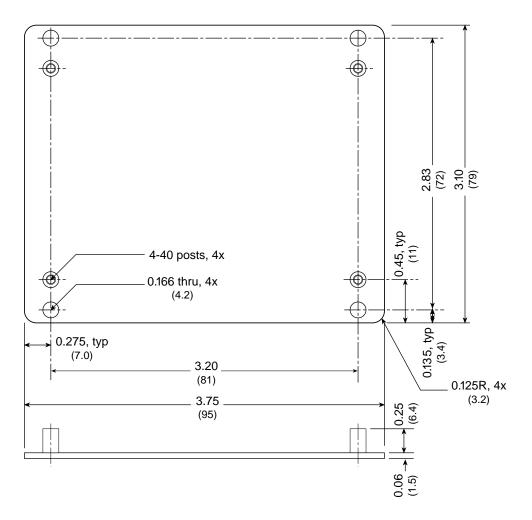

All diagram and graphic measurements are in inches followed by millimeters enclosed in parenthesis.

# CHAPTER 1. OVERVIEW

Chapter 1 provides an overview and description of the LP3100 low-power controllers. The following sections are included.

- Features

- Standard Models

- Flexibility and Customization

- Subsystems

- Development and Evaluation Tools

- Software

- CE Compliance

The LP3100 is a low-power controller designed for use in low-power and battery-powered embedded applications.

Typical applications for the LP3100 include the following:

- Remote data acquisition

- Portable instrumentation

- Handheld equipment

- Solar powered instrumentation

- Battery powered systems

#### 1.1 Features

The LP3100 has many features, including the following:

- Low-voltage design (3.3 V operation)

- Flexible power control system

- 6.144 MHz or 3.072 MHz system clock (software selectable)

- Flash EPROM (up to 512K)

- Static RAM with battery backup capability (up to 512K)

- 2 serial channels (RS-232 and RS-485)

- 4-channel 12-bit analog inputs with signal conditioning

- 4 digital inputs

- 8 digital outputs

- 8 configurable digital inputs/outputs (software configurable)

- Real-time clock

- Microprocessor supervisor IC

- Expansion bus (LPBus)

- Onboard diagnostic LED

- Dedicated programming port for Dynamic C

For details on customizing the LP3100, call a Z-World Sales Representative at (530) 757-3737.

#### 1.2 Standard Models

The LP3100 Series currently has four members: LP3100, LP3110, LP3120, and LP3130. Table 1 lists the features of each model.

Table 1. LP3100 Series Model Features

| Model  | Features                                                                                                                                                                              |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP3100 | 6.144 MHz clock, 512K flash EPROM, 128K SRAM, 2 RS-232 channels, RS-485 driver, 4-channel 12-bit A/D converter, 20 digital input/output lines, real-time clock, LPBus expansion port. |

| LP3110 | LP3100 with 256K flash EPROM, 32K SRAM, no RS-485 driver.                                                                                                                             |

| LP3120 | LP3100 with 256K flash EPROM, 32K SRAM, no RS-485 driver, no A/D converter.                                                                                                           |

| LP3130 | LP3100 with 256K flash EPROM, 32K SRAM, no RS-485 driver, no A/D converter, no real-time clock, no 5 V regulator, no LPBus expansion port.                                            |

## 1.3 Flexibility and Customization

The LP3100 was designed for application flexibility. Two levels of flexibility allow appropriate selection of the I/O for a specific application's needs:

## • Flexibility Level 1 — Out of the Box

Jumper-configurable serial communication channels.

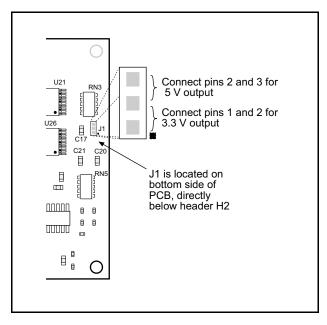

Jumper-selectable supply voltage to output latches allows control of the output voltage level (3.3 V or 5 V).

Bias and gain for conditioned analog input channel conditioning circuits configured with resistors.

Flexible digital input/output channels (eight channels) configurable as inputs or outputs under software control.

Software-controlled subsystem power (analog inputs, RS-232, memory and microprocessor, real-time clock) allows selective power-down for maximum power savings.

#### • Flexibility Level 2 — Customization

For quantity orders, Z-World can tailor the LP3100 to meet custom specifications. Once the application prototype is defined, Z-World's automated surface-mount manufacturing facility can build the LP3100 with the exact hardware a specific application requires.

# 1.4 Subsystems

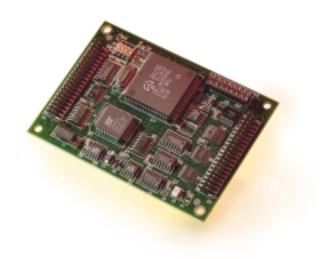

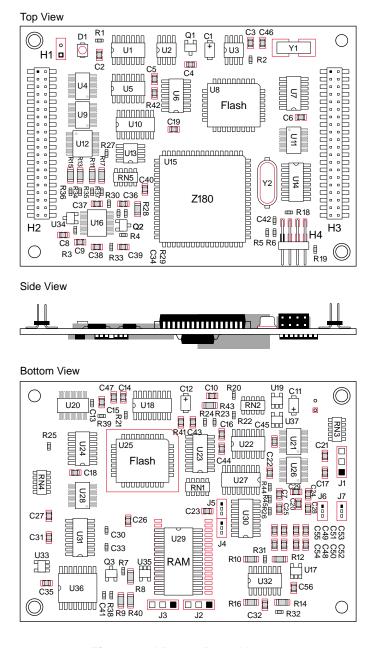

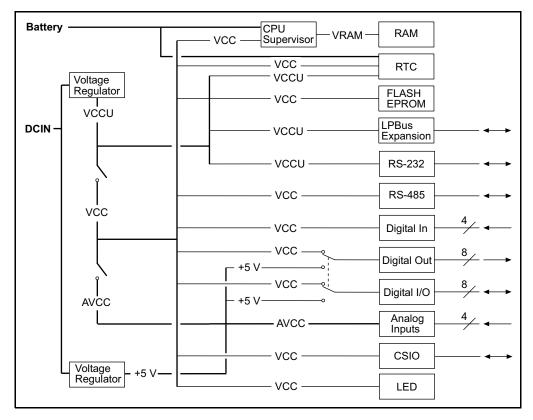

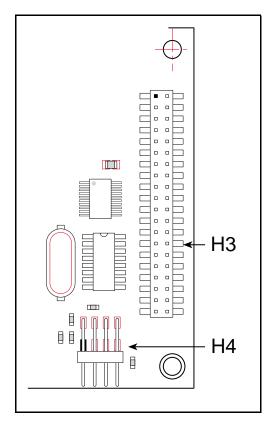

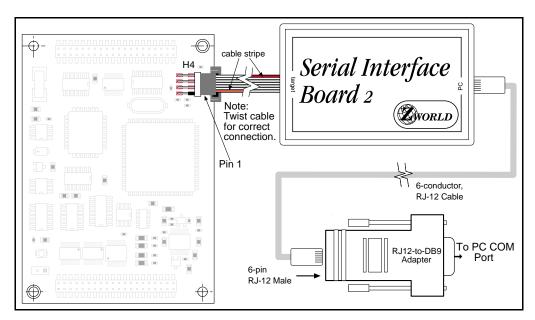

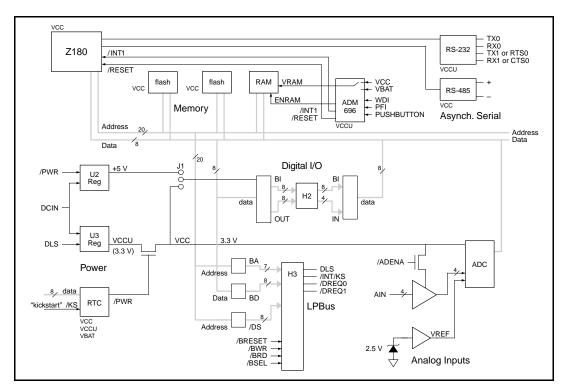

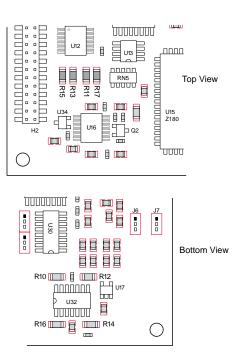

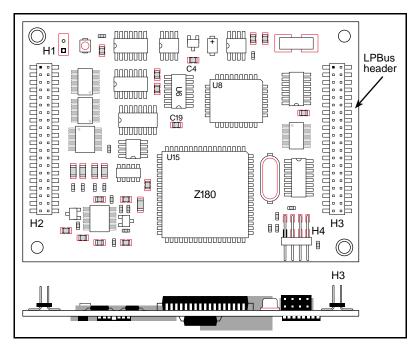

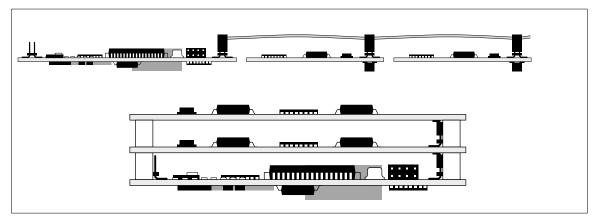

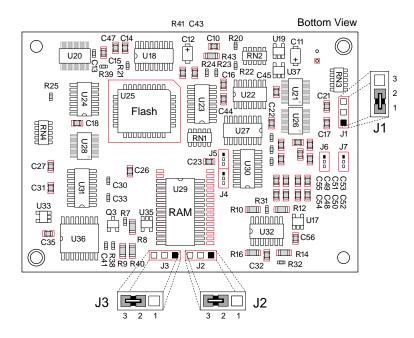

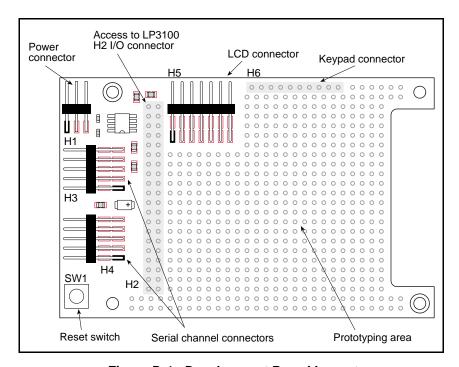

The LP3100 consists of several subsystems, including a microprocessor, memory, power control, digital inputs and outputs, analog inputs, serial communication channels, a real-time clock, and an LPBus expansion port. Figure 1 shows the board layout and Figure 2 illustrates the LP3100 subsystems.

Figure 1. LP3100 Board Layout

Figure 2. Subsystems Block Diagram

#### 1.4.1 Microprocessor, Memory, and Support Circuits

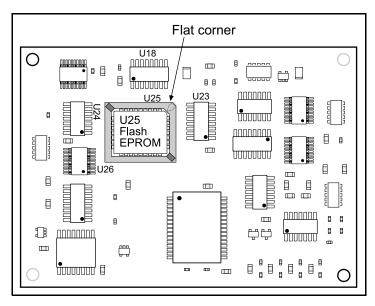

The LP3100 uses a low-voltage microprocessor running at either 6.144 MHz or 3.072 MHz. Up to 512K of flash EPROM and 512K of static RAM are available. Up to 256K of the flash EPROM can be used for data-logging. A microprocessor supervisor IC provides protection against software bugs and glitches in addition to providing a battery-backup capability and brownout protection for the static RAM.

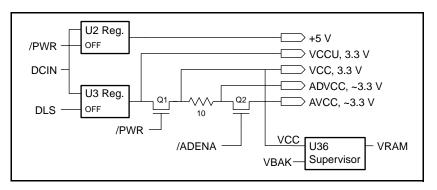

### 1.4.2 Power Control

Controlling the power supplies for the LP3100 subsystems enhances low-power operation. Most subsystems on the LP3100, including the microprocessor and memory, can be powered down or operated in low-power modes. The low-power mode virtually eliminates current draw for a subsystem that is not being used.

#### 1.4.3 Digital Inputs/Outputs

The LP3100 series has the following three types of digital inputs/outputs.

- 1. **Digital Inputs -** Four dedicated digital input channels that include pull-up resistors. DIN0 can be used to wake the board from sleep mode.

- 2. **Digital Outputs -** Eight dedicated digital outputs that can be configured for either 3.3 V or 5 V output and can sink or source up to 8 mA.

3. **Configurable Digital Inputs/Outputs -** Eight digital channels that can be configured as either inputs or outputs with the same specifications as the dedicated inputs and outputs.

#### 1.4.4 Analog Inputs

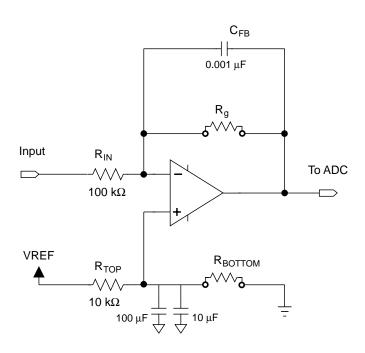

The LP3100 has four conditioned analog inputs. The inputs are multiplexed into a 12-bit ADC.

By default, the analog inputs have an input range of 0–10 volts. The inputs can be configured for almost any arbitrary range by replacing two configuration resistors.

#### 1.4.5 Serial Channels

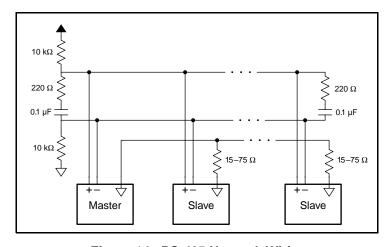

The LP3100 has two serial channels. One channel can be configured as either a 5-wire RS-232 or as a 3-wire RS-232. The other channel can be configured as a 3-wire RS-232 or as a 2-wire RS-485. The serial channels operate at speeds up to 38,400 bps using a 6.072 MHz system clock.

#### 1.4.6 Real-Time Clock

Date and time-of-day information can be read from the real-time clock (RTC). The RTC provides the date and the day of the week in addition to the hour, minute, and second. The RTC can also be used to wake the LP3100 from sleep mode or to provide a periodic alarm.

#### **1.4.7 LPBus**

The LPBus provides an expansion capability for the LP3100. The LPBus provides address, data, and control signals for controlling add-on expansion modules.

### 1.4.8 LED