DS07-13601-5E

# 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16L MB90630A Series

# MB90632A/634A/P634A

#### **■ DESCRIPTION**

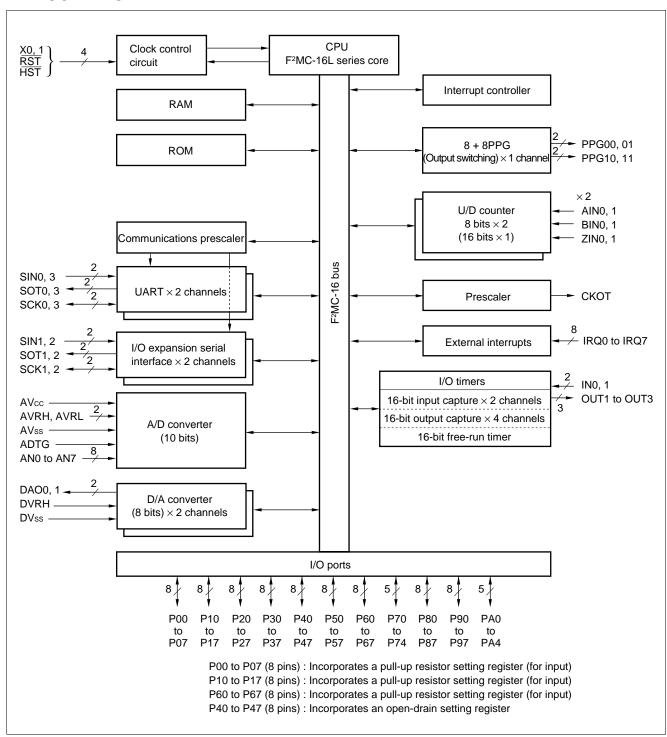

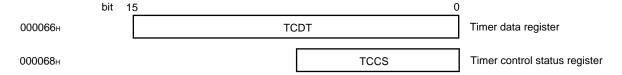

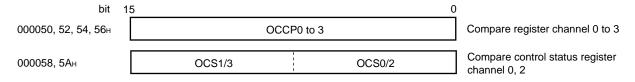

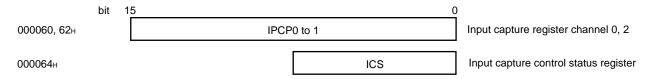

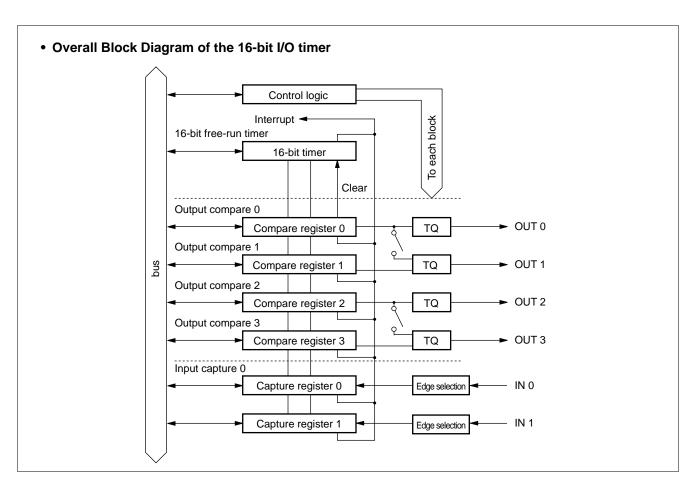

The MB90630A series are 16-bit microcontrollers designed for high speed real-time processing in consumer product applications such as controlling video cameras, VCRs, or copiers. The series uses the F<sup>2</sup>MC\*-16L CPU. The chips incorporate an eight channels 10-bit A/D converter, two channels 8-bit D/A converter, UART two channels, two channels serial interface, 8/16-bit up/down counter, 16-bit I/O timer (two channels input capture, four channels output compare, and one channel 16-bit free-run timer).

\*: F2MC stands for FUJITSU Flexible Microcontroller.

#### **■ FEATURES**

F2MC-16L CPU

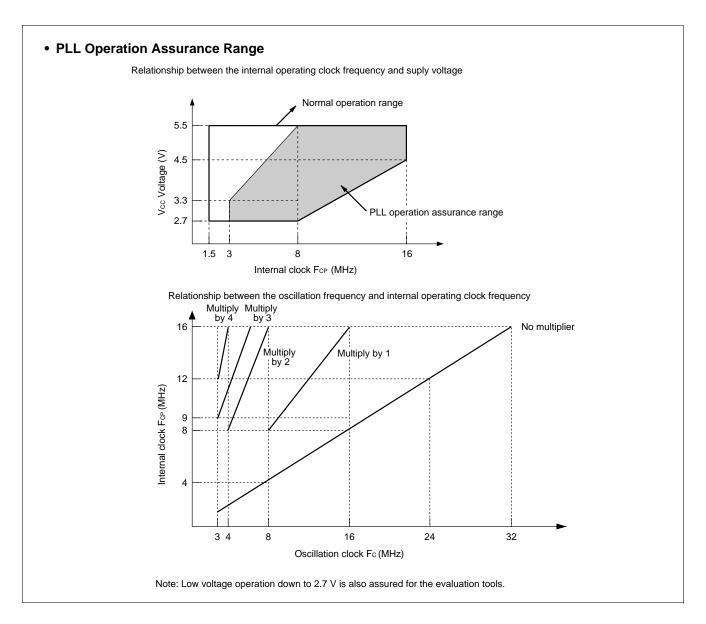

- Minimum execution time: 62.5 ns/4 MHz oscillation (Uses PLL clock multiplication), maximum multiplier = 4

- Instruction set optimized for controller applications

Object code compatibility with F<sup>2</sup>MC-16(H)

Wide range of data types (bit, byte, word, and long word)

Improved instruction cycles provide increased speed

Additional addressing modes: 23 modes

High code efficiency

Access mothods (bank access, linear pointer)

(Continued)

### **■ PACKAGE**

### (Continued)

High precision operations are enhanced by use of a 32-bit accumulator Extended intelligent I/O service (access area extended to 64 KB) Maximum memory space: 16 MB

• Enhanced high level language (C) and multitasking support insturctions

Use of a system stack pointer

Enhanced pointer indirect instructions

Barrel shift instructions

- Improved execution speed: Four byte instruction queue

- Powerful interrupt function

- Automatic data transfer function that does not use insturction (IIOS)

Internal peripherals

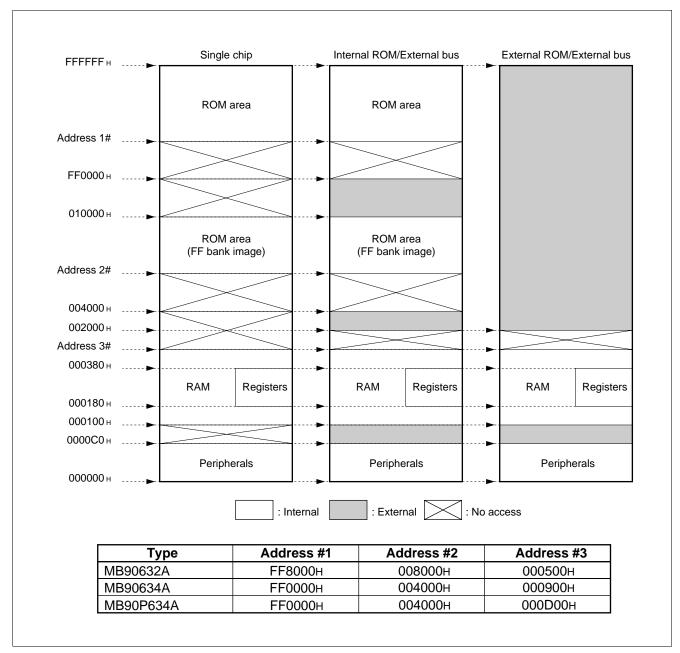

• ROM: 32 Kbytes (MB90632A)

64 Kbytes (MB90634A)

One-time PROM: 64 Kbytes (MB90P634A)

• RAM: 1 Kbytes (MB90632A)

2 Kbytes (MB90634A)

3 Kbytes (MB90P634A)

- General-purpose ports: 82 ports max.

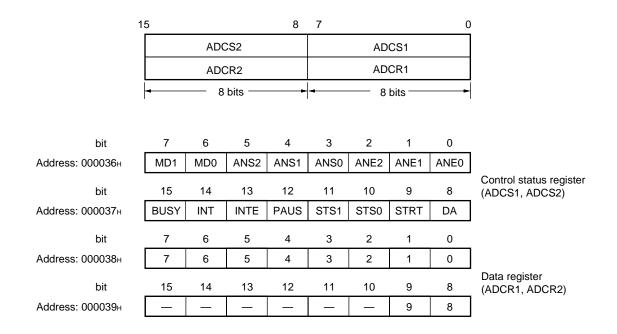

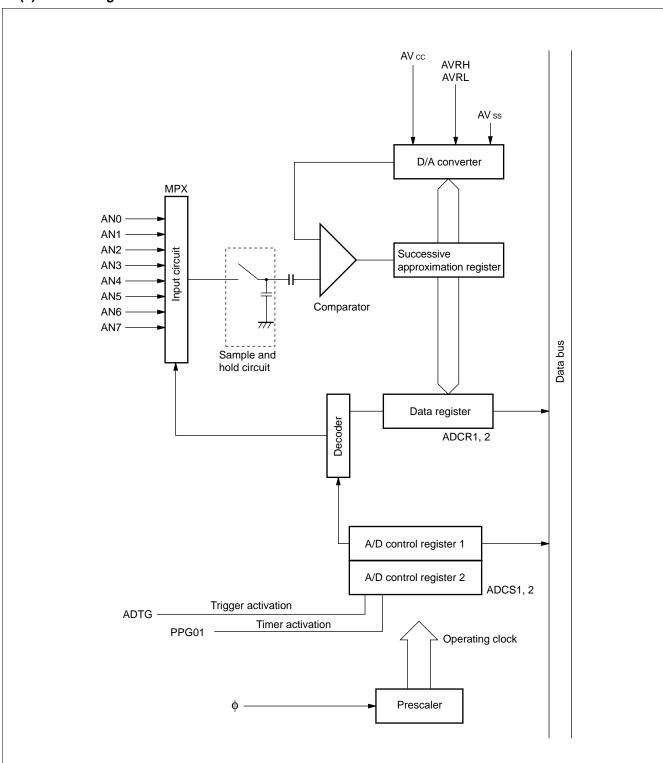

- 10-bit A/D converter (RC successive approximation): eight channels (10-bit resolution, conversion time = 5.2 μs at 4 MHz with a × 4 multiplier)

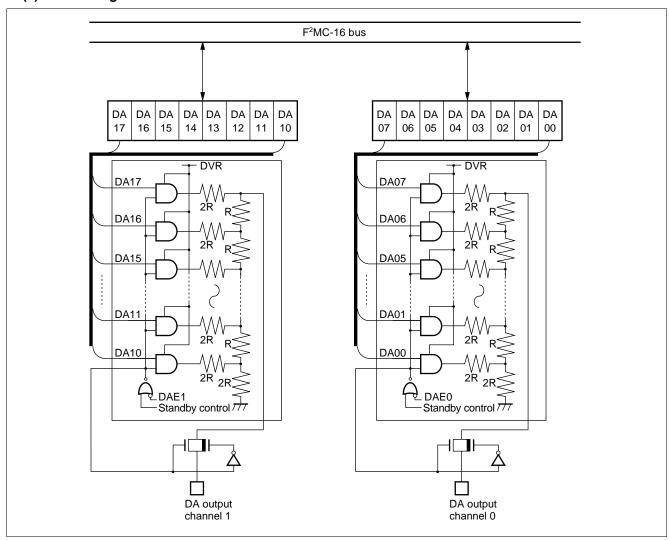

- 8-bit D/A converter two channels (8-bit resolution)

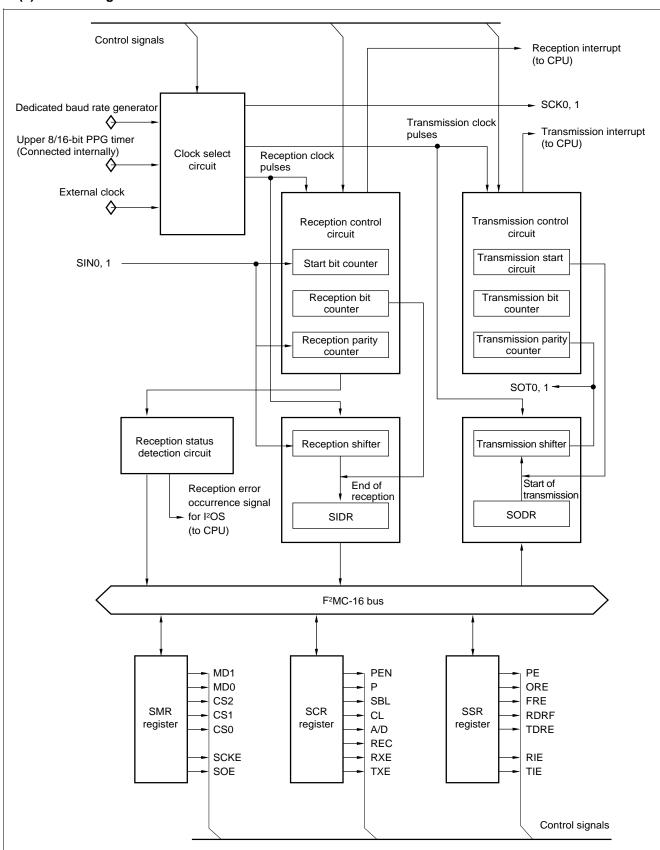

- UART (can also be used as a serial port) two channels

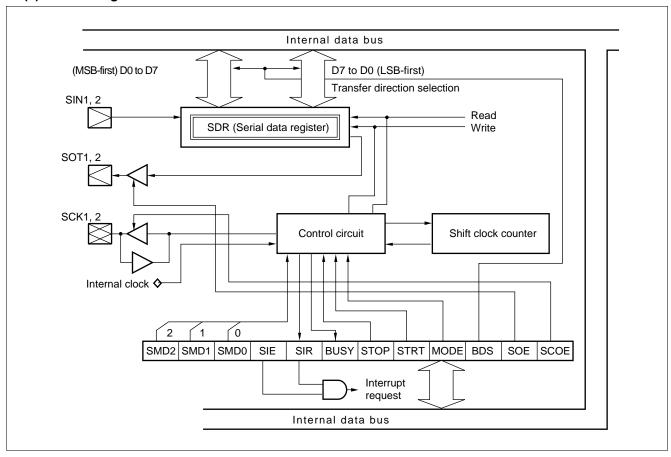

- I/O expansion serial interface two channels

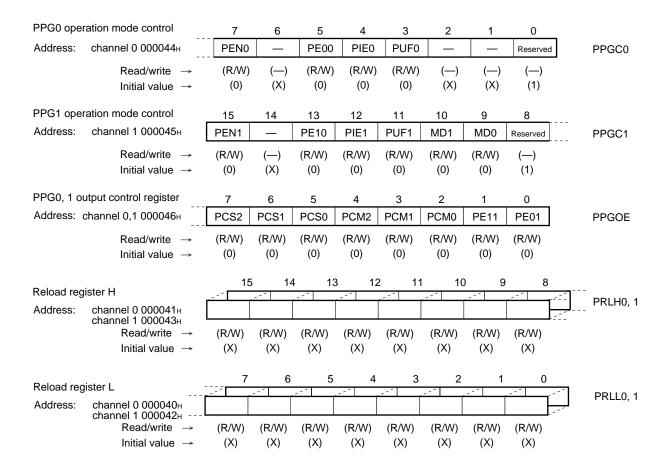

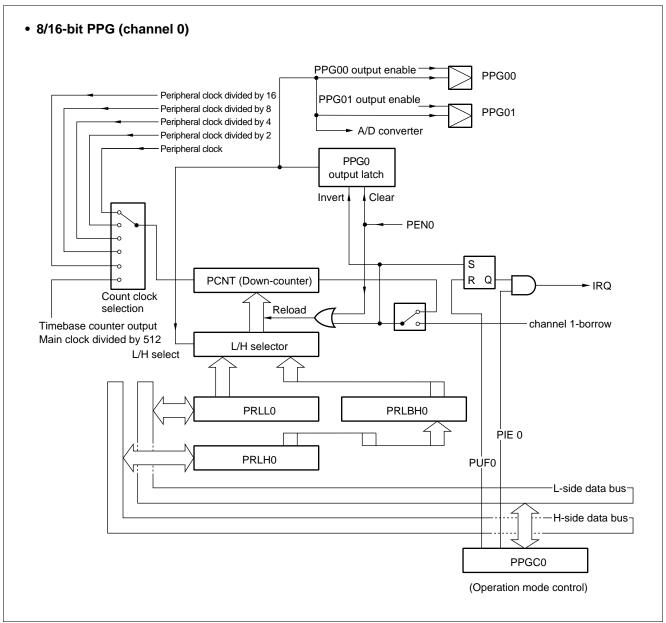

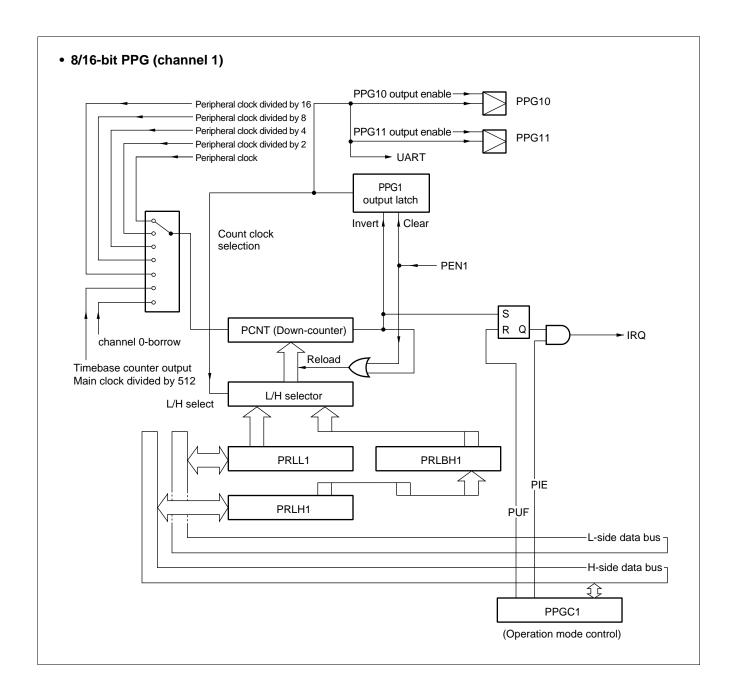

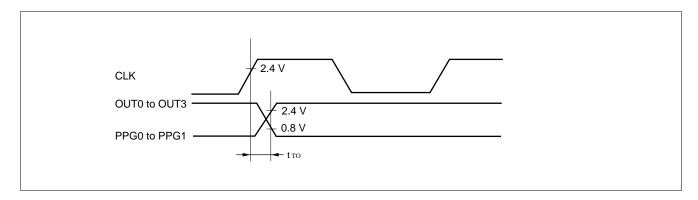

- 8/16-bit PPG (can be set to either 8-bit × two channels or 16-bit × one channel) one channel

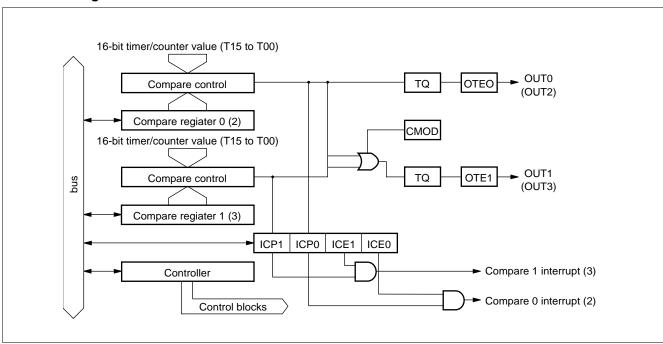

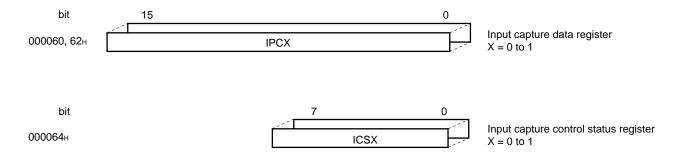

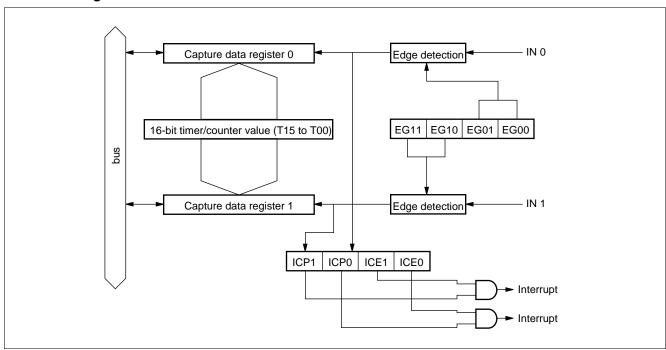

- 16-bit I/O timer one channel

(two channels input capture, four channels output compare, and one channel free-run timer)

- Clock output generator

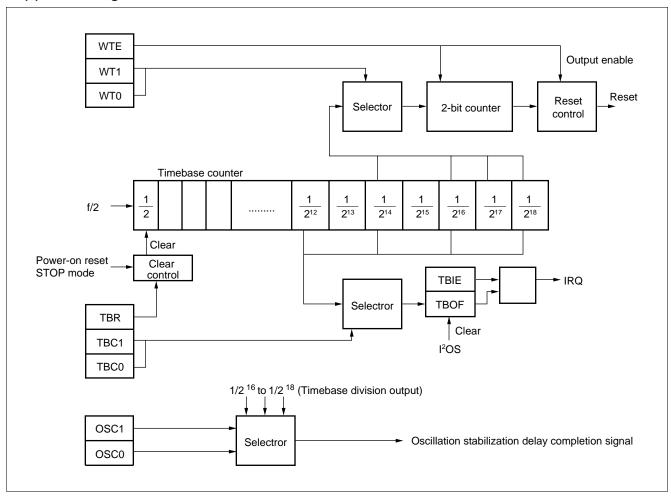

- Timebase counter/watchdog timer (18-bit)

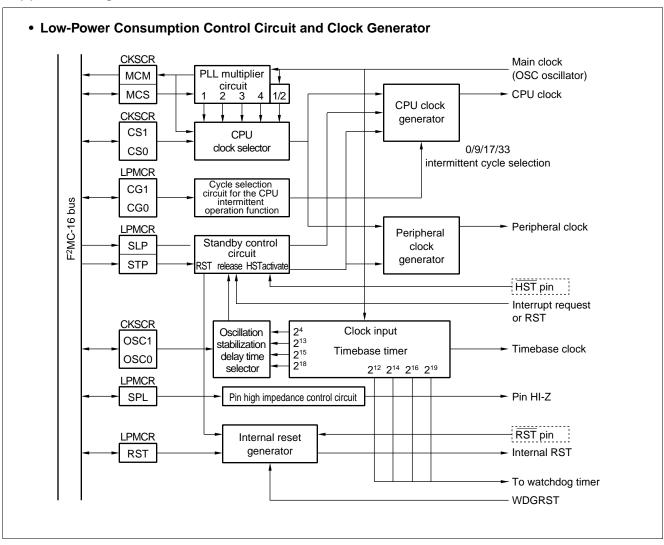

- Low-power consumption modes

- The device types are classified by the initial value of the oscillation stabilization delay time.

Oscillation stabilization delay time initial value = 2.05 ms: MB90630A series (MB90632A/634A/P634A)

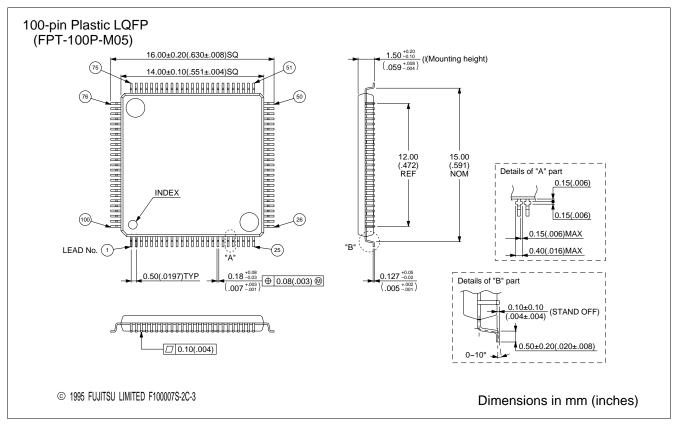

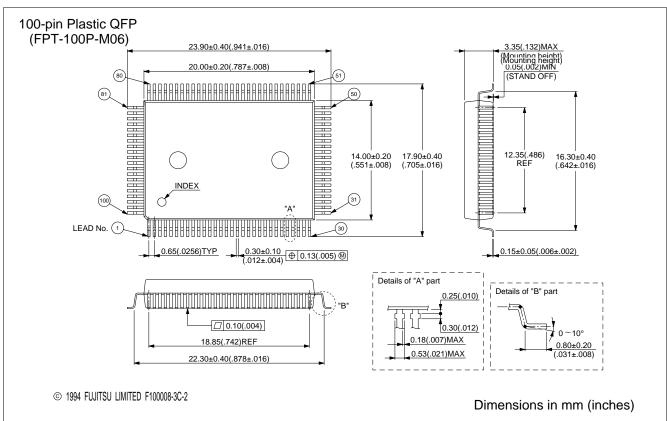

- Package: LQFP-100 (QFP-100 planned)

- CMOS technology

## **■ PRODUCT LINEUP**

| Part number                                | MB90P634A                                                                                                                                                                                                                                        | MB90632A                                                                                         | MB90634A             |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Parameter                                  |                                                                                                                                                                                                                                                  |                                                                                                  |                      |  |  |  |

| Classification                             | OTPROM Mask ROM                                                                                                                                                                                                                                  |                                                                                                  |                      |  |  |  |

| ROM size                                   | 64 Kbyte                                                                                                                                                                                                                                         | 32 Kbyte                                                                                         | 64 Kbyte             |  |  |  |

| RAM size                                   | 3 Kbyte                                                                                                                                                                                                                                          | 1 Kbyte                                                                                          | 2 Kbyte              |  |  |  |

| CPU functions                              | Number of instructio<br>Instruction bit length<br>Instruction length<br>Data bit length<br>Minimum execution t<br>Interrupt processing                                                                                                           | : 8/16 bits<br>: 1/7 bytes<br>: 1/4/8/16/32 bits<br>:ime : 62.5 ns/4 MHz<br>time : 1000 ns/16 MH | (PLL multiplier = 4) |  |  |  |

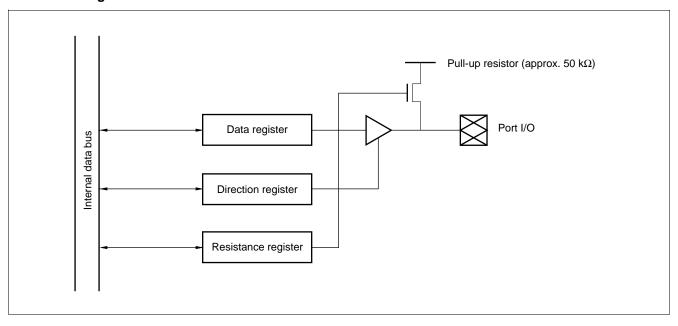

| Ports                                      | I/O ports (CMOS/TT<br>Input pull-up resistor<br>Can be set as open-                                                                                                                                                                              |                                                                                                  |                      |  |  |  |

| Package                                    |                                                                                                                                                                                                                                                  | FPT-100P-M05<br>FPT-100P-M06                                                                     |                      |  |  |  |

| A/D converter                              |                                                                                                                                                                                                                                                  | 2 μs conversion time (at 4 MHz<br>approximation, 8 channels (mu                                  |                      |  |  |  |

| D/A converter                              | R-2                                                                                                                                                                                                                                              | 8-bit resolution<br>2R type, 2 channels (independe                                               | ent)                 |  |  |  |

| UART                                       | Full-duplex, double-buffered (8-bit), internal baud rate correction circuit that uses the operating clock  NRZ-type transfer, supports MIDI frequencies, 2 channels                                                                              |                                                                                                  |                      |  |  |  |

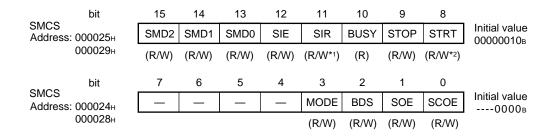

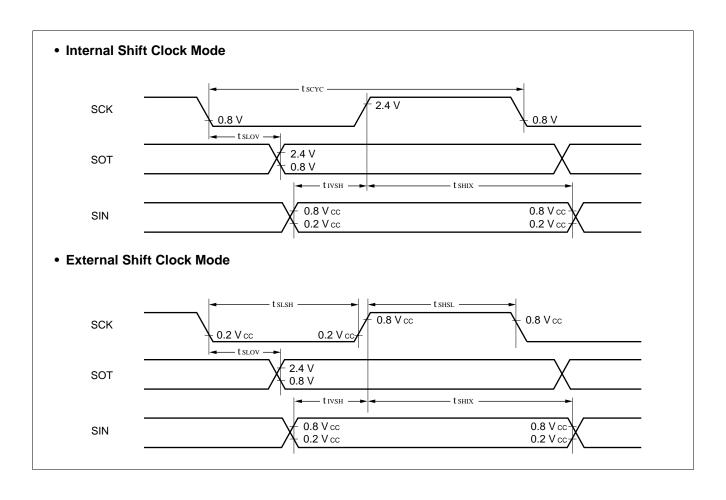

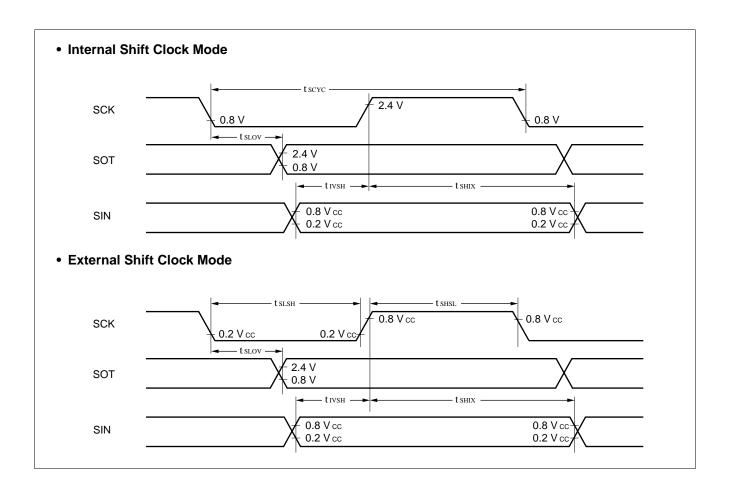

| Serial interface                           | 8-bit data register. LSB-first or MSB-first operation can be selected.  The transfer shift clock can be input externally.  The internal shift clock includes a built-in operating clock correction circuit. 1 channel                            |                                                                                                  |                      |  |  |  |

| 8/16-bit PPG                               | Can operate as two independent channels in 8-bit mode. Can also be used as a single-channel 16-bit PPG. 1 channel                                                                                                                                |                                                                                                  |                      |  |  |  |

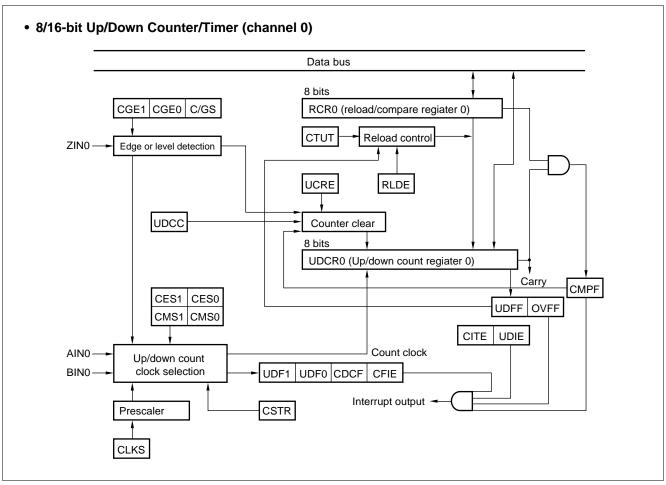

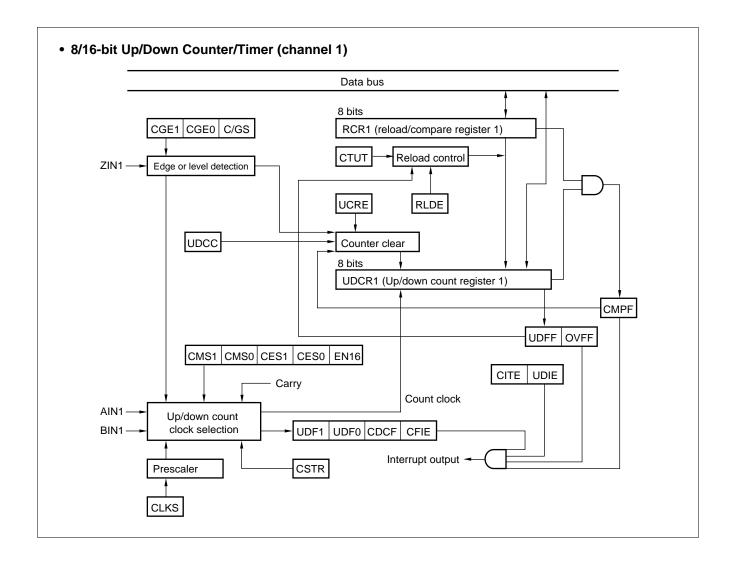

| 8/16-bit up/down counter                   | 6 event inputs. Can operate as two independent 8-bit up/down counter channels. Can also be used as a single-channel 16-bit counter. Includes reload and compare functions.  1 channel                                                            |                                                                                                  |                      |  |  |  |

| 16-bit I/O timer                           | Consists of 2 $\times$ input capture, 4 $\times$ output compare, and 1 $\times$ free-run timer. 1 channel                                                                                                                                        |                                                                                                  |                      |  |  |  |

| Timer functions                            | Time                                                                                                                                                                                                                                             | ebase timer/watchdog timer (18                                                                   | 3-bit)               |  |  |  |

| Low-power consumption modes                | Includes sle                                                                                                                                                                                                                                     | eep, stop, and hardware standl                                                                   | by functions         |  |  |  |

| Oscillation<br>stabilization delay<br>time | The initial value of the oscillation stabilization delay time is 64 ms.  The oscillation stabilization delay time can also be set to 0 ms, 2.05 ms, 8.19 ms, or 64 ms (for an crystal oscillator).  The MB90630A series are for FAR oscillators. |                                                                                                  |                      |  |  |  |

| External interrupt                         | 8 inputs External interrupt mode (Interrupts can be generated from four different types of request signal)                                                                                                                                       |                                                                                                  |                      |  |  |  |

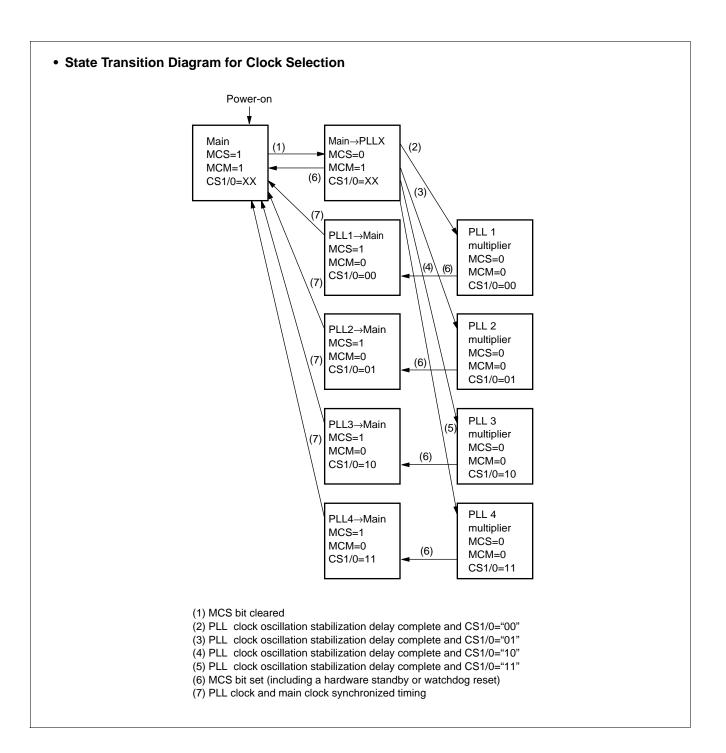

| PLL function                               | Selectable multiplier: 1/2/3/4 (Set a multiplier that does not exceed the assured operation frequency range.)                                                                                                                                    |                                                                                                  |                      |  |  |  |

| Other                                      | V <sub>PP</sub> is shared with the MD2 pin (for EPROM programming)                                                                                                                                                                               | _                                                                                                | _                    |  |  |  |

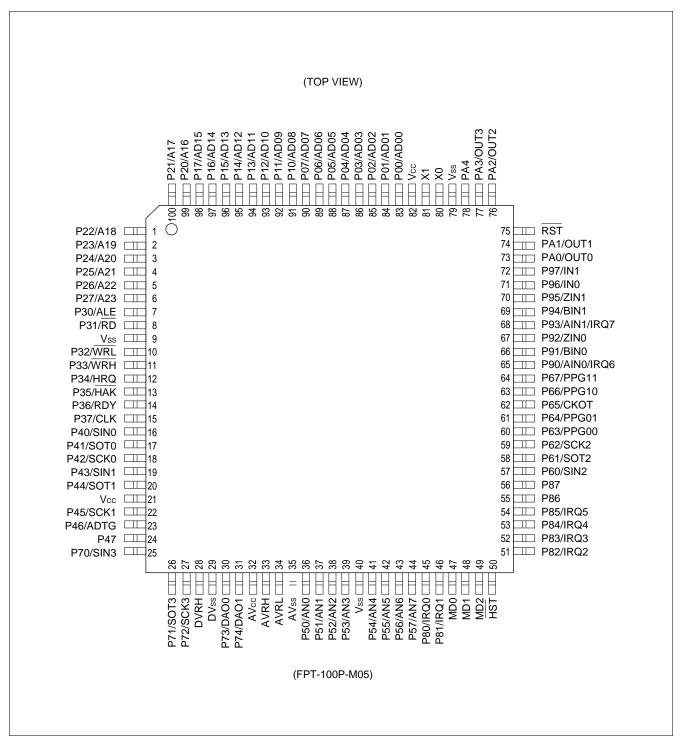

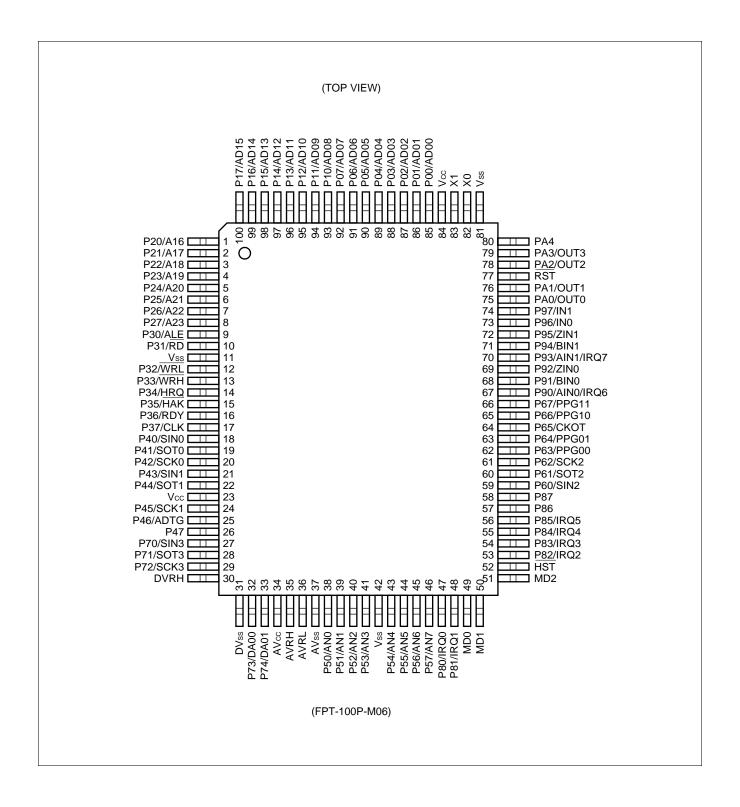

### **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTION**

| Pin no.            |           |              | Circuit     |                                                                                                                                                                                                                                        |  |

|--------------------|-----------|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP*1             | QFP*2     | Pin name     | type        | Function                                                                                                                                                                                                                               |  |

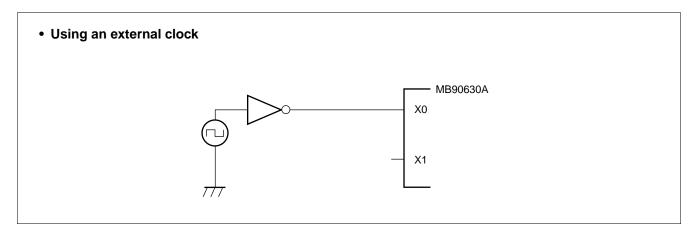

| 80                 | 82        | X0           | Α           | Oscillator pin                                                                                                                                                                                                                         |  |

| 81                 | 83        | X1           | Α           | Oscillator pin                                                                                                                                                                                                                         |  |

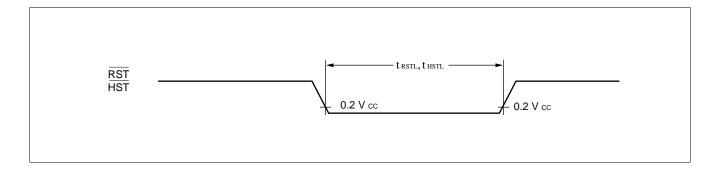

| 50                 | 52        | HST          | С           | Hardware standby input pin                                                                                                                                                                                                             |  |

| 75                 | 77        | RST          | В           | Reset input pin                                                                                                                                                                                                                        |  |

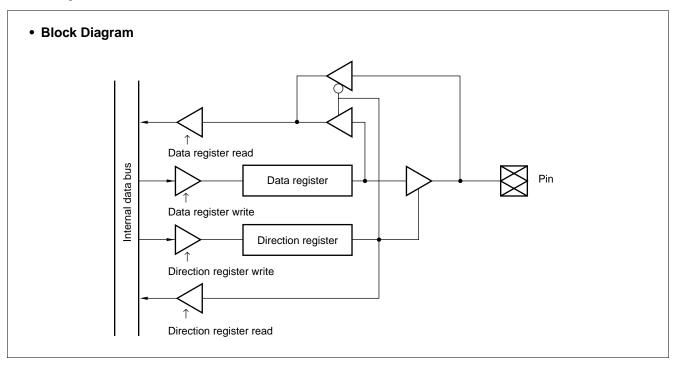

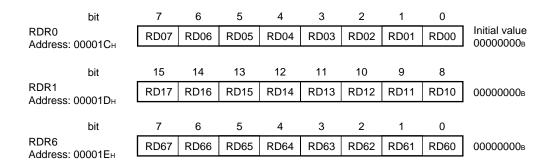

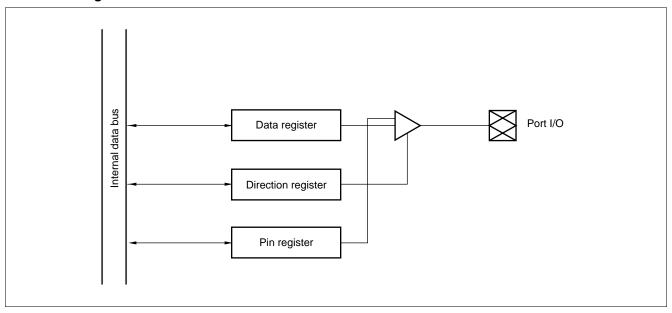

| 83 to 90           | 85 to 92  | P00 to P07   | D<br>(STBC) | General-purpose I/O ports Pull-up resistors can be set (RD07 to RD00 = "1") using the pull-up resistor setting register (RDR0). The setting does not apply for ports set as outputs (D07 to D00 = "1": invalid at the output setting). |  |

|                    |           | AD00 to AD07 |             | In external bus mode, the pins function as the lower data I/O or lower address outputs (AD00 to AD07).                                                                                                                                 |  |

| 91 to 98           | 93 to 100 | P10 to P17   | D<br>(STBC) | General-purpose I/O ports Pull-up resistors can be set (RD17 to RD10 = "1") using the pull-up resistor setting register (RDR1). The setting does not apply for ports set as outputs (D17 to D10 = "1": invalid at the output setting). |  |

|                    |           | AD08 to AD15 |             | In 16-bit external bus mode, the pins function as the upper data I/O or middle address outputs (AD08 to AD15).                                                                                                                         |  |

| 99, 100,<br>1 to 6 | 1 to 8    | P20 to P27   | H<br>(STBC) | General-purpose I/O ports In external bus mode, pins for which the corresponding bit in the HACR register is "0" function as the P20 to P27 pins.                                                                                      |  |

|                    |           | A16 to A23   |             | In external bus mode, pins for which the corresponding bit in the HACR register is "1" function as the upper address output pins (A16 to A23).                                                                                         |  |

| 7                  | 9         | P30          | H<br>(STBC) | General-purpose I/O port Functions as the ALE pin in external bus mode.                                                                                                                                                                |  |

|                    |           | ALE          |             | Functions as the address latch enable signal.                                                                                                                                                                                          |  |

| 8                  | 10        | P31          | H<br>(STBC) | General-purpose I/O port Functions as the RD pin in external bus mode.                                                                                                                                                                 |  |

|                    |           | RD           |             | Functions as the read strobe output (RD).                                                                                                                                                                                              |  |

| 10                 | 12        | P32          | H<br>(STBC) |                                                                                                                                                                                                                                        |  |

|                    |           | WRL          |             | Functions as the lower data write strobe output (WRL).                                                                                                                                                                                 |  |

| 11                 | 13        | P33          | H<br>(STBC) | General-purpose I/O port Functions as the WRH pin in 16-bit external bus mode if the WRE bit in the EPCR register is "1".                                                                                                              |  |

|                    |           | WRH          |             | Functions as the upper data write strobe output (WRH).                                                                                                                                                                                 |  |

STBC: Incorporates standby control

\*1: LQFP (FPT-100P-M05)

\*2: QFP (FPT-100P-M06)

| Pin no. |           | D.       | Circuit     | Franklan                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------|-----------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP*1  | QFP*2     | Pin name | type        | Function                                                                                                                                                                                                                                                                                                                                                                                                        |  |

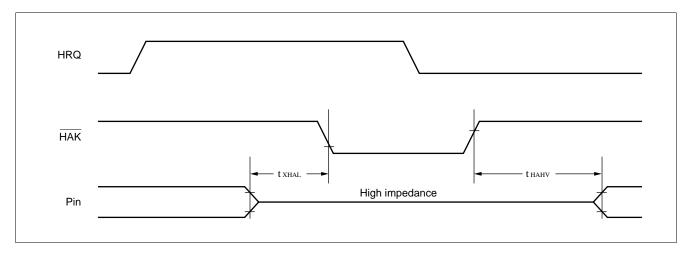

| 12      | 14        | P34      | H<br>(STBC) | General-purpose I/O port<br>Functions as the HRQ pin in external bus mode if the HDE bit<br>in the EPCR register is "1".                                                                                                                                                                                                                                                                                        |  |

|         |           | HRQ      |             | Functions as the hold request input pin (HRQ).                                                                                                                                                                                                                                                                                                                                                                  |  |

| 13      | 15        | P35      | H<br>(STBC) | General-purpose I/O port Functions as the HAK pin in external bus mode if the HDE bit in the EPCR register is "1".                                                                                                                                                                                                                                                                                              |  |

|         |           | HAK      |             | Functions as the hold acknowledge output (HAK) pin.                                                                                                                                                                                                                                                                                                                                                             |  |

| 14      | 16        | P36      | H<br>(STBC) | General-purpose I/O port Functions as the RDY pin in external bus mode if the RYE bit in the EPCR register is "1".                                                                                                                                                                                                                                                                                              |  |

|         |           | RDY      |             | Functions as the external ready input (RDY) pin.                                                                                                                                                                                                                                                                                                                                                                |  |

| 15      | 15 17 P37 |          | H<br>(STBC) | General-purpose I/O port<br>Functions as the CLK pin in external bus mode if the CKE bit in<br>the EPCR register is "1".                                                                                                                                                                                                                                                                                        |  |

|         |           | CLK      |             | Functions as the machine cycle clock output (CLK) pin.                                                                                                                                                                                                                                                                                                                                                          |  |

| 16      | 16 18 P4  |          | G<br>(STBC) | General-purpose I/O port When UART0 is operating, the data at the pin is used as the serial input (SIN0). Can be set as an open-drain output port (OD40 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D40 = "0": invalid at the input setting).                                                                                                         |  |

|         |           | SIN0     |             | Functions as the UART0 serial input (SIN0).                                                                                                                                                                                                                                                                                                                                                                     |  |

| 17      | 19        | P41      | F<br>(STBC) | General-purpose I/O port Functions as the SOT0 pin if the SOE bit in the UMC register is "1".  Can be set as an open-drain output port (OD41 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D41 = "0": invalid at the input setting).                                                                                                                    |  |

|         |           | SOT0     |             | Functions as the UART0 serial data output pin (SOT0).                                                                                                                                                                                                                                                                                                                                                           |  |

| 18      | 20        | P42      | G<br>(STBC) | General-purpose I/O port When UART0 is operating in external shift clock mode, the data at the pin is used as the clock input (SCK0). Also, functions as the SCK0 pin if the SOE bit in the UMC register is "1".  Can be set as an open-drain output port (OD42 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D42 = "0": invalid at the input setting). |  |

|         |           | SCK0     |             | Functions as the UART0 serial clock I/O pin (SCK0).                                                                                                                                                                                                                                                                                                                                                             |  |

STBC: Incorporates standby control

\*1: LQFP (FPT-100P-M05) \*2: QFP (FPT-100P-M06)

| Pin no.   |                                         | Din name Circuit | Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Function                                                                                                                                                                                                                                                                                                               |  |

|-----------|-----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP*1    | QFP*2                                   | Pin name         | type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                               |  |

| 19        | 21                                      | P43              | G<br>(STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | General-purpose I/O port When I/O expansion serial is operating, the data at the pin is used as the serial input (SIN1). Can be set as an open-drain output port (OD43 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D43 = "0": invalid at the input setting). |  |

|           |                                         | SIN1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functions as the serial input for I/O expansion serial data.                                                                                                                                                                                                                                                           |  |

| 20        | 22                                      | P44              | F<br>(STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | General-purpose I/O port Functions as the SOT1 pin if the SOE bit in the UMC register is "1". Can be set as an open-drain output port (OD44 = "1") by the open-drain control register (ODR4). The setting does not apply for ports set as inputs (D44 = "0": invalid at the input setting).                            |  |

|           |                                         | SOT1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functions as the output pin (SOT1) for I/O expansion serial data.                                                                                                                                                                                                                                                      |  |

| 22        | 24                                      | P45              | G (STBC)  When I/O expansion serial is operating in external shift mode, the data at the pin is used as the clock input (S Also, functions as the SCK1 pin if the SOE bit in the U register is "1".  Can be set as an open-drain output port (OD45 = "1") open-drain control register (ODR4). The setting does refor ports set as inputs (D45 = "0": invalid at the input setting does in the sett |                                                                                                                                                                                                                                                                                                                        |  |

|           |                                         | SCK1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functions as the I/O expansion serial clock I/O pin (SCK1).                                                                                                                                                                                                                                                            |  |

| 23        | 25                                      | P46              | F<br>(STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | General-purpose I/O port<br>Can be set as an open-drain output port (OD46 = "1") by the<br>open-drain control register (ODR4). The setting does not apply<br>for ports set as inputs (D46 = "0": invalid at the input setting).                                                                                        |  |

|           |                                         | ADTG             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functions as the external trigger input pin for the A/D converter.                                                                                                                                                                                                                                                     |  |

| 24        | 26                                      | P47              | F<br>(STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | General-purpose I/O port<br>Can be set as an open-drain output port (OD47 = "1") by the<br>open-drain control register (ODR4). The setting does not apply<br>for ports set as inputs (D47 = "0": invalid at the input setting).                                                                                        |  |

| 36 to 39, | 38 to 41,                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | General-purpose I/O ports                                                                                                                                                                                                                                                                                              |  |

| 41 to 44  | 41 to 44   43 to 46   AN0 to AN7   (STE |                  | (STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | The pins are used as analog inputs (AN0 to AN7) when the A/D converter is operating.                                                                                                                                                                                                                                   |  |

| 25        | 27                                      | P70              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | General-purpose I/O port                                                                                                                                                                                                                                                                                               |  |

|           |                                         | SIN3             | (STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Functions as the UART1 serial input (SIN3).                                                                                                                                                                                                                                                                            |  |

| 26        | 28                                      | P71              | H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | General-purpose I/O port                                                                                                                                                                                                                                                                                               |  |

|           |                                         | SOT3             | (STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Functions as the UART1 serial data output pin (SOT3).                                                                                                                                                                                                                                                                  |  |

| 27        | 29                                      | P72              | (0.775.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | General-purpose I/O port                                                                                                                                                                                                                                                                                               |  |

|           |                                         | SCK3             | (STBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Functions as the UART1 serial clock I/O pin (SCK0).                                                                                                                                                                                                                                                                    |  |

STBC: Incorporates standby control

<sup>\*1:</sup> LQFP (FPT-100P-M05)

<sup>\*2:</sup> QFP (FPT-100P-M06)

| Pin    | no.   |          | Circuit                                                                                                                                                                                                                                                                                      |                                                                                                            |  |

|--------|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| LQFP*1 | QFP*2 | Pin name | type                                                                                                                                                                                                                                                                                         | Function                                                                                                   |  |

| 30     | 32    | P73      | L (STBC) General-purpose I/O port Functions as a D/A output pin when DAE0 = "1" in the D/A control register (DACR).                                                                                                                                                                          |                                                                                                            |  |

|        |       | DAO0     |                                                                                                                                                                                                                                                                                              | Functions as D/A output 0 when the D/A converter is operating.                                             |  |

| 31     | 33    | P74      | L<br>(STBC)                                                                                                                                                                                                                                                                                  | General-purpose I/O port Functions as a D/A output pin when DAE1 = "1" in the D/A control register (DACR). |  |

|        |       | DAO1     |                                                                                                                                                                                                                                                                                              | Functions as D/A output 1 when the D/A converter is operating.                                             |  |

| 45     | 47    | P80      |                                                                                                                                                                                                                                                                                              | General-purpose I/O port                                                                                   |  |

|        |       | IRQ0     | _ !                                                                                                                                                                                                                                                                                          | Functions as external interrupt request I/O 0.                                                             |  |

| 46     | 48    | P81      | I                                                                                                                                                                                                                                                                                            | General-purpose I/O port                                                                                   |  |

|        |       | IRQ1     |                                                                                                                                                                                                                                                                                              | Functions as external interrupt request I/O 1.                                                             |  |

| 51     | 53    | P82      | I                                                                                                                                                                                                                                                                                            | General-purpose I/O port                                                                                   |  |

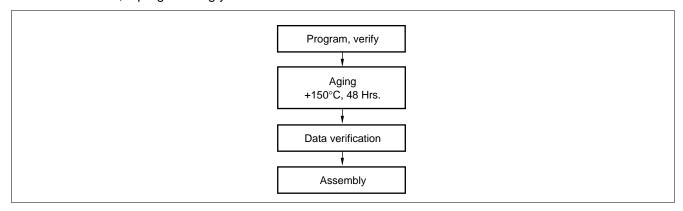

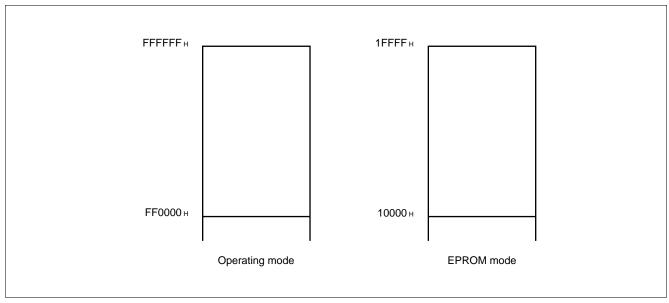

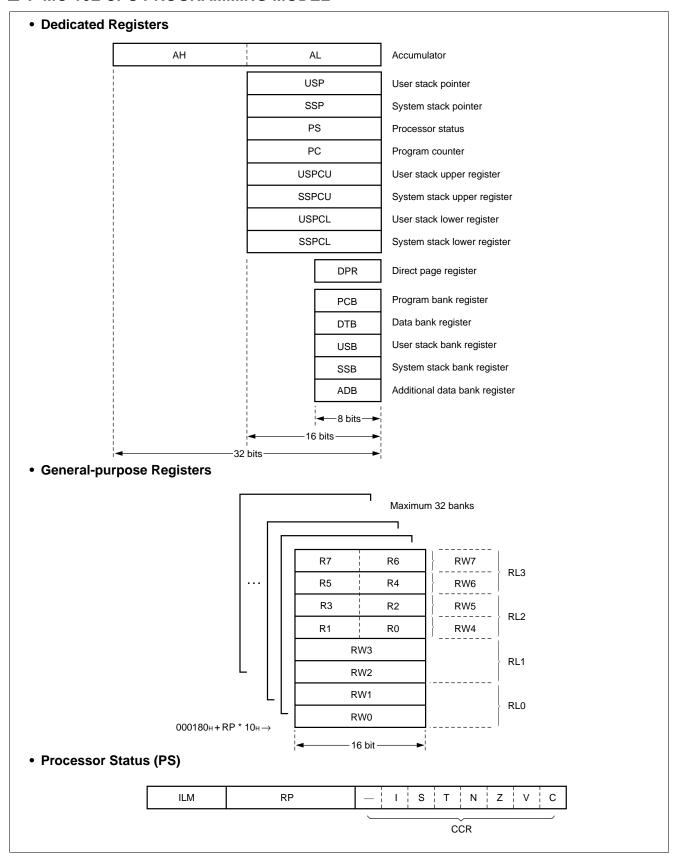

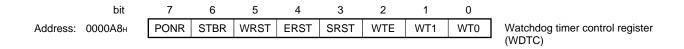

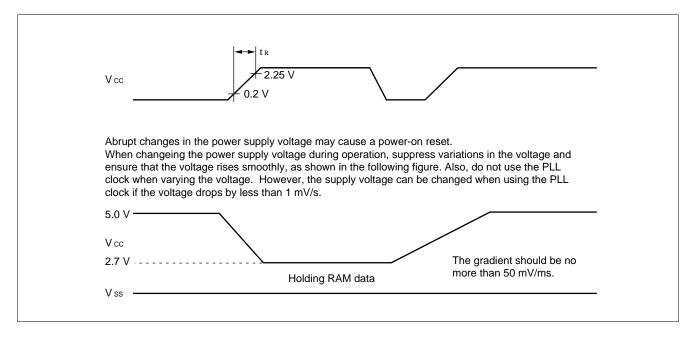

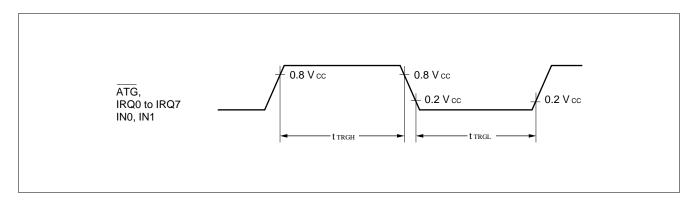

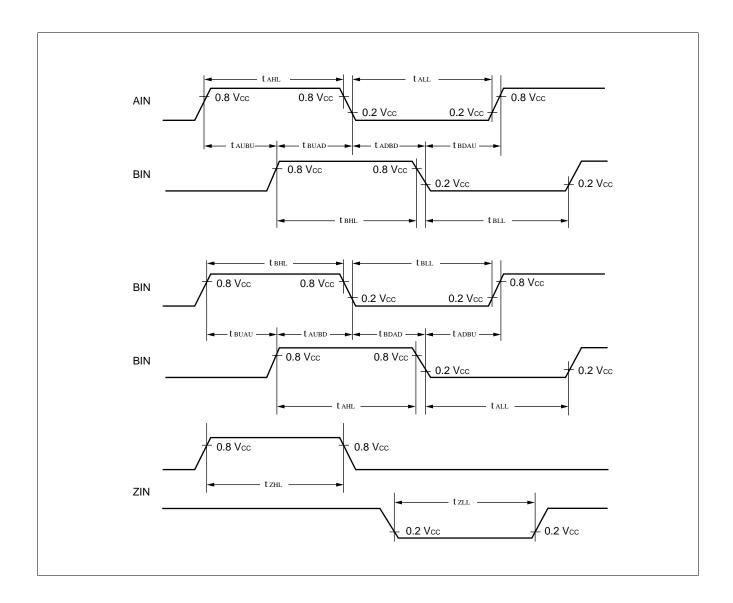

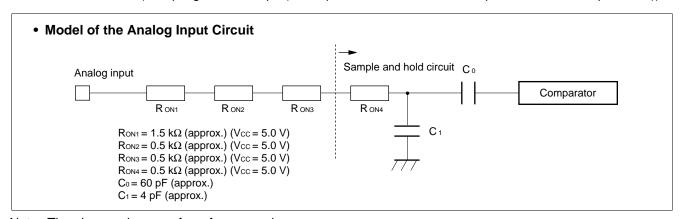

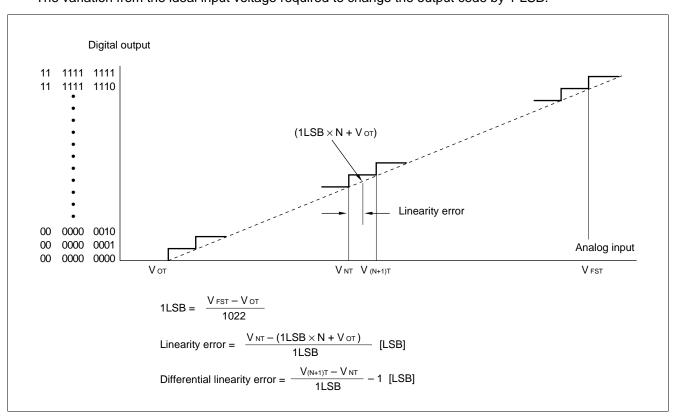

|        |       | IRQ2     |                                                                                                                                                                                                                                                                                              | Functions as external interrupt request I/O 2.                                                             |  |