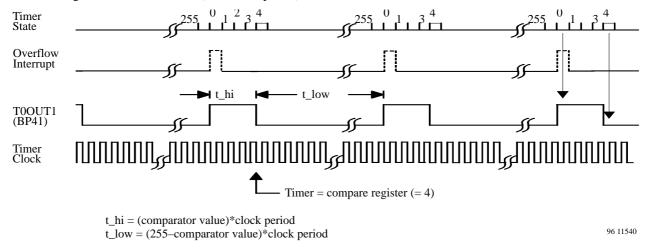

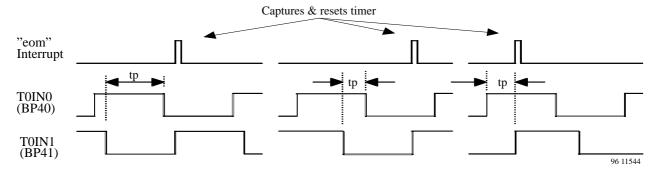

# M44C510 Keyboard Application

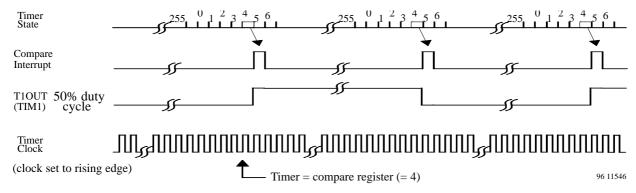

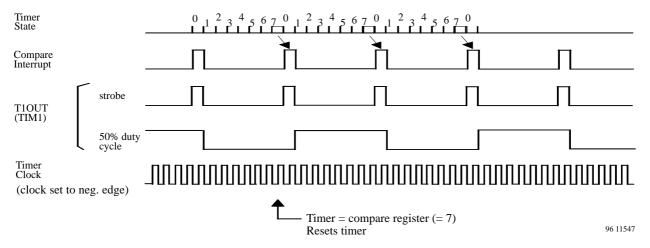

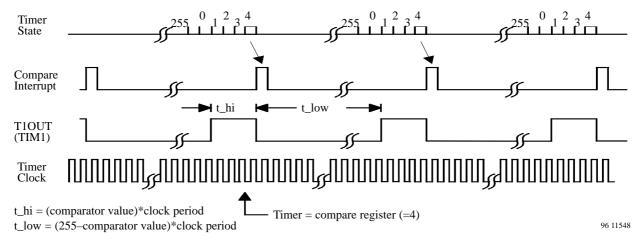

# **Table of Contents**

| IntroductionIntroduction                                            | 1  |

|---------------------------------------------------------------------|----|

| TEMIC Semiconductors                                                | 1  |

| TEMIC – a Microcontroller Specialist                                | 1  |

| The History of MARC4                                                | 1  |

| The MARC4 Family                                                    | 1  |

| Members of the MARC4 Family                                         | 3  |

| M43C505 – Low-Current 3- and 5-V Solution for Consumer Applications | 3  |

| M44C090/092 – Low-Current Solution for Wireless Communication       | 4  |

| M44C260 – Perfect Solution for Security and Access Control          | 5  |

| M44C510 – Flexible and Powerful Solution for Embedded Control       | 6  |

| M44C588 – Versatile High-End Controller for General Purposes        | 7  |

| M44C636 – Perfect Solution for Low-Current Applications             | 8  |

| Key Application Chart                                               | 9  |

| M44C510 Keyboard Application                                        | 10 |

| Keyboard Scanning and Code Generation                               |    |

| Program Description for Keypad Handling and Code Generation         | 11 |

| Make/Break/Typematic Timing Control                                 | 12 |

| Communication between PC and Keyboard                               | 14 |

| Command Protocol                                                    | 14 |

| Appendix                                                            | 17 |

| MARC4 Product Overview                                              |    |

| Development Tools                                                   | 18 |

| *                                                                   |    |

| Data Sheet M44C510                                                  |    |

## Introduction

### **TEMIC Semiconductors**

TEMIC is the microelectronics enterprise of Daimler-Benz. TEMIC's Semiconductor division is a leading manufacturer of application-specific, value-adding integrated circuits for communication equipment, automotive and industrial systems, computers and broadcast media. Discrete semiconductors and optoelectronic devices make the product range complete.

With a technology portfolio which includes bipolar, BiCMOS, GaAs, CMOS and DMOS processes, TEMIC Semiconductors provides a unique set of components and solutions.

# TEMIC – a Microcontroller Specialist

TEMIC is since twenty years a technology leader in applications requiring minimum current consumption such as watches and clocks, and has ten years of experience regarding the design of low-power microcontrollers. TEMIC offers 4-bit, 8-bit, extended 8-bit and 32-bit controllers. Our MARC4 products are high-sophisticated and well-experienced as they have been adapted to ten different technologies up to now.

Choosing TEMIC as a partner means, you will have one independent source for components – transistors, diodes, optoelectronic devices including LEDs and IrDA components, integrated circuits and smart-power devices. Due to our state-of-the-art facilities worldwide, TEMIC's production resources are more than sufficient. TEMIC guarantees excellent application support which will reduce your time-to-market. The available software library for programming as well as the detailed documentation (see appendix) are free of charge.

# The History of MARC4

TEMIC Semiconductors started developing the MARC4 in 1986, based on experience with the former 4-µm CMOS core e3101. The aim was to design an easy-to-use, high-performance, 4-bit controller by selecting a high-level language for programming and to provide highly advanced and efficient development tools. Special effort was spent to realize a modular concept with a very small core design.

After developing MARC4 products in 3-µm and even 1.5-µm technologies, TEMIC started working with external foundries in 1989. Since 1993, the MARC4 family has been based completely on external foundries using 2-µm down to 0.6-µm technologies (volatile/non-volatile).

# The MARC4 Family

TEMIC offers a complete family of cost-effective, single-chip CMOS microcontrollers, based on a 4-bit CPU core designed for 1.5-, 3- and 5-V applications. The modular MARC4 architecture is HARVARD-like, high-level language oriented and best designed to realize high-integrated microcontrollers with a variety of application- or customer-specific, on-chip peripheral combinations. The MARC4 controller's low voltage and low power consumption is perfect for hand-held and battery-operated applications.

The standard members of the MARC4 family have selected peripheral combinations for a broad range of applications.

Programming is supported by an easy-to-use, PC-based software development system with a high-level language qFORTH compiler and an emulator board. The stack-oriented microcontroller concept enables the qFORTH compiler to generate compact and efficient MARC4 program codes.

#### **Applications**

The very small 4-bit core combined with a versatile peripheral cell library enables the design of application-specific microcontrollers.

- 32-kHz sub-clock

- A/D converter

- Comparator

- EEPROM

- External interrupts

- High-current ports

- LCD drivers

- Low battery detection

- Power-on-reset

- Prescaler

- Programmable I/Os

- Reset input

- Serial I/O

- Timers/counters

- Various system oscillators

- Watchdog timer

#### **Features**

- Very small 4-bit core combined with versatile peripheral cell library

- Various on-chip peripheral combinations available

- HARVARD structure 3 parallel-operating buses (pipelining) enhance computing power (2 clock cycles per instruction only)

- 72 RISC-like 8-bit instructions

- Stack architecture offers customized stack size and 'unlimited' subroutine nesting

- Unique 8 level interrupt controller leads to a very short (3 cycle) interrupt response time

- 'Brown-out' function and internal Power-On-Reset (POR) make external components unnecessary

- Small 4-bit periphery bus offers extraordinary flexibility

- 256 × 4-bit of RAM directly addressable

- Up to 9 KBytes of ROM

- Low-voltage operating range

- Low power consumption

- Hardware optimized to fit with high-level language qFORTH

- Programming and debugging is supported by an integrated software development system

Programming in the high-level language qFORTH is simple, easy to understand and advantageous. From the hardware side, the expression and return stack have a user-programmable size, the qFORTH instructions correspond directly to the machine words and therefore, the program executes fast. The software code is compact and the sub-routine nesting is nearly unlimited. In addition, programming is easy and safe due to the possibility of combining existing software modules.

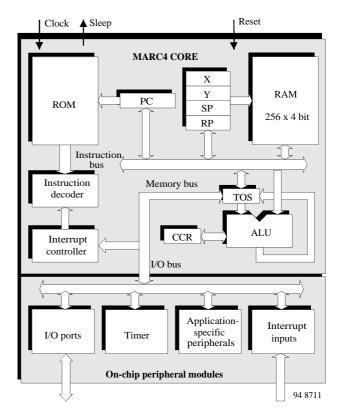

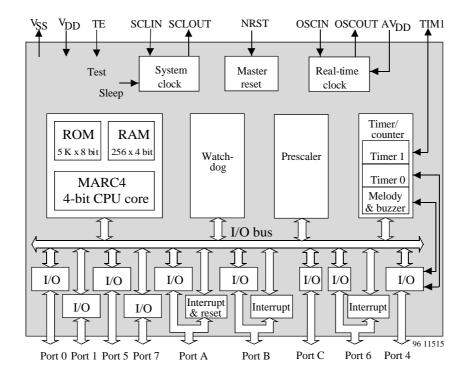

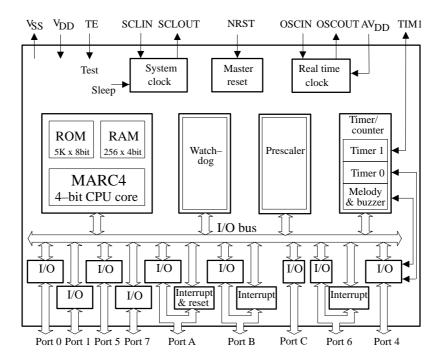

MARC4 core

# **Members of the MARC4 Family**

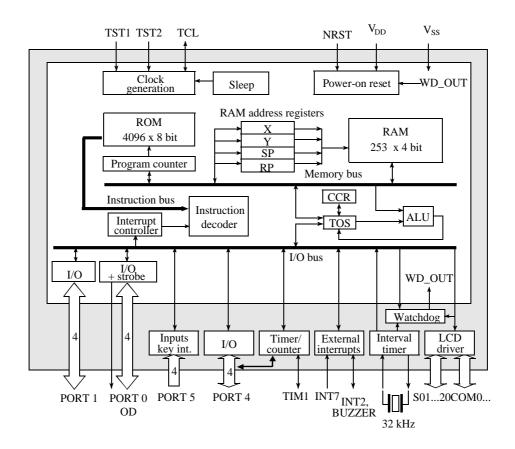

# M43C505 – Low-Current 3- and 5-V Solution for Consumer Applications

- Wide supply voltage range (2.4 V to 5.5 V)

- Very low current consumption

- $4096 \times 8 \text{ ROM}, 253 \times 4 \text{ RAM}$

- 16 programmable I/Os

- 2-MHz fast system clock (1 MIPS)

- 32-kHz crystal oscillator

- 20 × 4 LCD temp.-compensated drivers

- 2 external/ 3 internal interrupt sources

- Prescaler/ interval timer

- Internal POR and brown-out

Existing applications comprise temperature measurement and -control, battery charging, bicycle computers, timers, radio-controlled clocks and CD players.

Existing software modules for time keeping, calendar, stop watches, display drivers for various multiplex rates, accurate dual-slope temperature measurement and interface software for TEMIC's radio-controlled clock receivers are part of the comprehensive qFORTH software library.

A power-saving sleep- and stop mode increases significantly battery life time in hand-held applications while offering 1 MIPS computing power during active time. Internal POR, oscillator and pull-up/-down resistors simplify PCB layout and minimize system costs.

Software is free of charge for these applications which increases the confidence level and reduces the time-to-market for new developments.

M43C505

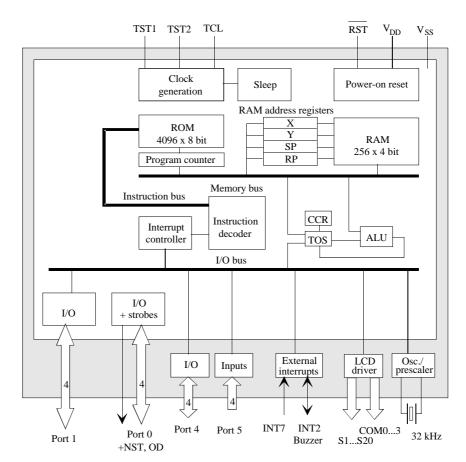

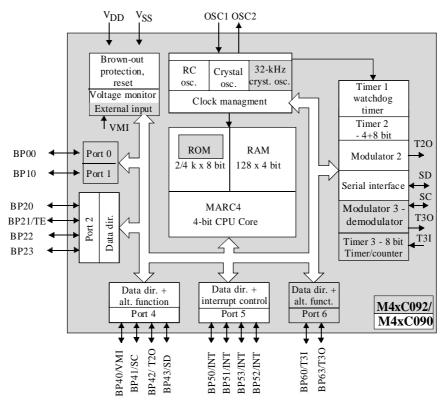

## M44C090/092 – Low-Current Solution for Wireless Communication

- 4 mask-selectable system-clock sources, crystal oscillator, external clock, RC oscillator with/ without external resistor

- Wide supply voltage range (1.8 V to 6.2 V)

- Very low sleep current

- 2/4 + 0.5 KByte ROM,  $128 \times 4$  bit RAM

- 512-bit EEPROM optional

- 12/20 programmable I/Os

- 32-kHz crystal oscillator (C092 only)

- Up to 5 external/ 6 internal interrupt sources

- Prescaler/ interval timer

- 2-wire serial interface

- Multi-functional timers/ counters incl. IR/ RF remote control carrier generation

- Watchdog, POR and brown-out function

- OTP M48C092

- SO8 package (M44C090)

The two MARC4 products M44C090 and M44C092 offer highest integration for IR and

RF data communication and remote control. These controllers are optimized for the requirements of the transmitter as well as the receiver side.

TEMIC's system know-how was used to integrate the modulator into the M44C090 and the modulator as well as the demodulator for commonly-used wireless protocols into the M44C092.

Both controllers perfectly match the RF front end device U2740B and the IR driver chip U426B. This – along with the very small SSO package and the approach to minimize the number of external components – leads to extremely compact remote control units, e.g., for electronic keys. Finally, the very low current consumption and the extended supply voltage range optimizes battery life time.

Development is supported with the OTP M48C092 which covers the features of the M44C092 and both includes the performance of the M44C090.

M44C090/092

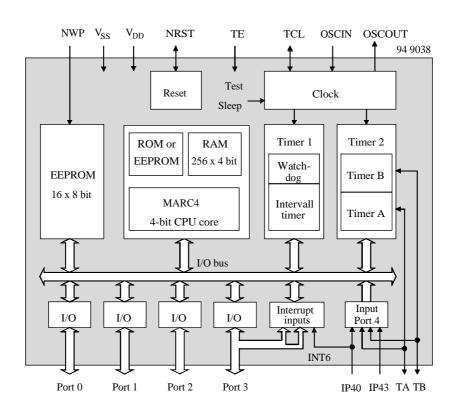

# M44C260 – Perfect Solution for Security and Access Control

- Wide supply voltage range (2.4 V to 6.2 V)

- Very low sleep current

- 4 KByte ROM,  $256 \times 4$  bit RAM

- 128 bit EEPROM on board

- 18 programmable I/Os

- 4.2-MHz fast system clock (FLL)

- 32-kHz crystal oscillator

- 6 interrupt sources

- Prescaler/ interval timer

- Multi-functional timers/ counters incl. IR remote control carrier generation

- Watchdog and POR

- OTP M48C260

The M44C260 is specially optimized for IR remote control and security and access control applications, e.g., for automotive and industrial applications.

The on-board 128-bit EEPROM offers the capability to store and change identifiers as well as security codes. Any application which requires the ability to store a small amount of data will also benefit.

The multi-function timer/counter modules which are also on-board include modes to directly generate the signal for an IR transmitter device such as TEMIC's U426B.

The wide supply voltage range combined with the very small current consumption increases battery life time in mobile applications.

The OTP M48C260 simplifies and reduces the development time.

For detailed information please refer to TEMIC's "Automotive Safety and Convenience Data Book".

M44C260

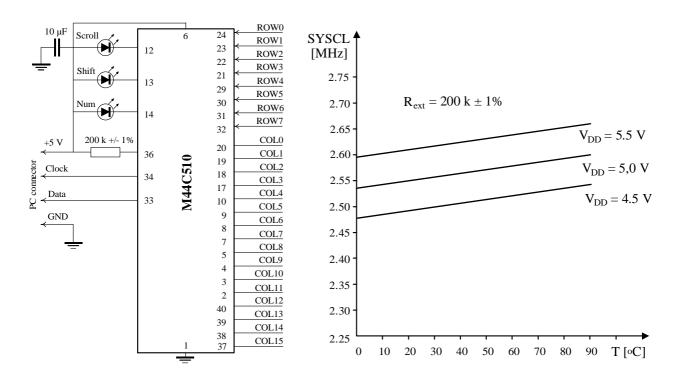

# M44C510 – Flexible and Powerful Solution for Embedded Control

- 4 mask-selectable system-clock sources, crystal oscillator, ceramic resonator, RC oscillator with/ without external resistor

- Wide supply voltage range (2.4 V to 6.2 V)

- Very low current consumption

- 4 KByte ROM,  $256 \times 4$  bit RAM

- 32 bitwise-programmable I/Os

- High-current outputs

- 32-kHz crystal oscillator

- 10 external and 4 internal interrupt sources

- Prescaler/ interval timer

- Two 8-bit multi-functional timers/ counters

- Watchdog timer, internal POR and brown-out

- Minimum external components

- Very small package (SSO44)

The M44C510 presents a solution for embedded control applications. Various mask

options provide an optimum price-performance ratio for the system.

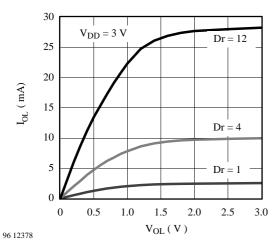

Due to the pull-up/-down, push-pull and opendrain functions of the bit-wise programmable I/Os, external components become unneccessary. LEDs and relays can directly be connected to the M44C510 by using up to eight I/Os driving 20 mA each. Mask selectable clock sources cover a wide range of application requirements. Watchdog, POR and brown-out function supervise correct operation. More than ten timer/counter modes offer D/A conversion, event counting, 16-bit modes and even melody modes. The wide supply voltage range along with the very small current consumption supports battery-powered systems.

Software modules available include keyboard software, LCD and LED display driver, serial port protocols, radio-controlled clock decoders and timer as well as temperature measurement modules.

M44C510

# M44C588 – Versatile High-End Controller for General Purposes

- Various mask-selectable system clock sources to define application-specific system price/ performance ratio

- Dual clock mode for minimum current consumption

- Wide supply voltage range (1.8 to 6.2 V)

- 9 KByte ROM, 512 × 4 bit RAM

- Up to 32 I/Os incl. high-current ports

- 32-kHz crystal oscillator

- Up to  $32 \times 4$  LCD segments

- Prescaler

- 8 external and 5 internal interrupts

- Watchdog, POR and low battery detection for enhanced system security

- Synchronous 8-bit serial port

- Multi-function timer/ counter incl. IR/ RF remote control carrier generation

High-end, battery-powered consumer applications such as bicycle computers, feature watches, diver computers and high-end, radio-controlled clocks/watches which all require both computing power and low current consumption will benefit from the M44C588.

The dual clock mode and core frequencies of 4 MHz (2 MIPS) on the one hand and 32 kHz slow operation/ sleep mode (consuming only micro-amps) on the other hand make the M44C588 the best solution for these tough requirements.

The programmable I/Os with pull-up/-down options, integrated oscillators, 20-mA drive capability, internal watchdog, POR and low battery detection minimize the number of system components, resulting in reduced system costs and PCB size. The integrated temperature-compensated display drivers for up to 128 LCD segments enable even sophisticated display solutions. Data transfer to external storage devices such as serial EEPROMs is simplified by the serial port.

M44C588

# M44C636 – Perfect Solution for Low-Current Applications

- 1.2 V to 2.2 V/ 1.8 V to 3.6 V (mask opt.)

- < 1 μA sleep mode current, 200 μA active current

- On-chip RC system clock oscillator

- 4 KByte ROM,  $253 \times 4$  bit RAM

- 16 programmable I/Os

- 32-kHz crystal oscillator

- 20 × 4 temperature-compensated LCD driver segments

- Prescaler/ interval timer

- Two independent 8-bit timers/ counters

- Watchdog and POR

The M44C636 is pushing the limits of lowcurrent consumption to the values of the dis charge of batteries. Combining sleep and active periods, system currents of less than 2  $\mu$ A can be designed. The M44C636 therefore fits exactly to applications such as feature watches, radio-controlled clocks/watches, timers powered by back-up capacitors and even telecom applications such as telephone-rate counters directly powered by transmission lines.

Mask options adjust the extended supply voltage range of the M44C636 to 1.5-V or 3-V batteries. For 3-V applications, an internal voltage regulator powers the core, reducing the active current down to  $200~\mu A$ .

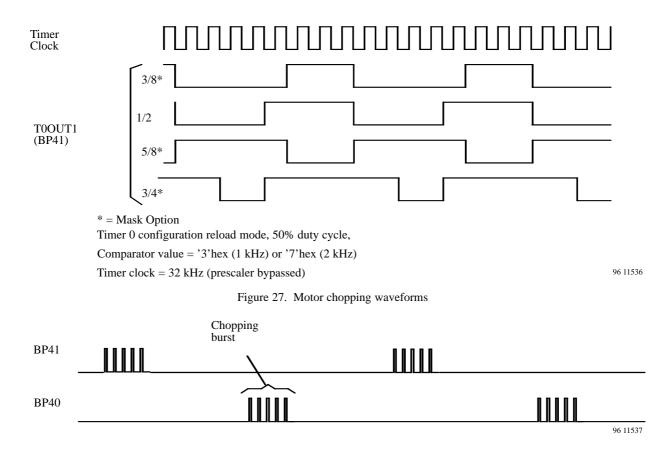

Two multi-function timers/counters and motor output drivers support 3-V watch applications even including motor-pulse chopping. Internal watchdog, brown-out function and POR supervise correct operation.

M44C636

# **Key Application Chart**

| MARC4 Product | <b>Key Applications</b>                                                        |

|---------------|--------------------------------------------------------------------------------|

| M43C505       | Temperature measurement Altitude and distance meter Battery charger/ shaver    |

| M44C090/092   | Remote control                                                                 |

| M44C260       | Access control/ security                                                       |

| M44C510       | White goods, industrial control RC clocks/ feature watches Keyboard controller |

| M44C588       | Bicycle computer, diver computer high-end RC clocks/ watches                   |

| M44C636       | Telecom applications Timer/ blind control RC clocks/ feature watches           |

# M44C510 Keyboard Application

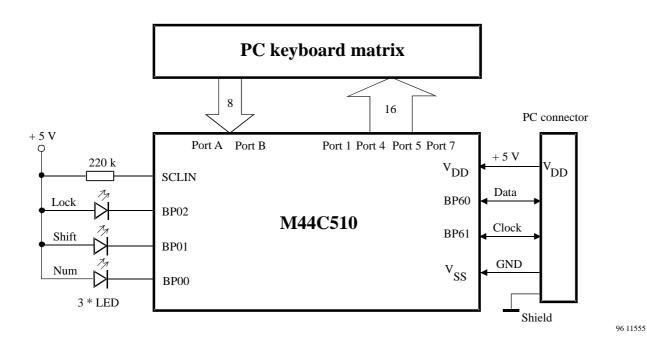

Figure 1. M44C510-P40 as keyboard controller

# **Keyboard Scanning and Code Generation**

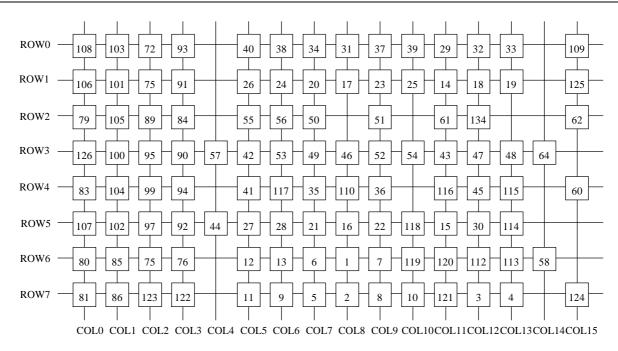

A key matrix is scanned every 4 milliseconds. Scanning is performed by sequentially pulling each of the 16 column outputs in turn to a low level while the other column outputs remain high. For each column, the eight row inputs are monitored for activated keys.

Each key is defined by a matrix number, a row and a column number (see figure 2). The current software handles up to eight simultaneously activated keys. If more than eight keypads are pressed, the others are ignored.

The M44C510 hardware supports up to 12 simultaneously-activated keys.

Each key has an associated Make/ Break code which is transmitted serially to the host PC. This code signals the activation or release of that particular key. The codes consist of single or multiple byte sequences. There are three different scan code sets (XT, AT, PS2) which can all be supported by the TEMIC microcontroller. The release/activation of a key is only accepted by the controller after the matrix inputs have remained stable for two consecutive scan cycles (anti-bounce guard period).

All keys operate in a Typematic mode. When a key is pressed and held, the keyboard repeatedly transmits the corresponding Make code after a defined delay (Typematic Delay) with a pre-defined repetition rate (Typematic Rate).

Figure 2. Keyboard matrix

# **Program Description for Keypad Handling and Code Generation**

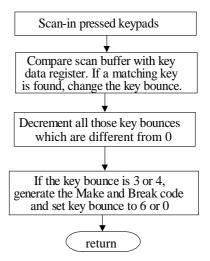

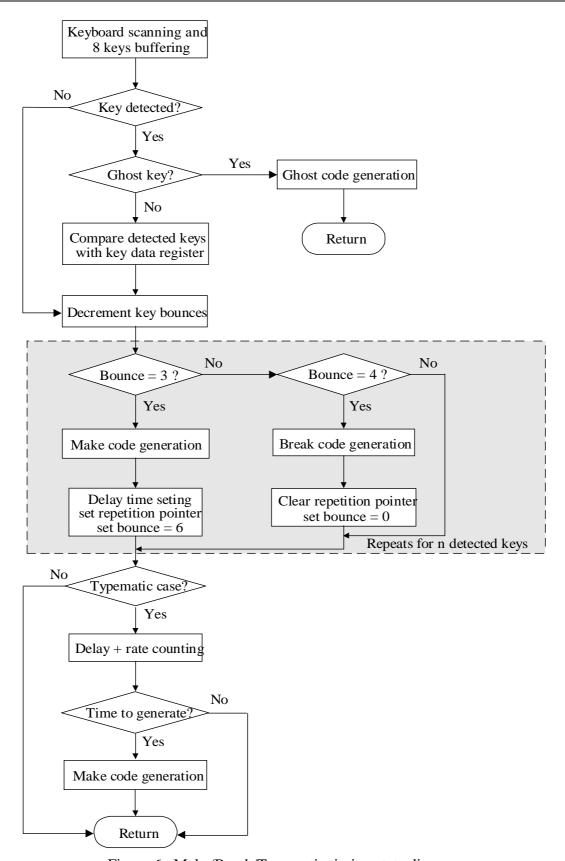

The controller keeps track of the incoming keys using eight working register pairs. There is one pair for each of the 8 keys that can be activated at any time. Each pair consists of an 8-bit key data register for storing the key matrix row/column address, and a 4-bit key bounce register which stores the present key status and controls the anti-bounce protection. For a detailed description, see figures 3 and 4.

During every scan cycle, the controller monitors the keypad matrix inputs and stores the row and column addresses of all pressed keys in a temporary scan buffer. At the end of the cycle, the monitored addresses are compared with the key addresses of active keys in the 8 key data registers. Those addresses which can not be found, (i.e., newly activated keys) are stored in an empty key data register, and the corresponding bounce state is set to 2. The associated bounce state of all matching key addresses (already activated keys) are updated to either 4 or 7 depending on whether the key was detected for the first time in the preceding

scan cycle or whether it has been activated for a longer time. Finally, after this comparison phase, all bounce values are decremented and the next scan cycle is resumed.

If the resultant decremented bounce state is 3, the Make code for that key is generated and stored. If, on the other hand, the bounce state decrements to 4, the corresponding Break code is similarly generated. Thus, a newly activated/released key will generate a Make/Break code after two scan cycles.

Figure 3. Bounce handling

Figure 4. Make/Break Code generation

# Make/Break/Typematic Timing Control

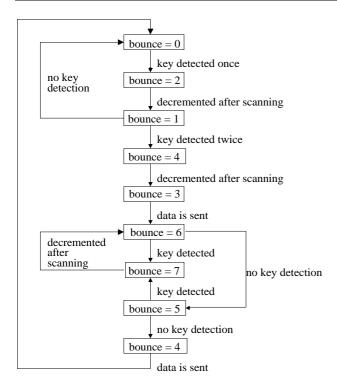

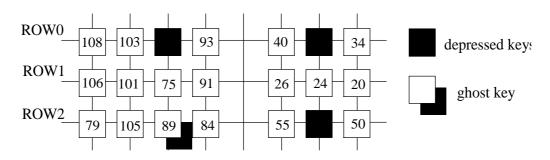

After every complete matrix scan, the controller checks detected key arrangements for so-called ghost keys. Due to the arrangement of single contact keys in the standard key matrixes, activating three keys on two orthogonal axis causes an indirect connection between two row lines. This might cause a controller to detect a further, fourth, non-activated ghost key. If this were the case, the controller would see four pressed keys instead of

three, as shown in figure 5. A situation as described above can be detected by the M44C510 and a ghost key code is then generated.

Case keys (Shift, Alt, Ctrl or Num Lock) also have their own Make/Break codes. Normal keys, when activated together with one or more Case keys, cause modified Make/Break codes. To handle such multi-key combinations, the controller always stores and updates the present status (active/non active) of each Case key. These are updated whenever a case key Make/Break occurs. Only certain keys can be used together with a case key and only the codes for these keys are modified in the case of a simultaneous Case key activation.

All Make/Break codes are stored in an output FIFO keyboard buffer.

After loading a new key code into the FIFO, the key address is stored in a Typematic pointer register and the Typematic Delay value is loaded into a Typematic counter. This then proceeds to count down unless disabled by a Break code. When time out occurs, the counter reloads with the Typematic Rate period and sets the last code, addressed by the Typematic pointer, again into the FIFO. This is repeated until the key is released and the key bounce state 4 is reached (see figure 4), whereby the Typematic Pointer is reset, the Break code put into the FIFO and the bounce state set to 0 (i.e., empty key data).

A reset of the Typematic pointer disables the Typematic counter and thus the key repeat function.

Figure 5. Generation of a ghost key

Figure 6. Make/Break/Typematic timing state diagram

# **Communication between PC and Keyboard**

The following subsection describes the interfacing of the microcontroller to the PC.

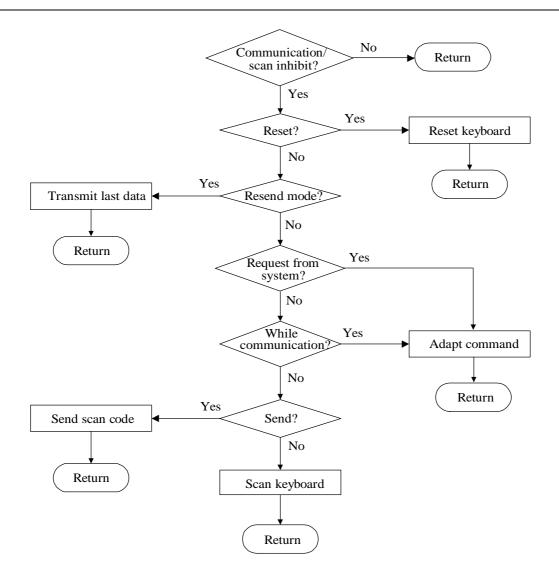

After power-up, the microcontroller sets the clock and data lines to a high level and checks the current line status.

There are three line status modes possible:

- PC forces clock line low (communication interrupted/inhibited by PC)

- PC forces data line low (request to send data from PC to keyboard)

- Data and clock line high (scan code transmission by keyboard)

The clock line is always driven by the microcontroller, except when the PC inhibits communication. If the clock line is high, the controller checks the data line. When it is low (forced by the PC), the PC signals a request to send serial data to the keyboard. In this case, the controller supplies a serial clock burst to fetch the data packet from the PC.

When data and clock lines are high, the serial channel is free for the controller to transmit the scanned key codes to the PC.

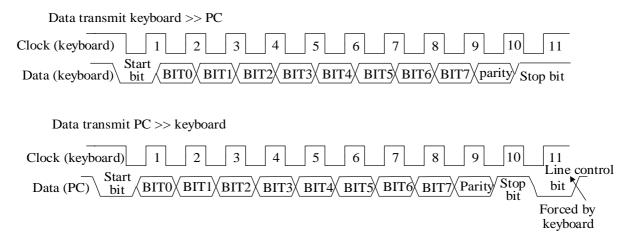

Each serial data packet normally consists of an 11-bit data stream, including a start bit, 8 data bits, a parity bit and stop bit (see figure 7).

In transmit mode, the data sent by the controller to the PC is valid during the low level of the clock signal. Data changes during the high clock phase. The data transfer can be interrupted by the PC at any time up until the rising edge of the 10th clock pulse (parity bit).

In receive mode, the received PC data is valid during the high level of the clock signal and changes during the low level. After detecting the stop bit, the controller forces the data line to a low level for a one-bit period (line control bit).

The start bit is always low and the stop bit high.

### **Command Protocol**

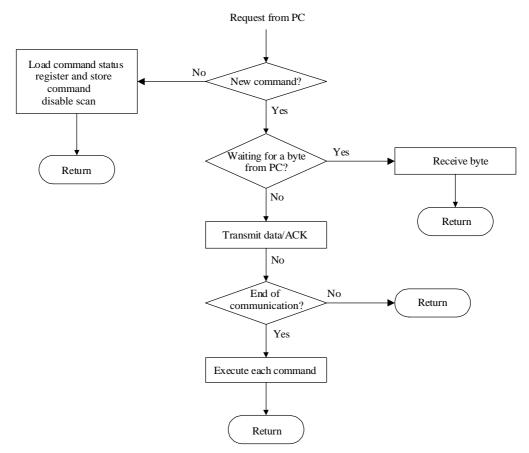

The controller must handle different types of data – both commands and data to and from the PC, acknowledge signaling and key scan codes from the keyboard FIFO buffer. All commands and data are organized in serial packets as described above. Commands coming from the PC always have priority and a new command always overrides a preceding one. To initiate a command, the PC forces the data line low and the M44C510 supplies eleven clock pulses and reads in the command.

Figure 7. Data communication format

Some of these PC commands request either data from the keyboard, or prepare the keyboard to receive the following data words. After receiving a command, the controller returns an acknowledge word (FA hex). If the command involves data transmission from/to the PC, the acknowledge is followed by the transmission of the data. The M44C510 sends only the key scan codes from the FIFO buffer when there is no request from the PC.

Whenever there is a request from the PC, the controller reads in the data (see figure 8). The data is checked to see whether it is a new command. A new command is stored in a Command Register. The command is decoded and the number of associated data bytes to be handled is stored in a Command Status register. The acknowledge word (FA hex) is stored in the command output buffer and transmitted, whereupon the Command Status register dec-

rements and tests for zero. If it is zero, this command communication is terminated and the controller is free to process other commands or return to key scanning (see figure 9). If it is not zero, the controller remains active to process further command-associated data. While the controller is involved with command communication, all keyboard scanning is suspended.

The multiple scan codes are stored into a 16-byte First-In-First-Out (FIFO) buffer until the PC is ready to receive them. If the FIFO is full and further scan codes appear, an overrun code is generated and stored into the 17th byte of the last occupied buffer register location. All further key activities will be ignored. The keyboard buffer contains only the scan codes and does not include any commands from the PC or optional data during command communication.

Figure 8. Command communication state diagram

Figure 9. Communication state diagram

# **Appendix**

# **MARC4 Product Overview**

|                        | M43C505                               | M44C090        | M44C092           | M44C260       | M44C510           | M44C588            | M44C636                              |

|------------------------|---------------------------------------|----------------|-------------------|---------------|-------------------|--------------------|--------------------------------------|

| ROM×8                  | 4096                                  | 2048           | 4096              | 4096          | 4096              | 9216               | 4096                                 |

| Test ROM × 8           | -                                     | 512            | 512               | 1024          | 1024              | 1024               | -                                    |

| RAM×4                  | 253                                   | 128            | 128               | 256           | 256               | 256+256            | 253                                  |

| EEPROM × 8             | _                                     | (64)           | (64)              | 16            | _                 | _                  | _                                    |

| IN/OUT (bidirectional) | 12 + 1                                | 12             | 20                | 16            | 32                | 16 + 16            | 12 + 1                               |

| IN                     | 4                                     | -              | -                 | 2             | -                 | _                  | 4                                    |

| Prescaler              | 2                                     | 1              | 1                 | 1             | 2                 | 2                  | 2                                    |

| 8-bit timer            | _                                     | 1              | 2                 | 2             | 2                 | 2                  | 2                                    |

| Watchdog               | _                                     | yes            | yes               | yes           | yes               | yes                | yes                                  |

| Batt. low              | _                                     | yes            | yes               | _             | _                 | yes                | _                                    |

| High I out             | _                                     | -              | _                 | _             | 8 × 20 mA         | 4 ×4 mA @<br>2.4 V | $2 \times 1 \text{ mA}$              |

| Serial I/O             | _                                     | 8 bit sync.    | 8 bit sync.       | _             | _                 | 8 bit sync.        | _                                    |

| LCD                    | $20 \times 4$                         | _              | _                 | _             | _                 | $32 \times 4$      | $20 \times 4$                        |

| Analog I/O             | _                                     | _              | 1 comparator      | _             | _                 | _                  | _                                    |

| Interrupts             | 2 int., 3 ext.                        | 3 int., 4 ext. | 6 int., 5 ext.    | 3 int., 3 ext | 4 int., 10 ext.   | 5 int., 8 ext.     | 4 int., 3 ext.                       |

| Peripheral<br>clock    | 32 kHz                                | -              | 32 kHz            | 32 kHz        | 32 kHz            | 32 kHz             | 32 kHz                               |

| System clock           | ystem clock 2 MHz (RC) 4 MHz (Q,(R)C) |                | 4 MHz<br>(Q,(R)C) | 4.2 MHz       | 4 MHz<br>(Q,(R)C) | 4 MHz<br>(Q,(R)C)  | 1 MHz<br>(1.5 V)<br>500 kHz<br>(3 V) |

| Inst. cycle            | 1 μs                                  | 0.5 μs         | 0.5 μs            | 1 μs          | 0.5 μs            | 0.5 μs             | 4 μs                                 |

| IDD active             | ·                                     |                | 1 mA              | 4 mA          | 1 mA              | 1.4 mA             | 400 μA<br>(1.5 V)<br>180 μA          |

| I sleep (3 V)          | 3 μΑ                                  | 10 μΑ          | 1 μΑ              | 0,8 μΑ        | 3 μΑ              | 4 μΑ               | (3 V)<br>0.8 μA                      |

| Suppl. voltage         | 2.4 - 5.5 V                           | 1.8 - 6.2 V    | 1.8 - 6.2 V       | 2.4 - 6.2 V   | 2.4 - 6.2 V       | 2.4 - 6.2 V        | 1.2 - 2.2 V                          |

| Suppli voluge          | 2 0.0                                 | 1.0 0.2        | 110 0.2           | 2 0.2 .       | 2 0.2             | 2 0.2              | 1.8 V-3.6 V                          |

| Package                | DIT                                   | DIT            | DIT               | DIT           | DIT               | DIT                | DIT                                  |

|                        | QFP64                                 | SO8<br>SO16    | SO28<br>DIP28     | SO28<br>SSO20 | PDIL24,40         | QFP100             | QFP64                                |

|                        | PLCC44                                |                |                   |               | SO28<br>SSO44     |                    | PLCC44                               |

| Eval. type             | M45C535                               | M48C092        | M48C092           | M48C260       | M40C510           |                    | M40C636                              |

|                        | (metal-<br>ROM)                       | (EEPROM)       | (EEPROM)          | (EEPROM)      | (Piggyback)       |                    | (Piggyback)                          |

# **Development Tools**

## **Integrated Software Package SDS2**

- Free-of-charge qFORTH software library

- Integrated environment with text editor and pull-down menus running on any IBM-compatible PC under MS-DOS, Windows, OS/2

- Software simulator

- Highly optimizing qFORTH compiler

- Comprehensive documentation (qFORTH, Programmer's Guide, User's Guide)

#### **Emulator Card**

- Full-sized PC/AT plug-in card

- $4 \text{ k} \times 32 \text{ bit instruction trace buffer}$

- Up to 4 PC, 4 RAM and 2 I/O breakpoints for real-time triggering

- Stack overflow and interrupt supervisor

### **Target Application Board**

- Level shifter logic for real-time emulation even < 1.2 V

- VG96 interface connector to an additional wire-wrap board or LCD demo board

- Interface connector to emulator card

- Stand-alone operation possible from a single, external 9-V supply

- Standard 27C64 CMOS EPROM socket on board for stand-alone mode

# M40C505/636 Piggyback

- 64-pin DIL-sized hybrid chip, compatible to the emulation device's pin out

- Supply voltage 2.8 V to 5.5 V

- All external components are integrated

- Standard 27C64 on top side

## M44C510 Piggyback

• 40-pin DIL-sized hybrid chip

### M48C260 OTP with Programming Adapter

- Available in SS028 or PDIL28 package

- Programmer attached to parallel/ printer port

# MARC4 – 4-bit Universal Microcontroller

The M44C510 is a member of the TEMIC family of 4-bit single-chip microcontrollers. It contains ROM, RAM, up to 32 digital I/O pins, up to 10 maskable external interrupt sources, 6 maskable internal interrupts, a watchdog timer, 32-kHz oscillator with programmable watch timer, 2 x 8-bit multifunction timer/counter module and a versatile on-chip system clock generation module.

#### **Features**

- 4 K x 8-bit application ROM

- 256 x 4-bit RAM

- 8 hardware and software interrupt priority levels

- Bitwise maskable prioritized interrupts

- Up to 10 external and 4 internal interrupts

- Up to 32 I/O lines

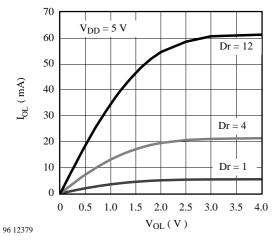

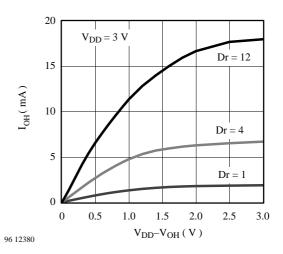

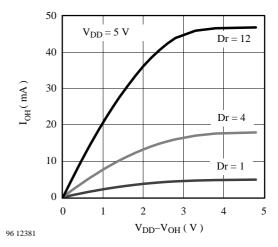

- High drive ports (20 mA,  $V_{DD} = 5 \text{ V}$ )

- I/O ports bitwise configurable with combined interrupt handling (for serial I/O applications)

- 2 x 8-bit multifunction timer/counters

- 32-kHz on chip oscillator with programmable prescaler/interval timer

- User definable on-chip system clock generation

- 4-MHz crystal, 4-MHz ceramic resonator or fully integrated RC oscillator \*\*

#### **Benefits**

- Extremely low-power consumption

- Minimal external components

- Coded reset and watchdog timer \*\*

- Power-on reset, "brown out" function

- Power-down mode

- 2.4 V to 6.2 V supply voltage

- Data retention down to 2 V in SLEEP mode

- Efficient, hardware-controlled interrupt handling

- High-level programming language in qFORTH

- Comprehensive library of useful routines

- PC based development tools

(\*\* mask option)

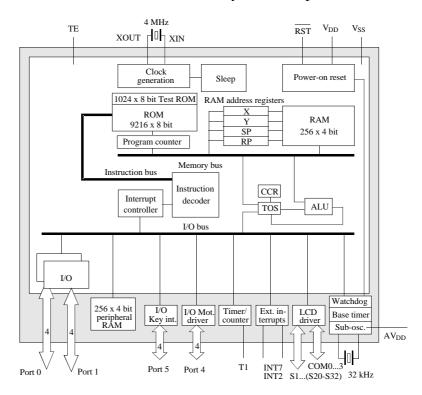

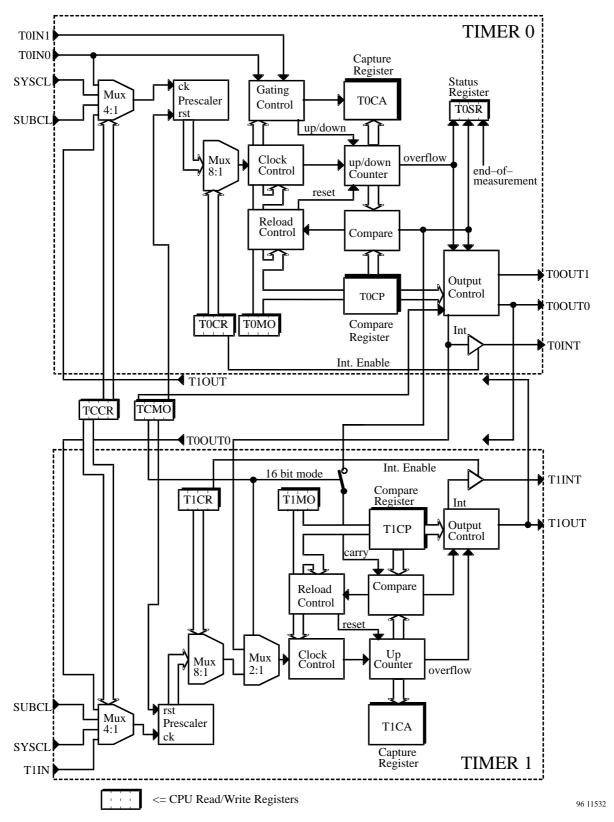

Figure 1. Block diagram

Rev. A2, 24-Jun-96

96 11515

96 11516

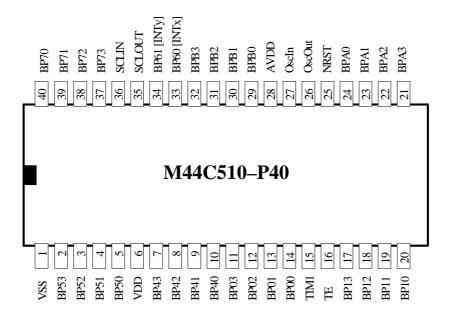

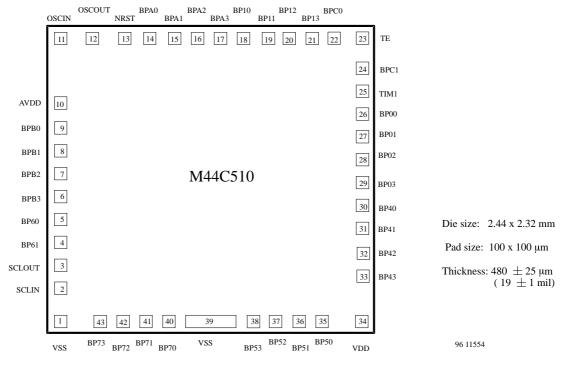

Figure 2. Pin connections

Table 1. Pin description

| Name            | Function                                                                                                                                       |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{ m DD}$     | Power supply voltage +2.4 V to +6.2 V                                                                                                          |

| $AV_{ m DD}$    | Analog power supply voltage +2.4 V to +6.2V                                                                                                    |

| V <sub>SS</sub> | Circuit ground                                                                                                                                 |

| BP00 - BP03     | 4 bidirectional I/O lines of Port 0 – automatic nibblewise configurable I/O                                                                    |

| BP10 – BP13     | 4 bidirectional I/O lines of Port 1(*) – automatic nibblewise configurable I/O                                                                 |

| BP50 – BP53     | 4 bidirectional I/O lines of high current Port 5(*) – bitwise configurable I/O                                                                 |

| BP70 – BP73     | 4 bidirectional I/O lines of high current Port 7(*) – bitwise configurable I/O                                                                 |

| BPA0 – BPA3     | 4 bidirectional I/O lines of Port A(*) – bitwise configurable I/O and as inputs to a port monitor module. Optional coded reset inputs (*)      |

| BPB0 – BPB3     | 4 bidirectional I/O lines of Port B(*) – bitwise configurable I/O and as inputs to a port monitor module                                       |

| BPC0 – BPC1     | 2 bidirectional I/O lines of Port C (*) – bitwise configurable I/O                                                                             |

| BP60 – BP61     | 2 bidirectional I/O lines of Port 6 (*) – bitwise configurable I/O or as 2 external programmable interrupts                                    |

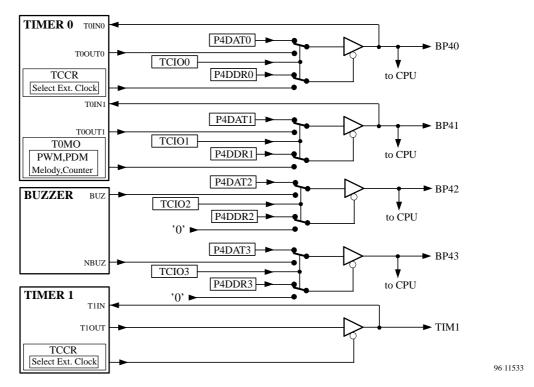

| BP40-T0OUT0     | I/O line BP40 of Port 4(*) – configurable I/O or timer/counter 0 I/O T0OUT0                                                                    |

| BP41-T0OUT1     | I/O line BP41 of Port 4(*) – configurable I/O or timer/counter 0 I/O T0OUT1                                                                    |

| BP42-BUZ        | High current I/O line BP42 of Port 4(*) – configurable I/O or buzzer output BUZ                                                                |

| BP43-NBUZ       | High current I/O line BP43 of Port 4(*) – configurable I/O or buzzer output NBUZ                                                               |

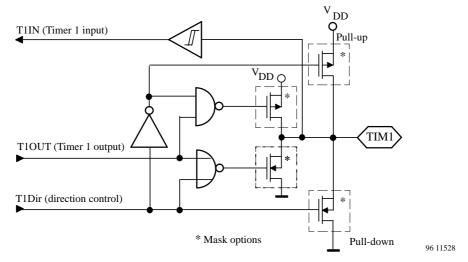

| TIM1            | Dedicated bidirectional I/O for Timer 1                                                                                                        |

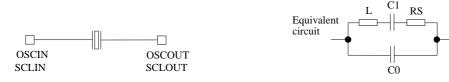

| SCLIN           | 4-MHz quartz crystal/ceramic resonator or trimming resistor pin (mask-option dependent)                                                        |

| SCLOUT          | 4-MHz quartz crystal/ceramic resonator pin (mask-option dependent)                                                                             |

| OSCIN           | 32-kHz quartz crystal pin (mask-option dependent)                                                                                              |

| OSCOUT          | 32-kHz quartz crystal pin (mask-option dependent)                                                                                              |

| TE              | Testmode input. This input is used to control the test modes (internal pull-down)                                                              |

| NRST            | Reset input (/output), a logic low on this pin resets the device. An internal watchdog or coded reset is indicated by a low pulse on this pin. |

<sup>(\*)</sup> For mask options, please see the order information.

### **Contents**

| 1 | MAR   | C4 Archit           | tecture                                                                 |  |  |  |  |  |  |

|---|-------|---------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

|   | 1.1   | General             | Description                                                             |  |  |  |  |  |  |

|   | 1.2   | Compor              | nents of MARC4 Core                                                     |  |  |  |  |  |  |

|   |       | 1.2.1               | ROM                                                                     |  |  |  |  |  |  |

|   |       | 1.2.2               | RAM                                                                     |  |  |  |  |  |  |

|   |       | 1.2.3               | Registers                                                               |  |  |  |  |  |  |

|   |       | 1.2.4               | ALU                                                                     |  |  |  |  |  |  |

|   |       | 1.2.5               | Instruction Set                                                         |  |  |  |  |  |  |

|   |       | 1.2.6               | I/O Bus                                                                 |  |  |  |  |  |  |

|   | 1.3   | Interrup            | ot Structure                                                            |  |  |  |  |  |  |

|   |       | 1.3.1               | Hardware Interrupts                                                     |  |  |  |  |  |  |

|   |       | 1.3.2               | Software Interrupts                                                     |  |  |  |  |  |  |

|   | 1.4   | Hardwa              | re Reset                                                                |  |  |  |  |  |  |

|   | 1.5   | Clock G             | Generation                                                              |  |  |  |  |  |  |

|   |       | 1.5.1               | Clock Monitor Mode                                                      |  |  |  |  |  |  |

|   | 1.6   | Sleep M             | Iode                                                                    |  |  |  |  |  |  |

|   | Perip | _                   | lules                                                                   |  |  |  |  |  |  |

|   | 2.1   | Address             | sing Peripherals                                                        |  |  |  |  |  |  |

|   | 2.2   | Bidirectional Ports |                                                                         |  |  |  |  |  |  |

|   |       | 2.2.1               | Port 0, Port 1 – Bidirectional Ports Type 1                             |  |  |  |  |  |  |

|   |       | 2.2.2               | Port 5, Port 7, Port C – Bidirectional Ports Type 2                     |  |  |  |  |  |  |

|   |       | 2.2.3               | Port A, Port B – Bidirectional Ports Type 3 – and Port Monitor Function |  |  |  |  |  |  |

|   |       | 2.2.4               | Port 6 – Bidirectional Port Type 4                                      |  |  |  |  |  |  |

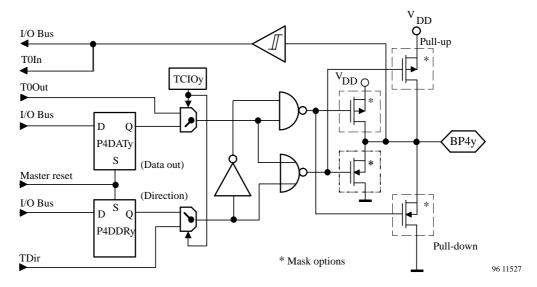

|   |       | 2.2.5               | Port 4 – Bidirectional Port Type 5                                      |  |  |  |  |  |  |

|   |       | 2.2.6               | TIM1 – Bidirectional Pin Timer 1                                        |  |  |  |  |  |  |

|   | 2.3   | Interval            | Timers / Prescaler                                                      |  |  |  |  |  |  |

|   |       | 2.3.1               | Interval Timer Registers                                                |  |  |  |  |  |  |

|   | 2.4   | Watchdo             | og Timer                                                                |  |  |  |  |  |  |

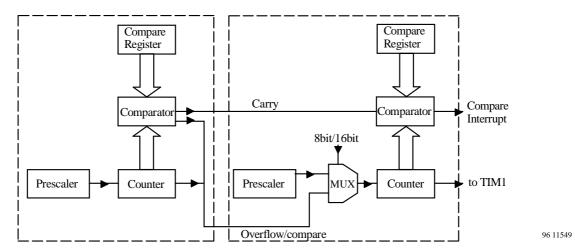

|   | 2.5   |                     | Counter Module (TCM)                                                    |  |  |  |  |  |  |

|   |       | 2.5.1               | General Timer/Counter Control Registers                                 |  |  |  |  |  |  |

|   |       | 2.5.2               | Timer/Counter in 16-bit Mode                                            |  |  |  |  |  |  |

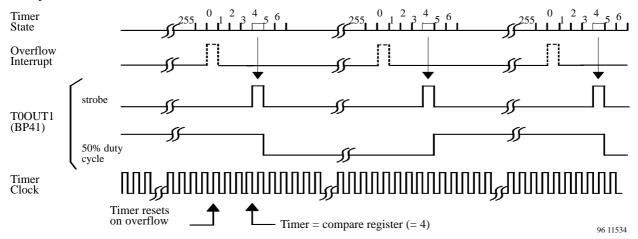

|   |       | 2.5.3               | Timer 0 Modes                                                           |  |  |  |  |  |  |

|   |       | 2.5.4               | Timer 1 Modes                                                           |  |  |  |  |  |  |

|   | 2.6   |                     | Module                                                                  |  |  |  |  |  |  |

|   | 2.7   |                     | on                                                                      |  |  |  |  |  |  |

|   | Elect |                     | acteristics                                                             |  |  |  |  |  |  |

|   | 3.1   |                     | e Maximum Ratings                                                       |  |  |  |  |  |  |

|   | 3.2   |                     | erating Characteristics                                                 |  |  |  |  |  |  |

|   | 3.3   |                     | uracteristics                                                           |  |  |  |  |  |  |

|   |       |                     |                                                                         |  |  |  |  |  |  |

|   |       | •                   | amples                                                                  |  |  |  |  |  |  |

|   |       | ring Infor          |                                                                         |  |  |  |  |  |  |

### 1 MARC4 Architecture

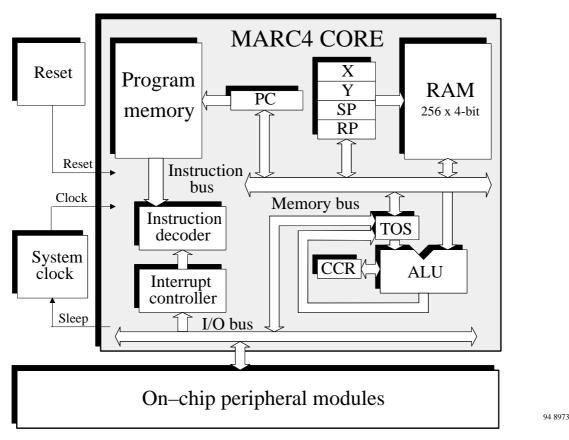

Figure 3. MARC4 core

## 1.1 General Description

The MARC4 microcontroller consists of an advanced stack based 4-bit CPU core and on-chip peripherals. The CPU is based on the HARVARD architecture with physically separate program memory (ROM) and data memory (RAM). Three independent buses, the instruction bus, the memory bus and the I/O bus are used for parallel communication between ROM, RAM and peripherals. This enhances program execution speed by allowing both instruction prefetching, and a simultaneous communication to the on-chip peripheral circuitry. The extremely powerful integrated interrupt controller with associated eight prioritized interrupt levels supports fast and efficient processing of hardware events. The MARC4 is designed for the high-level programming language qFORTH. The core includes an expression and a return stack. This architecture allows high-level language programming without any loss in efficiency or code density.

# 1.2 Components of MARC4 Core

The core contains ROM, RAM, ALU, a program counter, RAM address registers, an instruction decoder and an interrupt controller. The following sections describe each functional block in more detail:

#### 1.2.1 **ROM**

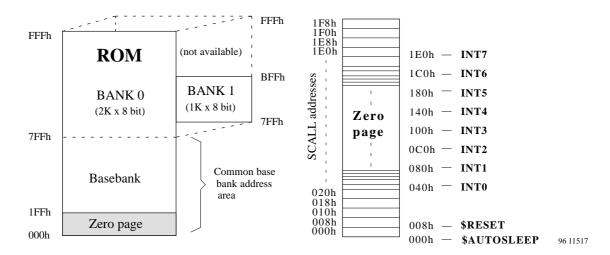

The program memory (ROM) is mask programmed with the customer application program during the fabrication of the microcontroller. The ROM is addressed by a 12-bit wide program counter, thus predefining a maximum program bank size of 4 Kbytes. An additional 1 Kbyte of ROM exists which is used partly for a quality control self-test program. The remaining space is available for the application program. The access to this additional ROM section is done by using a ROM-bank switch.

Figure 4. ROM map of M44C510

The lowest user ROM address segment is taken up by a 512-byte zero page which contains predefined start addresses for interrupt service routines and special subroutines accessible with single-byte instructions (SCALL). The corresponding memory map is shown in figure 4. Look-up tables of constants can also be held in ROM and are accessed via the MARC4's built-in TABLE instruction.

#### **ROM Banking**

Bank switching is fully supported by the compiler for customers programming with qFORTH. The MARC4 switches from one ROM bank to another by writing the new bank number to the ROM Bank Register (RBR). Conventional program space (power-up bank) resides in ROM bank 0. Each ROM bank consists of a 4-KByte address space whereby the lowest 2 KByte is common to all banks, so that addresses between 000h and 7FFh always accesses the same ROM data (see figure 4). When ROM banking is used, the compiler will, if necessary, insert the program code to save and restore the condition of the RBR on bank switching.

#### 1.2.2 RAM

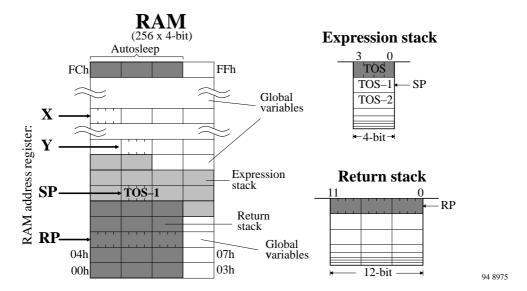

The MARC4 contains 256 x 4-bit wide static random access memory (RAM). It is used for the expression stack, the return stack and data memory for variables and arrays. The RAM is addressed by any of the four 8-bit wide RAM address registers SP, RP, X and Y.

#### **Expression Stack**

The 4-bit wide expression stack is addressed with the expression stack pointer (SP). All arithmetic, I/O and memory reference operations take their operands from, and return their result to the expression stack. The

MARC4 performs the operations with the top of stack items (TOS and TOS-1). The TOS register contains the top element of the expression stack and works in the same way as an accumulator. This stack is also used for passing parameters between subroutines and as a scratch pad area for temporary storage of data.

#### **Return Stack**

The 12-bit wide return stack is addressed by the return stack pointer (RP). It is used for storing return addresses of subroutines, interrupt routines and for keeping loop index counts. The return stack can also be used as a temporary storage area.

The MARC4 instruction set supports the exchange of data between the top elements of the expression stack and the return stack. The two stacks within the RAM have a userdefinable location and maximum depth.

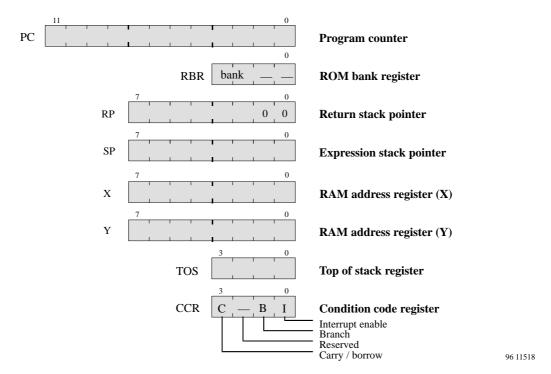

#### 1.2.3 Registers

The MARC4 controller has seven programmable registers and one condition code register. They are shown in figure 6.

#### **Program Counter (PC)**

The program counter (PC) is a 12-bit register that contains the address of the next instruction to be fetched from the ROM. Instructions currently being executed are decoded in the instruction decoder to determine the internal micro operations. For linear code (no calls or branches) the program counter is incremented with every instruction cycle. If a branch, call, return instruction or an interrupt is executed, the program counter is loaded with a new address. The program counter is also used with the TABLE instruction to fetch 8-bit wide ROM constants.

Figure 5. RAM map

#### **ROM Banking Register (RBR)**

The ROM banking register is a 4-bit register whereby in the M44C510, only bit 2 is used. This indicates which ROM bank is presently being addressed. The RBR is accessed with a standard qFORTH peripheral read or write instruction (IN or OUT, port address 'D' hex).

#### **RAM Address Registers**

The RAM is addressed with the four 8-bit wide RAM address registers: SP, RP, X and Y. These registers allow access to any of the 256 RAM nibbles.

#### **Expression Stack Pointer (SP)**

The stack pointer (SP) contains the address of the next-totop 4-bit item (TOS-1) of the expression stack. The pointer is automatically preincremented if a nibble is moved onto the stack, or postdecremented if a nibble is removed from the stack. Every postdecrement operation moves the item (TOS-1) to the TOS register before the SP is decremented. After a reset the stack pointer has to be initialized with ">SP SO" to allocate the start address of the expression stack area.

#### Return Stack Pointer (RP)

The return stack pointer points to the top element of the 12-bit wide return stack. The pointer automatically preincrements if an element is moved onto the stack or it postdecrements if an element is removed from the stack. The return stack pointer increments and decrements in steps of 4. This means that every time a 12-bit element is stacked, a 4-bit RAM location is left unwritten. These locations are used by the qFORTH compiler to allocate

4-bit variables. After a reset, the return stack pointer has to be initialized with ">RP FCh".

#### RAM Address Register ( X and Y )

The X and Y registers are used to address any 4-bit item in the RAM. A fetch operation moves the addressed nibble onto the TOS. A store operation moves the TOS to the addressed RAM location. By using either the preincrement or postdecrement, addressing mode arrays in the RAM can be compared, filled or moved.

#### Top Of Stack (TOS)

The top of stack register is the accumulator of the MARC4. All arithmetic/logic, memory reference and I/O operations use this register. The TOS register receives data from the ALU, ROM, RAM or I/O bus.

#### Condition Code Register ( CCR )

The 4-bit wide condition code register contains the branch, the carry and the interrupt-enable flag. These bits indicate the current state of the CPU. The CCR flags are set or reset by ALU operations. The instructions SET\_BCF, TOG\_BF, CCR! and DI allow direct manipulation of the condition code register.

#### Carry/Borrow (C)

The carry/borrow flag indicates that borrow or carry out of arithmetic logic unit ( ALU ) occurred during the last arithmetic operation. During shift and rotate operations, this bit is used as a fifth bit. Boolean operations have no affect on the C flag.

#### Branch (B)

The branch flag controls the conditional program branching. Should the branch flag have been set by a previous

instruction, a conditional branch will cause a jump. This flag is affected by arithmetical, logical, shift, and rotate operations.

#### Interrupt Enable ( I )

The interrupt-enable flag globally enables or disables the triggering of all interrupt routines with the exception of

the non-maskable reset. After a reset, or on executing the DI instruction, the interrupt-enable flag is reset, thus disabling all interrupts. The core will not accept any further interrupt requests until the interrupt-enable flag has been set again either by executing an EI, RTI or SLEEP instruction.

Figure 6. Programming model

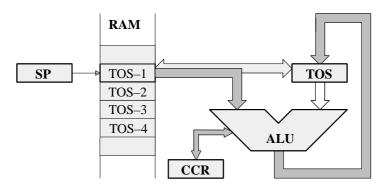

#### 1.2.4 ALU

Figure 7. ALU zero-address operations

The 4-bit ALU performs all the arithmetical, logical, shift and rotate operations with the top two elements of the expression stack (TOS and TOS-1) and returns the result to the TOS. The ALU operations affect the carry/borrow and branch flag in the condition code register (CCR).

#### 1.2.5 Instruction Set

The MARC4 instruction set is optimized for the highlevel programming language qFORTH. Many MARC4 instructions are qFORTH words. This enables the compiler to generate a fast and compact program code. The CPU has an instruction pipeline which allows the controller to prefetch an instruction from ROM at the same time as the present instruction is being executed. The MARC4 is a zero-address machine. The instructions contain only the operation to be performed and no source or destination address fields. The operations are implicitly performed on the data placed on the stack. There are one and two byte instructions which are executed within 1 to 4 machine cycles. A MARC4 machine cycle is made up of two system clock (SYSCL) cycles. Most of the instructions are only one byte long and are executed in a single machine cycle.

#### 1.2.6 I/O Bus

The I/O ports and the registers of the peripheral modules (Timer 0, Timer 1, Interval timer, Watchdog etc.) are I/O

mapped. All communication between the core and the onchip peripherals takes place via the I/O bus and the associated I/O control. With the MARC4 IN and OUT instructions, the I/O bus enables a direct read or write access to one of the 16 primary I/O addresses. More about the I/O access to the on-chip peripherals is described in the "Peripheral Modules". The I/O bus is internal and is not accessible by the customer on the final microcontroller device, but is used as the interface for the MARC4 emulation (see also the section "Emulation").

94 8977

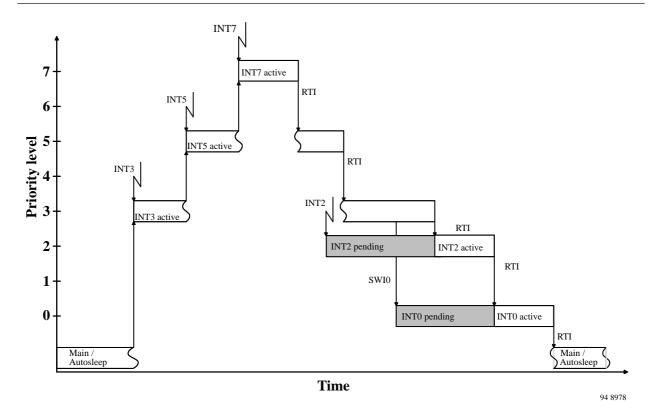

## 1.3 Interrupt Structure

The MARC4 can handle interrupts with eight different priority levels. They can be generated from the internal and external interrupt sources or by a software interrupt from the CPU itself. Each interrupt level has a hard-wired priority and an associated vector for the service routine in the ROM (see table 2, page 10). The programmer can postpone the processing of interrupts by resetting the interrupt enable flag (I) in the CCR. An interrupt occurrence will still be registered but the interrupt routine is only started after the I flag is set. All interrupts can be masked, and the priority individually software configured by programming the appropriate control register of the interrupting module (see section "Peripheral Modules").

Figure 8. Interrupt handling

#### **Interrupt Processing**

For processing the eight interrupt levels, the MARC4 includes an interrupt controller with two 8-bit wide "interrupt pending" and "interrupt active" registers. The interrupt controller samples all interrupt requests during every non-I/O instruction cycle and latches these in the interrupt pending register. Whenever an interrupt request is detected, the CPU interrupts the program currently being execution, on condition that no higher priority interrupt is present in the interrupt active register. If the interrupt-enable bit is set, the processor enters an interrupt acknowledge cycle. During this cycle a short call (SCALL) instruction is executed to the service routine and the current PC is saved on the return stack. An interrupt service routine is finished with the RTI instruction. This instruction sets the interrupt-enable flag, resets the corresponding bits in the interrupt pending/active register and fetches the return address from the return stack to the program counter. When the interrupt-enable flag is reset (triggering of interrupt routines is disabled), the

execution of new interrupt service routines is inhibited, but not the logging of the interrupt requests in the interrupt pending register. The execution of the interrupt is be delayed until the interrupt-enable flag is set again. Note that interrupts are only lost if an interrupt request occurs while the corresponding bit in the pending register is still set (i.e., the interrupt service routine is not yet finished).

It should also be realized that automatic stacking of the RBR is not carried out by the hardware and so if ROM banking is used, the RBR must be stacked on the expression stack by the application program and restored before the RTI. After a master reset (power-on, external or watchdog reset), the interrupt-enable flag and the interrupt pending and interrupt active registers are all reset.

#### **Interrupt Latency**

The interrupt latency is the time from the occurrence of the interrupt to the interrupt service routine being activated. In the MARC4, this is extremely short and takes between 3 to 5 machine cycles depending on the state of the core.

Table 2. Interrupt priority table

| Interrupt | Priority     | ROM Address | Maskable | Interrupt Opcode |

|-----------|--------------|-------------|----------|------------------|

| INT0      | lowest       | 040h        | Yes      | C8h (SCALL 040h) |

| INT1      |              | 080h        | Yes      | D0h (SCALL 080h) |

| INT2      |              | 0C0h        | Yes      | D8h (SCALL 0C0h) |

| INT3      |              | 100h        | Yes      | E8h (SCALL 100h) |

| INT4      |              | 140h        | Yes      | E8h (SCALL 140h) |

| INT5      |              | 180h        | Yes      | F0h (SCALL 180h) |

| INT6      | $\downarrow$ | 1C0h        | Yes      | F8h (SCALL 1C0h) |

| INT7      | highest      | 1E0h        | Yes      | FCh (SCALL 1E0h) |

#### 1.3.1 Hardware Interrupts

Table 3. Hardware interrupts

| Interrupt           | I | Possi | ible l | Inter | rupt | Prio | rities | S | RST | Interrupt M | ask | Function              |

|---------------------|---|-------|--------|-------|------|------|--------|---|-----|-------------|-----|-----------------------|

| Source              | 0 | 1     | 2      | 3     | 4    | 5    | 6      | 7 |     | Register    | Bit |                       |

| NRST external       |   |       |        |       |      |      |        |   | X   | _           | ı   | low level active      |

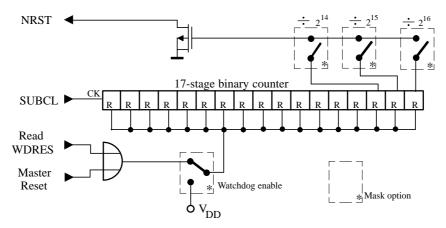

| Watchdog            |   |       |        |       |      |      |        |   | #   | _           | ı   | 1/2 - 2 sec. time out |

| Port A coded reset  |   |       |        |       |      |      |        |   | #   | _           | ı   | level any inputs      |

| Port A monitor      |   | *     |        | *     |      | *    |        | * |     | PAIPR       | 3   | any edge, any input   |

| Port B monitor      |   | *     |        | *     |      | *    |        | * |     | PBIPR       | 3   | any edge, any input   |

| Port 60 external    |   | *     |        | *     |      | *    |        | * |     | P6CR        | 1,0 | any edge              |

| Port 61 external    | * |       | *      |       | *    |      | *      |   |     | P6CR        | 3,2 | any edge              |

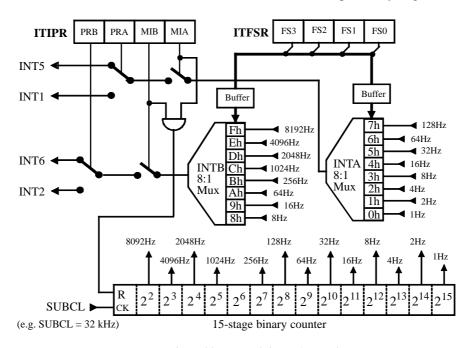

| Interval timer INTA |   | *     |        |       |      | *    |        |   |     | ITIPR       | 0   | 1 of 8 frequencies    |

|                     |   |       |        |       |      |      |        |   |     |             |     | (1 – 128 Hz)          |

| Interval timer INTB |   |       | *      |       |      |      | *      |   |     | ITIPR       | 1   | 1 of 8 frequencies    |

|                     |   |       |        |       |      |      |        |   |     |             |     | (8 – 8192 Hz)         |

| Timer 0             |   | *     |        | *     |      | *    |        | * |     | T0CR        | 0   | overflow/compare/     |

|                     |   |       |        |       |      |      |        |   |     |             |     | end measurement       |

| Timer 1             | * |       | *      |       | *    |      | *      |   |     | T1CR        | 0   | compare               |

X = hardwired (neither optional or software configurable)

# = customer mask option (see "Ordering Information")

In the M44C510, there are eleven hardware interrupt sources which can be programmed to occupy a variety of priority levels. Each source can be individually masked by mask bits in the corresponding control registers. An overview of the possible hardware configurations is shown in table 3.

#### 1.3.2 Software Interrupts

The programmer can generate interrupts using the software interrupt instruction (SWI) which is supported in qFORTH by predefined macros named SWI0...SWI7.

The software triggered interrupt operates in exactly the same way as any hardware triggered interrupt.

The SWI instruction takes the top two elements from the expression stack and writes the corresponding bits via the I/O bus to the interrupt pending register. Thus, by using the SWI instruction, interrupts can be re-prioritized or lower priority processes scheduled for later execution.

<sup>\* =</sup> software configurable (see "Peripheral Modules" section for further details)

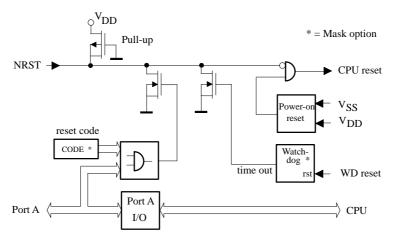

#### 1.4 Hardware Reset

The master reset forces the CPU into a well-defined condition, is unmaskable and is activated independent of the current program state. It can be triggered by either initial supply power-up, a short collapse of the power supply, a watchdog time out, activation of the NRST input or the occurrence of a coded reset on Port A (see figure 9). A master reset activation will reset the interrupt enable flag, the interrupt pending register and the interrupt active register. During the reset phase, the I/O bus control signals are set to 'reset mode' thereby initializing all on-chip peripherals.

Releasing the reset results in a short call instruction (opcode C1h) to the ROM address 008h. This activates the initialization routine \$RESET which in turn initializes all necessary RAM variables, stack pointers and peripheral configuration registers.

#### **Power-on Reset**

The fully integrated power-on reset circuit ensures that the core is held in a reset state until the minimum operating supply voltage has been reached. A reset condition is also generated should the supply voltage drop momentarily below the minimum operating supply.

#### **External Reset (NRST)**

An external reset can be triggered with the NRST pin. To activate an external reset, the pin should be low for a minimum of two machine cycles.

#### Coded Reset (Port A)

The coded reset circuit is connected directly to the Port A terminals. By using a mask option, the user can define a hardwired code combination (e.g., all pins low) which, if occurring on the Port A, will generate a reset in the same way as the NRST pin.

Table 4. Multiple key reset options

| NO_RST | Not used (default)        |

|--------|---------------------------|

| RST2   | BPA0 & BPA1               |

| RST3   | BPA0 & BPA1 & BPA2        |

| RST4   | BPA0 & BPA1 & BPA2 & BPA3 |

Note, that if this option is used, the reset is not maskable and will also trigger if the predefined code is written on to the Port A by the CPU itself. Care should also be taken not to generate an unwanted reset by inadvertently passing through the reset code on input transitions. This applies especially if the pins have a high capacitive load.

#### **Watchdog Reset**

The watchdog's function can be enabled via a mask option and triggers a reset with every watchdog counter overflow. To suppress the watchdog reset, the counter must be regularly reset by reading the watchdog register address (WDRES).

The CPU reacts in exactly the same manner as a reset stimulus from any of the above sources.

Figure 9. Reset configuration

96 11519

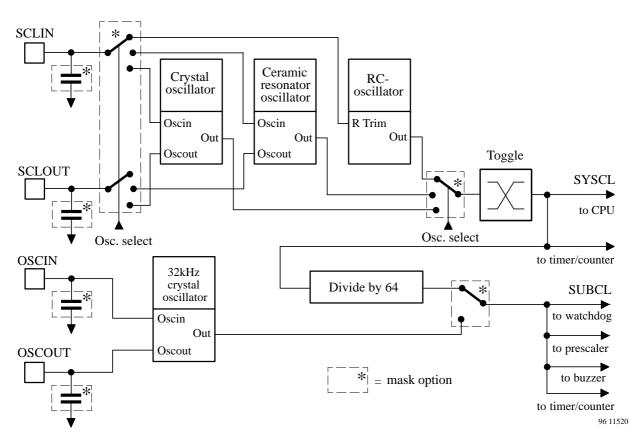

#### 1.5 Clock Generation

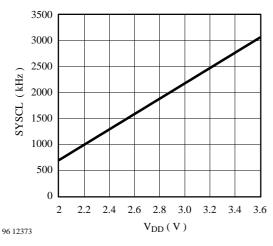

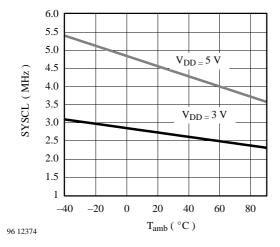

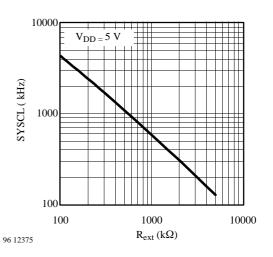

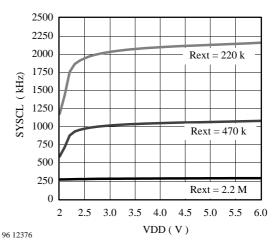

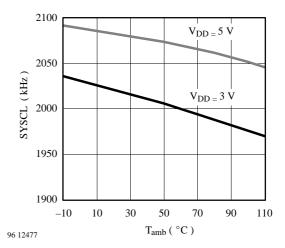

The M44C510 has a dual clock system, a 2-MHz system clock (SYSCL) for the core and a 32-kHz subclock (SUBCL) for the time-keeping peripheral modules (see figure 10). Each clock can be generated from independent on-chip oscillators or they can both be derived from the same high frequency SYSCL oscillator. This is mask selectable - allowing a choice of either an 4-MHz crystal, 4-MHz ceramic resonator or a RC oscillator. All the necessary oscillator circuitry, with the exception of the actual crystal or resonator, are integrated on chip. Therefore, if no exact timing is required, for example, it is possible to use the fully integrated RC oscillator, thus operating without any external components.

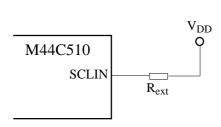

An additional mask option enables a high resolution trimmable RC oscillator whereby the SYSCL can be trimmed with an external resistor between SCLIN and  $V_{DD}$ . In this configuration, the SYSCL frequency can be maintained stable to within a tolerance of  $\pm 10\%$  over the full operating temperature range. A SYSCL frequency of

2 MHz, for example, can be obtained by connecting a 220 k $\Omega$  resistor (see figures 44, 48 and 49).

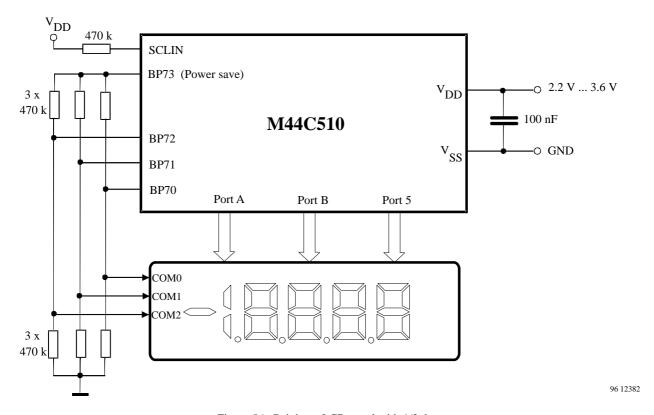

Some applications require only long-term time keeping or low resolution timing. In this case, an on-chip, low-power 32-kHz crystal oscillator can be used to generate the SUBCL. This allows the core to go into SLEEP mode when not used, and therefore greatly reduces power consumption.

If the full 2-MHz timing resolution is required, then either the crystal or resonator oscillator should be used for SYSCL generation.

Should a suitable external 1...4-MHz or 32-kHz clock source be available, then SCLIN (Crystal oscillator configuration) or OSCIN respectively can be used as the input.

Note: A SYSCL frequency of 2 MHz leads an instruction cycle time of 1  $\mu$ s.

Figure 10. Clock module

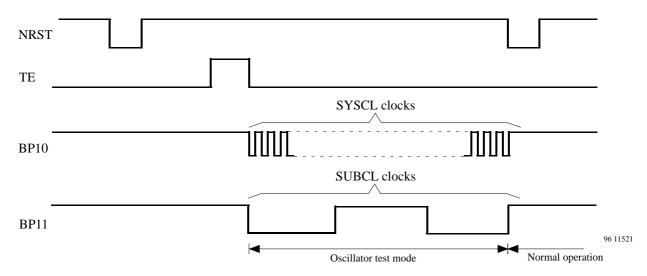

#### 1.5.1 Clock Monitor Mode

Figure 11. Clock monitoring

For trimming purposes, the M44C510 can be put into a clock monitor mode. The test input (TE) must therefore be pulsed high once, whereupon the SYSCL clock will appear on BP10 (Port 1, bit 0) and SUBCL clock on Port BP11 (Port 1, bit 1). To put BP10 and BP11 back into normal operation, the reset must be reapplied (see figure 11).

## 1.6 Sleep Mode

The sleep mode is a shutdown condition which is used to reduce the average system power consumption in applications where the µC is not fully utilized. In this mode, the system clock is stopped. The sleep mode is entered with the SLEEP instruction. This instruction sets the condition code register interrupt enable bit (I) to enable all interrupts and stops the core. During the sleep mode, the peripheral modules remain active and are able to generate interrupts. The  $\mu C$  exits the sleep mode with any interrupt or a reset. The sleep mode can only be maintained when no interrupt pending or active register bits are set. The application of the \$AUTOSLEEP routine ensures the correct function of the sleep mode. The total power consumption is directly proportional to the active time of the µC. For a rough estimation of the expected average system current consumption, the following formula should be used:

$$I_{total} (V_{DD}, f_{syscl}) = I_{Sleep} + (I_{DD} * T_{active} / T_{total})$$

$I_{DD}$  depends on  $V_{DD}$  and  $f_{syscl}.$  Using a 32-kHz crystal, the SLEEP current ( $I_{Sleep}$ ) is typically less than 1  $\mu A$ . The active time of the core and the total emulation time are displayed in a separate window of the MARC4 emulator software.

# 2 Peripheral Modules

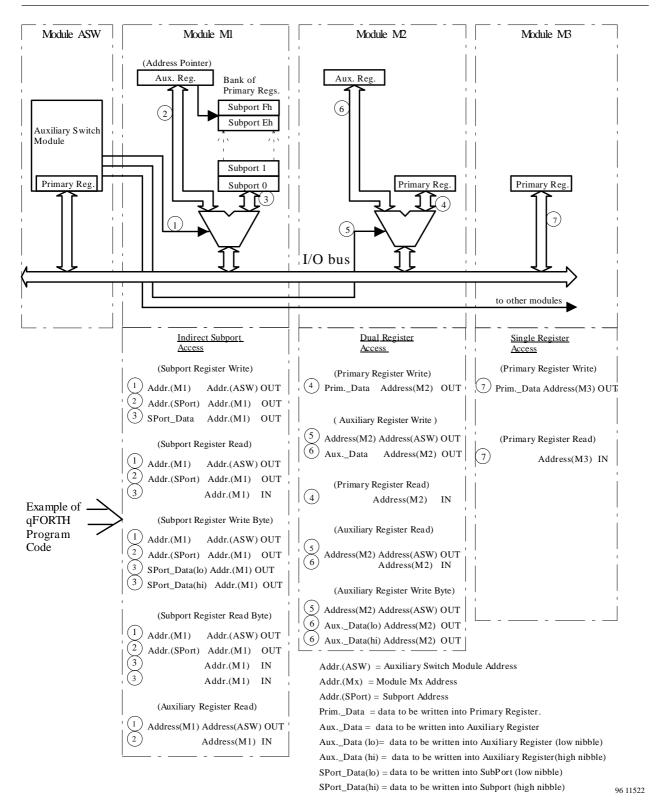

# 2.1 Addressing Peripherals

Accessing the peripheral modules takes place via the I/O bus (see figure 12). The IN or OUT instructions allow direct addressing of up to 16 I/O modules. A dual register addressing scheme has been adopted which addresses the "primary register" directly. To address the "auxiliary register", the access must be switched with an "auxiliary switching module". Thus, a single IN (or OUT) to the module address will read (or write) into the module primary register. Accessing the auxiliary register is performed with the same instruction preceded by writing the module address into the auxiliary switching module. Byte-wide registers are accessed by multiple IN (or OUT) instructions. Extended addressing is used for more complex peripheral modules, with a larger number of registers. In this case, a bank of up to 16 subport registers are indirectly addressed with the subport address being initially written into the auxiliary register.

Figure 12. Example of I/O addressing

Table 5. M44C510 Peripheral addresses

| Address |          | Name          | Write<br>/Read | Function                                   |  |  |  |  |

|---------|----------|---------------|----------------|--------------------------------------------|--|--|--|--|

| 0       |          | P0DAT         | W/R            | Port 0 – data register/input data          |  |  |  |  |

| 1       | 1        |               | W/R            | Port 1 – data register/input data          |  |  |  |  |

| 2       | 2        |               | W              | Port A – interrupt priority register       |  |  |  |  |

|         | Aux.     | PAICR         | W              | Port A – interrupt control register        |  |  |  |  |

| 3       | Į.       | PBIPR         | W              | Port B – interrupt priority register       |  |  |  |  |

|         |          | WDRES         | R              | Watchdog reset                             |  |  |  |  |

|         | Aux.     | PBICR         | W              | Port B – interrupt control register        |  |  |  |  |

| 4       |          | P4DAT         | W/R            | Port 4 – data register/pin data            |  |  |  |  |

|         | Aux.     | P4DDR         | W              | Port 4 – data direction register           |  |  |  |  |

| 5       |          | P5DAT         | W/R            | Port 5 – data register/pin data            |  |  |  |  |

|         | Aux.     | P5DDR         | W              | Port 5 – data direction register           |  |  |  |  |

| 6       | 1 10,111 | P6DAT         | W/R            | Port 6 – data register/pin data            |  |  |  |  |

|         | Aux      | P6CR          | W              | Port 6 – control register (byte)           |  |  |  |  |

| 7       | 7 tux    | P7DAT         | W/R            | Port 7 – data register/pin data            |  |  |  |  |

| ,       | Aux.     | P7DDR         | W              | Port 7 – data direction register           |  |  |  |  |

| 8       | Aux.     | ASW           | W              | Auxiliary switch register                  |  |  |  |  |

| 9       |          | TCM           | W/R            | Data to/from subport addressed by TCX      |  |  |  |  |

| 9       | A        | TOSR          | R              | Timer 0 interrupt status register          |  |  |  |  |

|         | Aux.     |               | +              |                                            |  |  |  |  |

|         |          | TCX           | W              | Timer/counter subport address pointer      |  |  |  |  |

|         | 1 -      | bport address | ***            | m o i                                      |  |  |  |  |

|         | 0        | T0MO          | W              | Timer 0 mode register                      |  |  |  |  |

|         | 1        | T0CR          | W              | Timer 0 control register                   |  |  |  |  |

|         | 2        | T1MO          | W              | Timer 1 mode register                      |  |  |  |  |

|         | 3        | T1CR          | W              | Timer 1 control register                   |  |  |  |  |

|         | 4        | TCMO          | W              | Timer/counter mode register                |  |  |  |  |

|         | 5        | TCIO          | W              | Timer/counter I/O control register         |  |  |  |  |

|         | 6        | TCCR          | W              | Timer/counter control register             |  |  |  |  |

|         | 7        | TCIP          | W              | Timer/counter interrupt priority           |  |  |  |  |

|         | 8        | T1CP          | W              | Timer 1 compare register (byte)            |  |  |  |  |

|         |          | T1CA          | R              | Timer 1 capture register (byte)            |  |  |  |  |

|         | 9        | T0CP          | W              | Timer 0 compare register (byte)            |  |  |  |  |

|         |          | T0CA          | R              | Timer 0 capture register (byte)            |  |  |  |  |

|         | A        | BZCR          | W              | Buzzer control register                    |  |  |  |  |

|         | B-F      | 7             | •              | Reserved                                   |  |  |  |  |

| A       |          | PADAT         | W/R            | Port A – data register/pin data            |  |  |  |  |

|         | Aux.     | PADDR         | W              | Port A – data direction register           |  |  |  |  |

| В       |          | PBDAT         | W/R            | Port B – data register/pin data            |  |  |  |  |

|         | Aux.     | PBDDR         | W              | Port B – data direction register           |  |  |  |  |

| С       |          | PCDAT         | W/R            | Port C – data register/pin data            |  |  |  |  |

|         | Aux.     | PCDDR         | W              | Port C – data direction register           |  |  |  |  |

| D       | 1        | RBR           | W              | Rom bank switch register                   |  |  |  |  |

| E       |          | _             | _              | Reserved                                   |  |  |  |  |

| F       |          | ITFSR         | W              | Interval timer frequency select register   |  |  |  |  |

| •       | Aux.     | ITIPR         | W              | Interval timer interrupt priority register |  |  |  |  |

33

#### 2.2 Bidirectional Ports

With the exception of Port 6 and Port C, all other ports (0, 1, 4, 5, 7, A and B) are 4 bits wide. Port 6 and Port C have a data width of 2 bits (bit 0 and bit 1). All these ports may be used for data input or output. All ports are equipped with Schmitt-trigger inputs and a variety of mask options

for open drain, open source and full complementary outputs and pull-up and pull-down transistors. All Port Data Registers (PxDAT) are I/O mapped to the primary address register of the respective port address, and the Port Data Direction Register (PxDDR) to the corresponding auxiliary register.

#### Port Data Register (PxDAT)

Primary register address: 'Port address'hex

|       | Bit 3* | Bit 2  | Bit 1  | Bit 0  |                    |

|-------|--------|--------|--------|--------|--------------------|

| PxDAT | PxDAT3 | PxDAT2 | PxDAT1 | PxDAT0 | Reset value: 1111b |

<sup>\*</sup> Bit  $3 \rightarrow MSB$ , bit  $0 \rightarrow LSB$

#### Port Data Direction Register (PxDDR)

Auxiliary register address: 'Port address'hex

|       | Bit 3  | Bit 2  | Bit 1  | Bit 0  |                    |

|-------|--------|--------|--------|--------|--------------------|

| PxDDR | PxDDR3 | PxDDR2 | PxDDR1 | PxDDR0 | Reset value: 1111b |

Value: 1111b means all pins in input mode

Table 6. Port Data Direction Register (PxDDR)

| Code    | Function            |

|---------|---------------------|

| 3 2 1 0 |                     |

| x x x 1 | BPx0 in input mode  |

| x x x 0 | BPx0 in output mode |

| x x 1 x | BPx1 in input mode  |

| x x 0 x | BPx1 in output mode |

| x 1 x x | BPx2 in input mode  |

| x 0 x x | BPx2 in output mode |

| 1 x x x | BPx3 in input mode  |

| 0 x x x | BPx3 in output mode |

There are five different types of bidirectional ports:

- Type 1 (Ports 0 and 1) 4-bit wide, bidirectional ports with automatic full bus width direction switching.

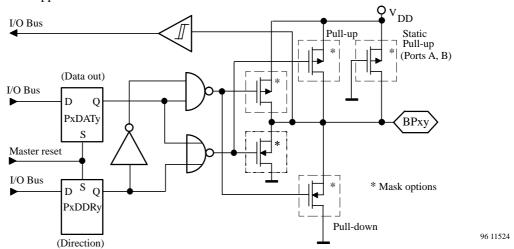

- Type 2 (Ports 5 and 7) 4-bit wide, Port C is a 2-bit wide, bitwise programmable high drive I/O port.

- Type 3 (Ports A and B) 4-bit wide, bitwise programmable bidirectional ports with optional keyboard pull-ups.

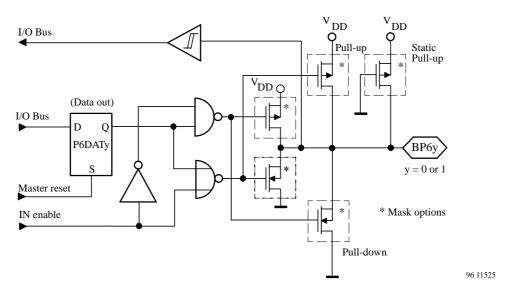

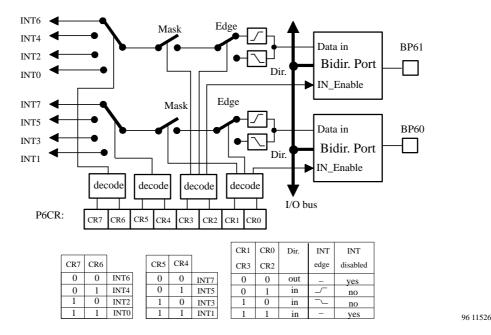

- Type 4 (Port 6) 2-bit wide, bitwise programmable bidirectional ports with optional bus pullups and programmable interrupt logic.

- Type 5 (Port 4) 4-bit wide, bitwise programmable bidirectional port also provides the I/O interface to Timer 0 and the Buzzer.

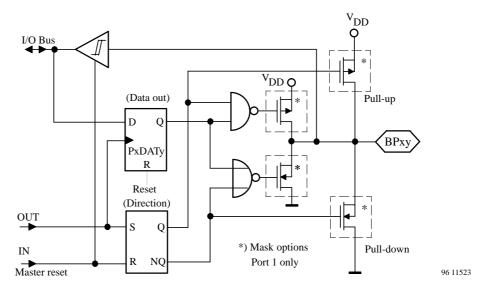

## 2.2.1 Port 0, Port 1 – Bidirectional Ports Type 1