# LC5824, LC5823, LC5822

4-Bit Single-Chip Microcontrollers Featuring 4 KB to 8 KB of ROM, 1 Kbit of RAM, and an LCD Driver for Medium Speed Small-Scale Control Applications

# Overview

The LC5822, LC5823, and LC5824 are CMOS microcontrollers that feature the low-voltage operation required for battery-power applications and that provide 4 KB, 6 KB, or 8 KB of ROM, 1 kilobit of RAM, and an LCD driver.

These microcontrollers support an instruction set based on that of the earlier LC5800, LC5812, and LC5814 for excellent efficiency in software development.

# Applications

- LCD display in multi-function watches, timers, and other products

- Control and LCD display in timers

- Control and LCD display in miniature test equipment, health maintenance equipment, and other products

- These microcontrollers are optimal for products that include an LCD display, especially battery powered products.

| Power<br>options<br>supply | Cycle<br>times | Supply<br>voltage<br>range      | Notes                                      |

|----------------------------|----------------|---------------------------------|--------------------------------------------|

| EXT-V                      | 10 µs          | $V_{DD}$ = 2.3 to 3.6 V         | When an 800-kHz ceramic oscillator is used |

| EXT-V                      | 20 µs          | $V_{DD}$ = 2.3 to 3.6 V         | When an 400-kHz ceramic oscillator is used |

| EXT-V                      | 61 µs          | V <sub>DD</sub> = 2.3 to 3.6 V  | When an 65-kHz crystal oscillator is used  |

| EXT-V                      | 122 µs         | $V_{DD}$ = 2.0 to 3.6 V         | When an 32-kHz crystal oscillator is used  |

| Li                         | 122 µs         | V <sub>DD</sub> = 2.6 to 3.6 V* | When an 32-kHz crystal oscillator is used  |

| Ag                         | 122 µs         | V <sub>DD</sub> = 1.3 to 1.65 V | When an 32-kHz crystal oscillator is used  |

Wide Allowable Operating Ranges

Note\*: When the backup flag is set, the BAK pin is connected to  $\mathsf{V}_{\mathsf{DD}}$

# **Features**

• These microcontrollers are high-end versions of the LC5800 and provide the following features.

Low Current Drain \* In halt mode (typical)

- Ceramic oscillator 400 kHz (3.0 V) 200 µA

- Crystal oscillator 32 kHz (1.5 V, Ag specifications)

3.0 µA (LCD biases other than 1/3)

4.5 µA (LCD drive: 1/3 bias)

- Crystal oscillator 32 kHz (3.0 V, Li specifications)

2.0 µA (LCD biases other than 1/3) 6.0 µA (LCD drive: 1/3 bias)

Timer and Counter Functions

- One 8-bit programmable timer (May be used as an event counter)

- One 8-bit programmable reload timer

- Time base timer (for clocks)

- Watchdog timer

- 8-bit serial I/O (3-pin synchronous system)

Standby Functions

• Clock standby function (halt mode)

Only the oscillator circuits, the divider circuit, and the LCD driver operate. All other internal operations are stopped. This provides a power-saving function in which current drain is minimized, and allows a clock function to be implemented easily with low power dissipation.

Furthermore, low-speed and high-speed modes can be implemented by setting the operating modes of the two oscillator circuits.

- Full standby function (hold mode)

- Halt mode can be cleared by any of two external and two internal interrupts.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN Improved I/O Functions

- External interrupt pins

- Input pins that can clear halt mode: 10 pins (maximum)

- Input ports with input resistors that can be controlled from software: 8 pins (maximum)

- Pins with a function that prevents the input port floating state: 8 pins (maximum)

- LCD drive pins: 4 pins (common), 42 pins (segment outputs)

- General-purpose I/O ports:

#### 16 pins (when all 4 P port pins are used)

- General-purpose inputs: 8 pins

- General-purpose outputs (1): 1 pin (the ALM pin)

| • General-purpose outputs (2 | ):42 pins (when all 42 of the |

|------------------------------|-------------------------------|

|                              | LCD segment outputs are       |

|                              | switched over to function as  |

|                              | general-purpose outputs)      |

| • 8-bit serial output port:  | 1 set (3 pins: output, input, |

|                              | and clock)                    |

Functional Overview

- Program ROM: 4096 × 16 bits LC5824 3072 × 16 bits LC5823 2048 × 16 bits LC5822

- Internal RAM:  $256 \times 4$  bits

- All instructions execute in a single cycle.

- Extensive set of interrupt functions for clearing halt and hold mode

- 8 halt mode clearing functions

- 5 hold mode clearing functions

- 6 interrupt functions

- Subroutines can be nested up to 8 levels (Specialpurpose registers that are shared with the interrupt function are built in.)

- · Powerful hardware to increase system processing capacity

- Segment port related hardware

- Built-in segment PLA circuit

- Built-in segment decoder

- Support for six different LCD drive specifications Outputs can be switched to CMOS levels

- Built-in 8-bit synchronous serial I/O circuit

- 8-bit read/write timer (plus a separate 8-bit prescaler; can be used as and event counter)

- 8-bit reload timer (plus built-in 8-bit prescaler)

- Built-in 8-bit prescaler (for use with timer 1, timer 2, and the serial counter)

- All of RAM can be used a working area (RAM bank system)

- Dedicated data pointer register for RAM access

- 15-stage divider circuit for clocks (also used as the LCD voltage alternation frequency generator)

- 8-bit table reference function (reads 8-bit ROM data)

- Chattering prevention circuit (on two ports)

- Alarm signal generation circuit

• LCD panel drive output pins with high flexibility (42 pins)

| Drive system | Number of driven segments | Required number of common pins |

|--------------|---------------------------|--------------------------------|

| bias · duty  | 168 segments              | 4 pins                         |

| bias · duty  | 126 segments              | 3 pins                         |

| bias · duty  | 168 segments              | 4 pins                         |

| bias · duty  | 126 segments              | 3 pins                         |

| bias · duty  | 84 segments               | 2 pins                         |

| Static drive | 42 segments               | 1 pin                          |

The LCD output pins can be switched to function as general-purpose outputs.

CMOS/p-channel/n-channel type combinations: Up to 42 pins

- An alternation frequency appropriate for the LCD panel used can be selected.

- An oscillator appropriate for your system's specifications can be selected.

- A 32- or 65-kHz crystal oscillator can be selected (Used when a clock function is required or for low current drain operation.)

- A ceramic oscillator with a frequency from 400 kHz to 2 MHz can be selected (when high-speed operation is required.)

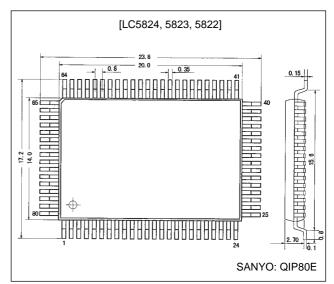

Available delivery formats: QIP-80 and chip

# **Package Dimensions**

#### unit: mm

#### 3174-QFP80E

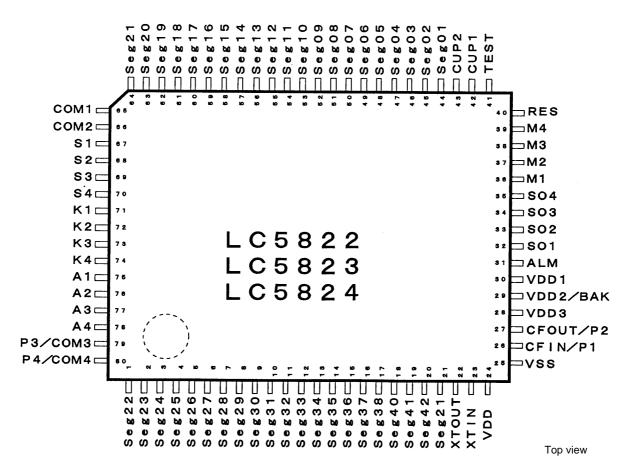

#### **Pin Assignment**

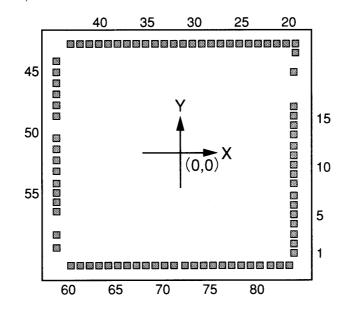

#### **Pad Arrangement**

Chip size: 4.92 mm  $\times$  5.15 mm Pad size: 120  $\mu m$   $\times$  120  $\mu m$  Chip thickness 480  $\mu m$  (chip specifications)

#### **Pad Coordinates**

|         | D.              | Coordi | nates |         | 5.                    | Coordi | nates |         | Ċ.            | Coordi | nates |

|---------|-----------------|--------|-------|---------|-----------------------|--------|-------|---------|---------------|--------|-------|

| PAD No. | Pin             | Χμm    | Υμm   | PAD No. | Pin                   | Χμm    | Υμm   | PAD No. | Pin           | Χμm    | Υµm   |

| 60      | Seg 22          | -2030  | -2178 | 5       | V <sub>DD</sub> 3     | 2257   | -1212 | 33      | Seg 11        | -194   | 2178  |

| 61      | Seg 23          | -1850  | -2178 | 6       | V <sub>DD</sub> 2/BAK | 2257   | -1032 | 34      | Seg 12        | -374   | 2178  |

| 62      | Seg 24          | -1670  | -2178 | 7       | V <sub>DD</sub> 1     | 2257   | -852  | 35      | Seg 13        | -546   | 2178  |

| 63      | Seg 25          | -1490  | -2178 | 8       | ALM                   | 2257   | -601  | 36      | Seg 14        | -726   | 2178  |

| 64      | Seg 26          | -1310  | -2178 | 9       | SO1                   | 2257   | -419  | 37      | Seg 15        | -906   | 2178  |

| 65      | Seg 27          | -1130  | -2178 | 10      | SO2 I/O port          | 2257   | -236  | 38      | Seg 16        | -1086  | 2178  |

| 66      | Seg 28          | -950   | -2178 | 11      | SO3 I/O port          | 2257   | 56    | 39      | Seg 17        | -1266  | 2178  |

| 67      | Seg 29          | -770   | -2178 | 12      | SO4 I/O port          | 2257   | 132   | 40      | Seg 18        | -1446  | 2178  |

| 68      | Seg 30          | -590   | -2178 | 13      | M1                    | 2257   | 364   | 41      | Seg 19        | -1626  | 2178  |

| 69      | Seg 31          | -410   | -2178 | 14      | M2 I/O port           | 2257   | 544   | 42      | Seg 20        | -1806  | 2178  |

| 70      | Seg 32          | -230   | -2178 | 15      | M3 I/O port           | 2257   | 724   | 43      | Seg 21        | -1986  | 2178  |

| 71      | Seg 33          | -50    | -2178 | 16      | M4 I/O port           | 2257   | 904   | 44      | COM1          | -2270  | 1871  |

| 72      | Seg 34          | 122    | -2178 | 17      | RES I/O port          | 2257   | 1636  | 45      | COM2          | -2270  | 1628  |

| 73      | Seg 35          | 302    | -2178 | 18      | Test                  | 2330   | 1998  | 46      | S1            | -2270  | 1367  |

| 74      | Seg 36          | 482    | -2178 | 19      | Test                  | 2330   | 2178  | 47      | S2 Input port | -2270  | 1140  |

| 75      | Seg 37          | 662    | -2178 | 20      | TST                   | 2150   | 2178  | 48      | S3 Input port | -2270  | 960   |

| 76      | Seg 38          | 842    | -2178 | 21      | CUP1                  | 1970   | 2178  | 49      | S4 Input port | -2270  | 734   |

| 77      | Seg 39          | 1022   | -2178 | 22      | CUP2                  | 1790   | 2178  | 50      | K1            | -2270  | 328   |

| 78      | Seg 40          | 1202   | -2178 | 23      | Seg 1                 | 1606   | 2178  | 51      | K2 Input port | -2270  | 88    |

| 79      | Seg 41          | 1382   | -2178 | 24      | Seg 2                 | 1426   | 2178  | 52      | K3 Input port | -2270  | -140  |

| 80      | Seg 42          | 1562   | -2178 | 25      | Seg 3                 | 1246   | 2178  | 53      | K4 Input port | -2270  | -380  |

| 81      | XC              | 1774   | -2178 | 26      | Seg 4                 | 1066   | 2178  | 54      | A1            | -2270  | -593  |

| 82      | XTOUT           | 1954   | -2178 | 27      | Seg 5                 | 886    | 2178  | 55      | A2 I/O ports  | -2270  | -773  |

| 83      | XTIN            | 2134   | -2178 | 28      | Seg 6                 | 706    | 2178  | 56      | A3 I/O ports  | -2270  | -953  |

| 1       | V <sub>DD</sub> | 2257   | -1959 | 29      | Seg 7                 | 526    | 2178  | 57      | A4 I/O ports  | -2270  | -1133 |

| 2       | V <sub>SS</sub> | 2257   | -1779 | 30      | Seg 8                 | 346    | 2178  | 58      | COM3/P3       | -2270  | -1602 |

| 3       | CFIN/P1         | 2257   | -1599 | 31      | Seg 9                 | 166    | 2178  | 59      | COM4/P4       | -2270  | -1846 |

| 4       | CFOUT/P2        | 2257   | -1402 | 32      | Seg 10                | -14    | 2178  |         |               |        |       |

Note: • The pin numbers are the QIP-80E mass-production package pin numbers.

- The test pin (TST) must be connected to  $V_{\text{SS}}.$

• Pads number 42 and 43 in the chip version must be left open.

• Do not use solder dip techniques to mount the QIP-80E package version.

- In the chip version, the substrate must be either connected to  $V_{\mbox{SS}}$  or left open.

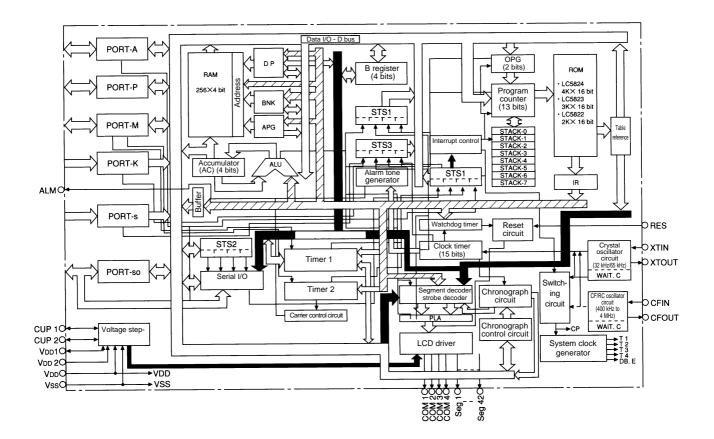

#### System Block Diagram

- RAM: Data memory

- ROM: Program memory

- DP: Data pointer register

- BNK: Bank register

- APG: RAM page flag

- AC: Accumulator

- ALU: Arithmetic and logic unit

- B: B register

- OPG: ROM page flag

- PC: Program counter

- IR: Instruction register

- STS1: Status register 1

- STS2: Status register 2

- STS3: Status register 3

- STS4: Status register 4

- PLA: Programmed logic array used for segment data and strobe functions

- WAIT.C: Wait time counter

## **Pin Functions**

| Pin No.              | Pin                                                             | I/O             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Options                                                                                                                   | Status at reset                                                                                                                                                                                               |

|----------------------|-----------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24<br>25             | V <sub>DD</sub><br>V <sub>SS</sub>                              | -               | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                           |                                                                                                                                                                                                               |

| 25                   | VSS                                                             |                 | LCD drive power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                           |                                                                                                                                                                                                               |

| 30<br>29<br>28       | V <sub>DD</sub> 1<br>V <sub>DD</sub> 2/BAK<br>V <sub>DD</sub> 3 |                 | Power supply<br>specifications         Ag         Li         EXTV           Pin blas         NON&/A6/2         1/3         NON&/A6/2         1/3         VID           VDD         O         O         O         O         O         O         O           VDD3         O         O         O         O         O         O         O           VDD3         O         O         O         O         O         O         O         O           VDD1         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O | <ul> <li>Ag specifications</li> <li>Li specifications</li> <li>EXT-V specifications</li> </ul>                            |                                                                                                                                                                                                               |

| 42<br>43             | CUP1<br>CUP2                                                    | _               | Connections of the LCD power supply step-up (step-down) capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                           |                                                                                                                                                                                                               |

| 26<br>27             | CFIN<br>CFOUT                                                   | Input<br>Output | System clock oscillator connections<br>• Ceramic element connections (CF specifications)<br>• RC component connections (RC specifications)<br>*: This oscillator circuit is stopped when a STOP or SLOW<br>instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>CF specifications</li> <li>RC specifications</li> <li>Unused</li> </ul>                                          |                                                                                                                                                                                                               |

| 23<br>22             | XTIN<br>XTOUT                                                   | Input<br>Output | Used for reference counting (clock specifications, LCD<br>alternation frequency) and as the system clock.<br>• 32-kHz crystal oscillator<br>• 65-kHz crystal oscillator<br>*: This oscillator circuit is stopped when a STOP instruction is<br>executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>32-kHz specifications</li> <li>65-kHz specifications</li> <li>38-kHz specifications</li> <li>Unused</li> </ul>   |                                                                                                                                                                                                               |

|                      | хс                                                              | _               | Used for the phase compensation capacitor connected between<br>this pin and XTOUT and XTIN. This pin is only used in the chip<br>product.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                           |                                                                                                                                                                                                               |

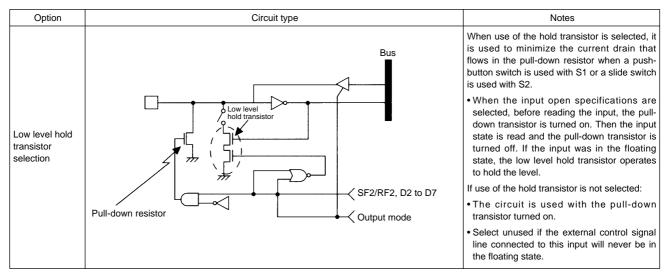

| 67<br>68<br>69<br>70 | S1<br>S2<br>S3<br>S4                                            | Input           | Input-only port<br>• Input pins used to acquire input data to RAM<br>• 1.95-ms and 7.8-ms chattering exclusion circuits included.<br>• Pull-down resistors are built in.<br>Note: the 1.95 ms and 7.8 ms values are for a ø0 of<br>32.768 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Presence or absence of<br>low-level hold<br>transistors                                                                   | • Pull-down resistors<br>enabled<br>Note: After a reset is<br>cleared, these pins go to<br>the floating state.                                                                                                |

| 71<br>72<br>73<br>74 | K1<br>K2<br>K3<br>K4                                            | Input           | Input-only port<br>Input pins used to acquire input data to RAM<br>1.95-ms and 7.8-ms chattering exclusion circuits included.<br>Pull-down resistors are built in.<br>Note: the 1.95 ms and 7.8 ms values are for a ø0 of<br>32.768 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Presence or absence of<br>low-level hold<br>transistors                                                                   | • Pull-down resistors<br>enabled<br>Note: After a reset is<br>cleared, these pins go to<br>the floating state.                                                                                                |

| 36<br>37<br>38<br>39 | M1<br>M2<br>M3<br>M4                                            | I/O             | <ul> <li>I/O port</li> <li>Input pins used to acquire input data to RAM.</li> <li>Output pins used to output RAM data.</li> <li>M4 is also used as the TM1 external clock input in TM1 mode 3.</li> <li>M3 is also used for HEF8 halt mode clear control.</li> <li>*: The minimum period for clock signal inputs is twice the cycle time</li> <li>Pull-down resistors are built in.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>Presence or absence of<br/>low-level hold<br/>transistors</li> <li>Output type: CMOS or<br/>p-channel</li> </ul> | <ul> <li>Pull-down resistors<br/>enabled</li> <li>Note: After a reset is<br/>cleared, these pins go to<br/>the floating state.</li> <li>Input mode</li> <li>The output latch data is<br/>set to 1.</li> </ul> |

| 26<br>27<br>79<br>80 | P1<br>P2<br>P3<br>P4                                            | I/O             | <ul> <li>I/O port</li> <li>Input pins used to acquire input data to RAM.</li> <li>Output pins used to output RAM data.</li> <li>Pull-down resistors are built in.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The same as those for<br>M1 to M4. However, only<br>for valid ports.                                                      | The same as those for<br>M1 to M4. However, only<br>for valid ports.                                                                                                                                          |

| 76<br>77<br>78<br>79 | A1<br>A2<br>A3<br>A4                                            | I/O             | <ul> <li>I/O port</li> <li>Input pins used to acquire input data to RAM.</li> <li>Output pins used to output RAM data.</li> <li>Pull-down resistors are built in.</li> <li>A1 is also used as the external interrupt request control input signal (INT).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The same as those for M1 to M4.                                                                                           | The same as those for<br>M1 to M4.                                                                                                                                                                            |

| Pin No.              | Pin                                  | I/O    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | F                                                                                                                                                                                                                                                                                                              | unction                                                                              |                                                                                                 |          | Options                                                                                                                                                                                                                                                                                                                                                                                                                                              | Status at reset                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|--------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32<br>33<br>34<br>35 | SO1<br>SO2<br>SO3<br>SO4             | I/O    | <ul> <li>I/O port</li> <li>Input pins used to acquire input data to RAM.</li> <li>Output pins used to output RAM data.</li> <li>Pull-down resistors are built in.</li> <li>SO1 to SO3 are also used as the serial interface pins.</li> <li>The serial interface function can be selected under program control.</li> <li>Pin functions:</li> <li>SO1: Serial input</li> <li>SO2: Serial output</li> <li>SO3: Serial clock</li> <li>The serial clock can be taken from either internal or external sources, and can be set up to detect either rising or falling edges under program control.</li> </ul> |                                                                                                                                                                                                                                                                                                                |                                                                                      |                                                                                                 |          | Identical to M1 through<br>M4                                                                                                                                                                                                                                                                                                                                                                                                                        | Identical to M1 through<br>M4                                                                                                                                                                                                                                                                                                                                                                                   |

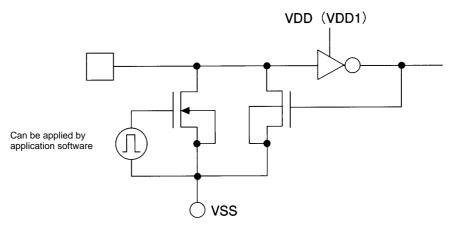

| 31                   | ALM                                  | Output | Output-only pin<br>• A signal modula<br>program contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                | ø3, or ø4 c                                                                          | can be outp                                                                                     | ut under |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low-level output                                                                                                                                                                                                                                                                                                                                                                                                |

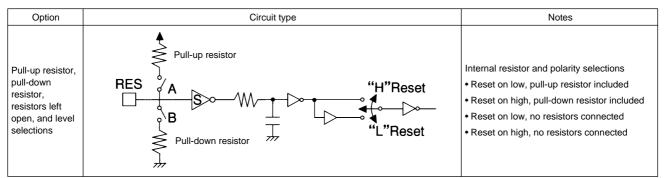

| 40                   | RES                                  | Input  | <ul> <li>The program co</li> <li>The reset input</li> <li>Either a pull-up</li> <li>Note: Application</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IC internal reset input<br>• The program counter is set to point to location 00H.<br>• The reset input level can be set to be either high or low.<br>• Either a pull-up or a pull-down resistor is built in.<br>Note: Applications must apply the reset signal level for at least<br>500 us to effect a reset. |                                                                                      |                                                                                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | or<br>v                                                                                                                                                                                                                                                                                                                                                                                                         |

| 44<br>64<br>1<br>21  | Seg 22<br>Seg 21<br>Seg 22<br>Seg 42 | Output | LCD panel driv<br>(1) Static<br>(2) 1/2 bias 1/<br>(3) 1/2 bias 1/<br>(4) 1/2 bias 1/<br>(5) 1/3 bias 1/<br>(6) 1/3 bias 1/<br>One of items (1)<br>General-purpos<br>(1) CMOS outp<br>(2) p-channel o<br>(3) n-channel o<br>One of items (1)<br>The adoption o<br>means that the<br>LCD/general-pu<br>Output latch co<br>standby states                                                                                                                                                                                                                                                                 | LCD panel drive outputs/general-purpose outputs  LCD panel drive                                                                                                                                                                                                                                               |                                                                                      |                                                                                                 |          | <ul> <li>Switching between LC<br/>drive output and<br/>general-purpose outp</li> <li>Switching between the<br/>LCD drive type option<br/>—Static</li> <li>—1/2 bias 1/2 duty</li> <li>—1/2 bias 1/3 duty</li> <li>—1/2 bias 1/4 duty</li> <li>—1/3 bias 1/4 duty</li> <li>—1/3 bias 1/4 duty</li> <li>General-purpose outp<br/>type switching</li> <li>—CMOS</li> <li>—p-channel open-dra</li> <li>—Standby mode output<br/>latch control</li> </ul> | <ul> <li>—All off</li> <li>* Determined by the<br/>master options</li> <li>• When used as general-<br/>purpose outputs:</li> <li>—High level</li> <li>—Low level</li> <li>* Determined by the<br/>master options</li> <li>Note: When a</li> <li>combination of LCD drive<br/>and general-purpose<br/>outputs is selected, these</li> <li>pins will be either:</li> <li>All lit/high-level output, or</li> </ul> |

| 65<br>66<br>79<br>80 | COM1<br>COM2<br>COM3<br>COM4         | Output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | lists which<br>nat the lister<br>ions when a<br>Static<br>O<br>X<br>X<br>X<br>X<br>32 Hz<br>he "X" sym                                                                                                                                                                                                         | pins are us<br>d alternatio<br>ø0 is 32.760<br>1/2 duty<br>O<br>X<br>X<br>X<br>32 Hz | ed in each<br>n frequenci<br>8 kHz.<br>1/3 duty<br>0<br>0<br>0<br>X<br>42.7 Hz<br>es that the c | 1/4/duty | ıg                                                                                                                                                                                                                                                                                                                                                                                                                                                   | * In products with the CF<br>specifications, the<br>alternation frequency<br>signal stops briefly.                                                                                                                                                                                                                                                                                                              |

| 41                   | TST                                  | Input  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>In the QIP-80 version, this pin must be connected to V<sub>SS</sub>.</li> <li>In the chip version, this pin must be left open or connected to</li> </ul>                                                                                                                                              |                                                                                      |                                                                                                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _                    | TEST<br>TEST                         | _      | Test pins.<br>(These are not u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | sed in the o                                                                                                                                                                                                                                                                                                   | device user                                                                          | interface.)                                                                                     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 |

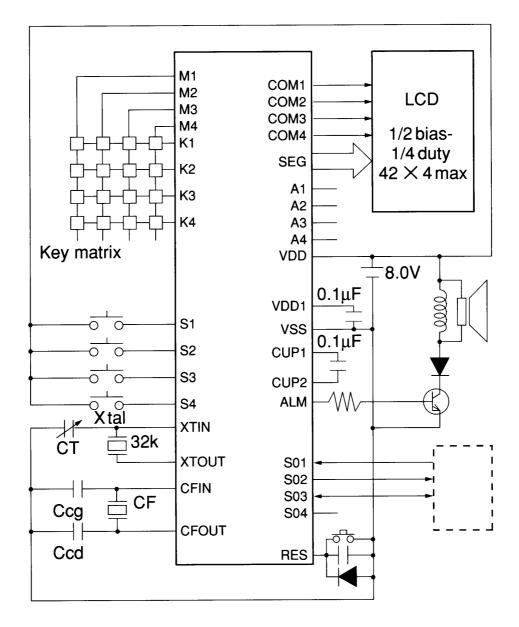

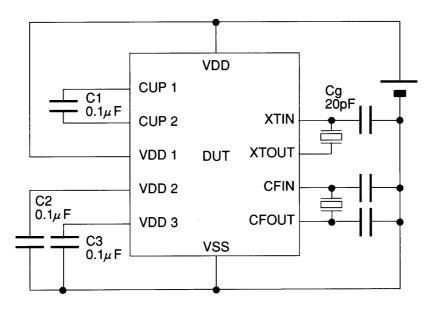

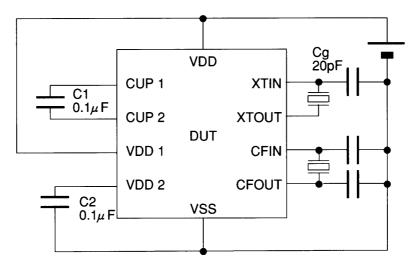

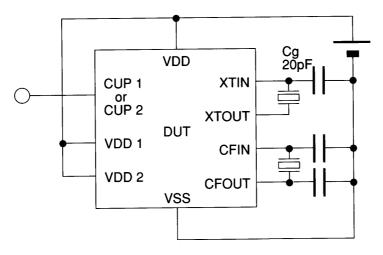

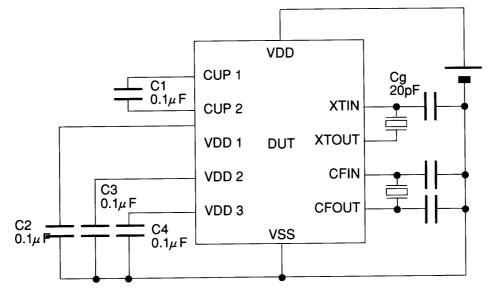

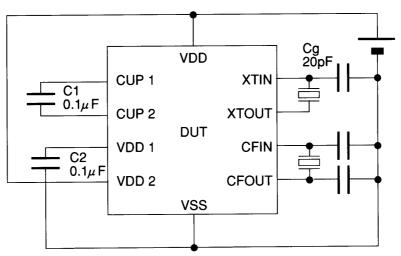

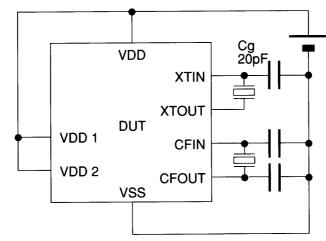

Sample Application Circuit LCD : 1/2 bias — 1/4 duty

# **Oscillator Circuit Options**

| Option                                      | Circuit type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Notes                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC & Xtal                                   | CFIN<br>CFIN<br>S<br>CFOUT<br>T<br>S<br>CFOUT<br>T<br>S<br>CFOUT<br>T<br>S<br>CFOUT<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T<br>T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>The cycle time is 4 times the f1 period.</li> <li>The divider circuit outputs (ø1 through ø15) are used as the clock time base, the LCD drive waveform generation clock, and for S/K port chattering prevention.</li> <li>OSC1 is stopped by the execution of a SLOW instruction.</li> </ul>               |

| CF & Xtal<br>• 400 kHz (CF)<br>• 4 MHz (CF) | CFIN<br>CFIN<br>CFI<br>T1<br>CFU<br>T1<br>T2<br>T3<br>T3<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4<br>T4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>The cycle time is 4 times n times the f1 period. (n:1)</li> <li>The divider circuit outputs (ø1 through ø15) are used as the clock time base, the LCD drive waveform generation clock, and for S/K port chattering prevention.</li> <li>OSC1 is stopped by the execution of a SLOW instruction.</li> </ul> |

| RC                                          | VSS TI<br>VSS TI<br>VS | <ul> <li>The cycle time is 4 times the f1 period.</li> <li>The divider circuit outputs (ø1 through ø15) are used as the clock time base, the LCD drive waveform generation clock, and for S/K port chattering prevention.</li> </ul>                                                                                |

| Option                       | Circuit type                                                                                                                               | Notes                                                                                                                                                                                                                                                                                                                                |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CF<br>• 400 kHz<br>• 4 MHz   | CFIN 50<br>CFIN 50<br>0<br>1/n 1/n T2<br>T3<br>T4<br>HALT<br>VSS                                                                           | <ul> <li>The cycle time is 4 times n times the f1 period. (n:1)</li> <li>The divider circuit outputs (ø1 through ø15) are used as the clock time base, the LCD drive frequency generation clock, and for S/K port chattering prevention.</li> </ul>                                                                                  |

| Xtal<br>• 32 kHz<br>• 55 kHz | CFIN<br>CFOUT<br>CFOUT<br>CFOUT<br>CFOUT<br>CFOUT<br>STOP<br>UIL<br>T2<br>T3<br>T4<br>HALT<br>HALT<br>UIL<br>UIL<br>T2<br>T3<br>T4<br>HALT | <ul> <li>The cycle time is 4 times the f2 period.</li> <li>The divider circuit outputs (ø1 through ø15) are used as the clock time base, the LCD drive waveform generation clock, and for S/K port chattering prevention.</li> <li>Note that the CFIN and CFOUT pins are switched over to function as the P1 and P2 pins.</li> </ul> |

## **Crystal Oscillator Circuit Options**

| Option                           | Circuit type                                                      | Notes                                                                                                                                                                                                                                                                                                                |

|----------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Used at 32 kHz                   | $\begin{array}{c} & & \\ & & \\ & & \\ & \\ & \\ & \\ & \\ & \\ $ | The resistor RD is built into the IC when this circuit is used at 32 kHz.                                                                                                                                                                                                                                            |

| Used at 38 kHz<br>Used at 65 kHz | Cg XTIN<br>Cg Rf<br>Cd XTOUT<br>Vss                               | <ul> <li>The cycle time is 4 times n times the f1 period. (n:2)</li> <li>The divider circuit outputs (ø1 through ø15) are used as the clock time base, the LCD drive frequency generation clock, and for S/K port chattering prevention.</li> <li>OSC1 is stopped by the execution of a SLOW instruction.</li> </ul> |

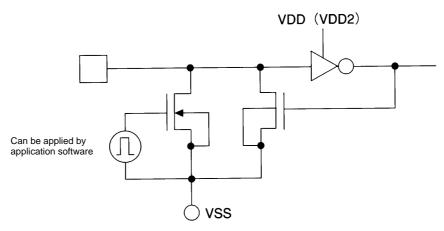

#### **Input Port Options**

#### **RES** Pin

#### **Mask Option List**

Voltage specifications

- Ag specifications

- Li specifications

- EXT-V specifications

#### LCD driver

- Static

- 1/2 bias 1/2 duty

- 1/2 bias 1/3 duty

- 1/2 bias 1/4 duty

- 1/3 bias 1/3 duty

- 1/3 bias 1/4 duty

- Unused

Segment port states during a reset

- LCD driver pins

- All lit

- All off

- CMOS p/n-channel pins

- High level

- Low level

#### Oscillator specifications

- CF only (ceramic oscillator element)

- RC only (using a resistor and a capacitor)

- Crystal only

- CF + crystal

- RC + crystal

#### CF

- 400 kHz

- 800 kHz

- 1 MHz

- 2 MHz

- 4 MHz

#### RC

- 400 kHz

- 800 kHz

- 1 MHz

#### Crystal

- 32 kHz

- 65 kHz

- 38 kHz

#### LCD alternation frequency

- SLOW

- TYP

- FAST

#### External reset circuit

- RES pin

- RES pin + S1 to S4 pressed at the same time

Internal reset circuit (power on reset)

- Selected

- Disabled

#### RES pin

- Reset on low, pull-up resistor included

- Reset on high, pull-down resistor included

- Reset on low, no resistors connected

- · Reset on high, no resistors connected

- Alarm output initial level

- Low level

- High level

#### Chronometer and strobe selection

- 00H

- 10H

- 00H & 10H

- Unused

Port S low level hold transistors

- Low level hold transistors present

- Low level hold transistors disabled

#### Port K low level hold transistors

- · Low level hold transistors present

- Low level hold transistors disabled

#### Port M low level hold transistors

- Low level hold transistors present

- Low level hold transistors disabled

#### Port P low level hold transistors

- · Low level hold transistors present

- Low level hold transistors disabled

#### Port SO low level hold transistors

- Low level hold transistors present

- Low level hold transistors disabled

#### Port A low level hold transistors

- Low level hold transistors present

- Low level hold transistors disabled

#### M1 to M4 outputs

- CMOS

- p-channel

- n-channel

#### P1 to P4 outputs

- CMOS

- p-channel

- n-channel

## A1 to A4 outputs

- CMOS

- p-channel n-channel

These electrical characteristics are provisional and the values are subject to change.

## Ag Specifications

# Absolute Maximum Ratings at Ta = 25 $^{\circ}C$ $\pm 2^{\circ}C,$ $V_{SS}$ = 0 V

| Parameter              | Symbol             | Conditions and applicable pins                                                                       |      | Unit |                         |      |

|------------------------|--------------------|------------------------------------------------------------------------------------------------------|------|------|-------------------------|------|

| Parameter              | Symbol             | Conditions and applicable pins                                                                       | min  | typ  | max                     | Unit |

|                        | V <sub>DD</sub>    |                                                                                                      | -0.3 |      | +4.0                    | V    |

|                        | V <sub>DD</sub> 1  |                                                                                                      | -0.3 |      | +4.0                    | V    |

| Maximum supply voltage | V <sub>DD</sub> 2  |                                                                                                      | -0.3 |      | +5.5                    | V    |

|                        | V <sub>DD</sub> 3  | For 1/3-bias LCD drive techniques                                                                    | -0.3 |      | +4.0                    | V    |

|                        | V <sub>DD</sub> 3  | For LCD drive techniques other than 1/3 bias                                                         | -0.3 |      | +4.0                    | V    |

| Maximum input voltage  | V <sub>IN</sub> 1  | S1 to S4, K1 to K4, M1 to M4, A1 to A4, SO1 to SO4, RES,TST                                          | -0.3 |      | V <sub>DD</sub> + 0.3   | V    |

| Maximum output voltage | V <sub>OUT</sub> 1 | M1 to M4, A1 to A4, SO1 to SO4, ALM, CUP2<br>(With M1 to M4, A1 to A4, and SO1 to SO4 in input mode) | -0.3 |      | +0.3                    | v    |

|                        | V <sub>OUT</sub> 2 | SEGOUT, COM1 to COM4, CUP1                                                                           | -0.3 |      | V <sub>DD</sub> 3 + 0.3 | V    |

| Operating temperature  | Topg               |                                                                                                      | -20  |      | +65                     | °C   |

| Storage temperature    | Tstg               |                                                                                                      | -30  |      | +125                    | °C   |

## Allowable Operating Ranges at $Ta=25^\circ C \pm 2^\circ C, \, V_{SS}=0 \; V$

| Parameter                | Symbol Conditions and applicable pins |                                                                                                                       |                       | Unit |                 |      |

|--------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------|------|

| Falanielei               | Symbol                                |                                                                                                                       | min                   | typ  | max             | Unit |

|                          | V <sub>DD</sub><br>V <sub>DD</sub> 1  | VBAK = V <sub>DD</sub> 1                                                                                              | 1.3                   |      | 1.65            | V    |

| Supply voltage           | V <sub>DD</sub> 2                     |                                                                                                                       | 2.4                   |      | 3.3             | V    |

|                          | V <sub>DD</sub> 3                     | For 1/3-bias LCD drive techniques                                                                                     | 3.7                   |      | 4.95            | V    |

|                          | V <sub>DD</sub> 3                     | For LCD drive techniques other than 1/3 bias                                                                          | 2.4                   |      | 3.3             |      |

| High-level input voltage | VIH                                   | S1 to S4, K1 to K4, M1 to M4, A1 to A4, SO1 to SO4,<br>(With M1 to M4, A1 to A4, and SO1 to SO4 in input mode)<br>RES | V <sub>DD</sub> – 0.2 |      | V <sub>DD</sub> | V    |

| Low-level input voltage  | VIL                                   | S1 to S4, K1 to K4, M1 to M4, A1 to A4, SO1 to SO4,<br>(With M1 to M4, A1 to A4, and SO1 to SO4 in input mode)<br>RES | 0                     |      | 0.2             | V    |

| Operating frequency      | fopg                                  | Ta = −20 to +65°C                                                                                                     | 32                    |      | 33              | kHz  |

# Electrical Characteristics at Ta = 25°C $\pm$ 2°C, V<sub>SS</sub> = 0 V, V<sub>DD</sub> = V<sub>DD</sub>1

| Parameter                 | Cumhal             | Conditions and applicable size                                                                                                                                                                                             |                        | Unit |      |      |

|---------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|------|

| Parameter                 | Symbol             | Conditions and applicable pins                                                                                                                                                                                             | min                    | typ  | max  | Unit |