# LC35256D-10, LC35256DM, DT-70/10

Dual Control Pins:  $\overline{\text{OE}}$  and  $\overline{\text{CE}}$  256K (32768-word  $\times$  8-bit) SRAM

### Overview

The LC35256D, LC35256DM, and LC35256DT are 32768-word  $\times$  8-bit asynchronous silicon gate CMOS static RAMs. These devices use a 6-transistor full CMOS memory cell, and feature low-voltage operation, low current drain, and an ultralow standby current. They provide two control signal inputs: an  $\overline{\text{OE}}$  input for high-speed access and a chip select ( $\overline{\text{CE}}$ ) input for device selection and low power operating mode. This makes these devices optimal for systems that require low power or battery backup, and they allow memory to be expanded easily. Their ultralow standby current allows capacitor-based backup to be used as well. Since they support 3-V operation, they are appropriate for use in portable systems that operate from batteries.

#### **Features**

• Supply voltage range: 2.7 to 5.5 V

— 5-V operation: 5.0 V±10%

— 3-V operation: 2.7 to 3.6 V

- Access times

- 5-V operation

LC35256DM, DT-70: 70 ns (max)

LC35256D, DM, DT-10: 100 ns (max)

— 3-V operation

LC35256DM, DT-70: 200 ns (max) LC35256D, DM, DT-10: 500 ns (max)

• Standby current

— 5-V operation: 1.0  $\mu$ A (Ta ≤ 60°C),

$5.0 \,\mu A \,(Ta \le 85^{\circ}C)$

— 3-V operation: 0.8  $\mu$ A (Ta ≤ 60°C),

$4.0 \,\mu A \,(Ta \le 85^{\circ}C)$

- Operating temperature range: -40 to +85°C

- Data retention supply voltage: 2.0 to 5.5 V

- All I/O levels

- 5-V operation: TTL compatible

- 3-V operation:  $V_{CC} 0.2 \text{ V}/0.2 \text{ V}$

- Shared I/O pins and 3-state outputs

- No clock signal required.

- Packages

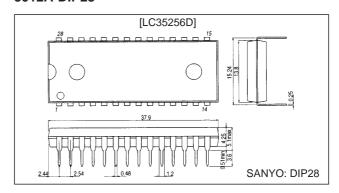

- 28-pin DIP (600 mil) plastic package: LC35256D

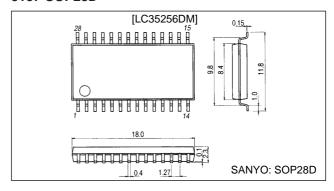

- 28-pin SOP (450 mil) plastic package: LC35256DM

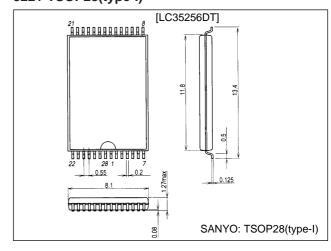

- 28-pin TSOP (8  $\times$  13.4 mm) plastic package: LC35256DT

### **Package Dimensions**

unit: mm

#### 3012A-DIP28

unit: mm

#### 3187-SOP28D

unit: mm

### 3221-TSOP28(type-I)

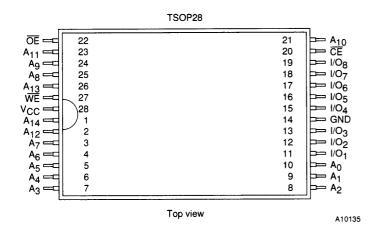

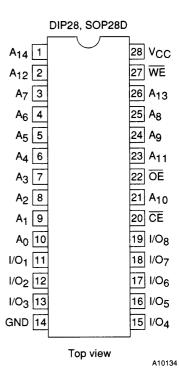

### **Pin Assignment**

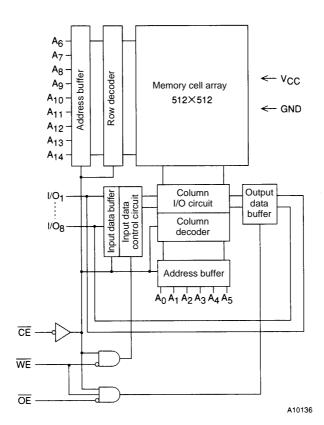

### **Block Diagram**

#### **Pin Functions**

| A0 to A14             | Address inputs           |

|-----------------------|--------------------------|

| WE                    | Read/write control input |

| ŌĒ                    | Output enable input      |

| CE                    | Chip enable input        |

| I/O1 to I/O8          | Data I/O                 |

| V <sub>CC</sub> , GND | Power supply, ground     |

### **Function Table**

| Mode           | CE | ŌE | WE | I/O            | Supply current   |

|----------------|----|----|----|----------------|------------------|

| Read cycle     | L  | L  | Н  | Data output    | I <sub>CCA</sub> |

| Write cycle    | L  | Х  | L  | Data input     | I <sub>CCA</sub> |

| Output disable | L  | Н  | Н  | High-impedance | I <sub>CCA</sub> |

| Unselected     | Н  | Х  | Х  | High-impedance | I <sub>CCS</sub> |

X : H or L

## **Specifications**

### **Absolute Maximum Ratings**

| Parameter              | Symbol              | Conditions | Ratings                        | Unit |

|------------------------|---------------------|------------|--------------------------------|------|

| Maximum supply voltage | V <sub>CC</sub> max |            | 7.0                            | V    |

| Input pin voltage      | V <sub>IN</sub>     |            | -0.3* to V <sub>CC</sub> + 0.3 | V    |

| I/O pin voltage        | V <sub>I/O</sub>    |            | -0.3 to V <sub>CC</sub> + 0.3  | V    |

| Operating temperature  | Topr                |            | -40 to +85                     | °C   |

| Storage temperature    | Tstg                |            | -55 to +125                    | °C   |

Note \*: -3.0 V for pulse widths of up to 30 ns.

### I/O Capacitances at $Ta = 25^{\circ}C$ , f = 1 MHz

| Parameter             | Symbol           | Conditions             |     | Unit |     |       |

|-----------------------|------------------|------------------------|-----|------|-----|-------|

| Falametei             | Symbol           | Conditions             | min | typ  | max | Offic |

| I/O pin capacitance   | C <sub>I/O</sub> | V <sub>I/O</sub> = 0 V |     | 6    | 10  | pF    |

| Input pin capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V  |     | 6    | 10  | pF    |

Note: These parameters are not measured in all units, but rather are only measured in sampled units.

### [5-V Operation]

### DC Allowable Operating Ranges at Ta = -40 to $+85^{\circ}C$ , $V_{CC} = 4.5$ to 5.5 V

| Parameter      | Symbol          | Conditions |       | Unit |                       |       |

|----------------|-----------------|------------|-------|------|-----------------------|-------|

| Farameter      | Symbol          | Conditions | min   | typ  | max                   | Ullit |

| Supply voltage | V <sub>CC</sub> |            | 4.5   | 5.0  | 5.5                   | V     |

| Input voltages | V <sub>IH</sub> |            | 2.2   |      | V <sub>CC</sub> + 0.3 | V     |

| Input voltages | V <sub>IL</sub> |            | -0.3* |      | +0.8                  | V     |

Note \*: -3.0 V for pulse widths of up to 30 ns.

## DC Electrical Characteristics at $Ta = -40~to~+85^{\circ}C,\,V_{CC} = 4.5~to~5.5~V$

| Doro              | Parameter Symbol         |                   | Cond                                                                                              | Conditions                                                                                            |                                    |                      | Ratings |      |      | Unit  |

|-------------------|--------------------------|-------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------|----------------------|---------|------|------|-------|

| Faia              | imetei                   | Symbol            | Cono                                                                                              | 11110115                                                                                              |                                    |                      | min     | typ* | max  | Ullit |

| Input leakage cui | rrent                    | ILI               | V <sub>IN</sub> = 0 to V <sub>CC</sub>                                                            |                                                                                                       |                                    |                      | -1.0    |      | +1.0 | μA    |

| Output leakage of | urrent                   | I <sub>LO</sub>   | $V_{\overline{CE}} = V_{IH} \text{ or } V_{\overline{OE}} = V_{IH} \text{ or } V_{\overline{OE}}$ | ∕ <sub>WE</sub> = V                                                                                   | <sub>IL</sub> , V <sub>I/O</sub> = | 0 to V <sub>CC</sub> | -1.0    |      | +1.0 | μA    |

| High-level output | voltage                  | V <sub>OH</sub>   | I <sub>OH</sub> = -1.0 mA                                                                         |                                                                                                       |                                    |                      | 2.4     |      |      | V     |

| Low-level output  | voltage                  | V <sub>OL</sub>   | I <sub>OL</sub> = 2.0 mA                                                                          |                                                                                                       |                                    |                      |         |      | 0.4  | V     |

|                   |                          | I <sub>CCA2</sub> | $V_{\overline{CE}} = V_{IL}, I_{I/O} = 0 \text{ mA}, V_{IN} =$                                    | = V <sub>IL</sub> , I <sub>I/O</sub> $=$ 0 mA, V <sub>IN</sub> $=$ V <sub>IH</sub> or V <sub>IL</sub> |                                    |                      |         |      | 5.0  | mA    |

| Operating         |                          |                   | ., ,, ,, ,,                                                                                       |                                                                                                       | LC3525                             | 6DM, DT-70           |         | 35   | 40   | mA    |

| current drain     | TTL inputs               | I <sub>CCA3</sub> | $V_{\overline{CE}} = V_{IL}, V_{IN} = V_{IH} \text{ or } V_{IL},$                                 | cycle                                                                                                 | LC35256                            | 6D, DM, DT-10        |         | 25   | 30   | mA    |

|                   |                          |                   | $I_{I/O} = 0$ mA, Duty 100%                                                                       | 1 µs c                                                                                                | ycle                               |                      |         | 3.5  | 6.0  | mA    |

|                   | V 0.2.V/                 |                   | V=>V 0.2V                                                                                         |                                                                                                       |                                    | Ta ≤ 25°C            |         | 0.01 |      | μA    |

| Standby mode      | V <sub>CC</sub> – 0.2 V/ | I <sub>CCS1</sub> | $V_{\overline{CE}} \ge V_{CC} - 0.2 \text{ V},$<br>$V_{IN} = 0 \text{ to } V_{CC}$                |                                                                                                       |                                    | Ta ≤ 60°C            |         |      | 1.0  | μA    |

| current drain     | 0.2 V inputs             |                   | $V_{IN} = 0$ to $V_{CC}$ Ta $\leq 85^{\circ}$ C                                                   |                                                                                                       | Ta ≤ 85°C                          |                      |         | 5.0  | μA   |       |

|                   | TTL inputs               | I <sub>CCS2</sub> | $V_{\overline{CE}} = V_{IH}, V_{IN} = 0 \text{ to } V_{CC}$                                       |                                                                                                       |                                    |                      |         |      | 1.0  | mA    |

Note \*: Reference value at Ta = 25°C, V<sub>CC</sub> = 5 V.

## AC Electrical Characteristics at $Ta~=-40~to~+85^{\circ}C,\,V_{CC}$ = 4.5 to 5.5 V

|                              | AC test conditions |                                                     |  |  |  |  |

|------------------------------|--------------------|-----------------------------------------------------|--|--|--|--|

| Input pulse voltage lev      | el                 | V <sub>IH</sub> = 2.4 V, V <sub>IL</sub> = 0.6 V    |  |  |  |  |

| Input rise and fall time     | 3                  | 5 ns                                                |  |  |  |  |

| Input and output timing      | j level            | 1.5 V                                               |  |  |  |  |

| Output load LC35256DM, DT-70 |                    | One TTL gate + 30 pF (Including jig capacitances.)  |  |  |  |  |

| LC35256D, DM, DT-10          |                    | One TTL gate + 100 pF (Including jig capacitances.) |  |  |  |  |

### **Read Cycle**

|                        |                 | LC35256D, DM, DT |     |     |      |    |  |

|------------------------|-----------------|------------------|-----|-----|------|----|--|

| Parameter              | Symbol          | -7               | '0* | -1  | Unit |    |  |

|                        |                 | min              | max | min | max  |    |  |

| Read cycle time        | t <sub>RC</sub> | 70               |     | 100 |      | ns |  |

| Address access time    | t <sub>AA</sub> |                  | 70  |     | 100  | ns |  |

| CE access time         | t <sub>CA</sub> |                  | 70  |     | 100  | ns |  |

| OE access time         | toA             |                  | 35  |     | 50   | ns |  |

| Output hold time       | tон             | 10               |     | 10  |      | ns |  |

| CE output enable time  | tcoe            | 10               |     | 10  |      | ns |  |

| OE output enable time  | tooe            | 5                |     | 5   |      | ns |  |

| CE output disable time | tcop            |                  | 30  |     | 30   | ns |  |

| OE output disable time | toop            |                  | 25  |     | 25   | ns |  |

Note \*: Specification values for the LC35256DM and LC35256DT.

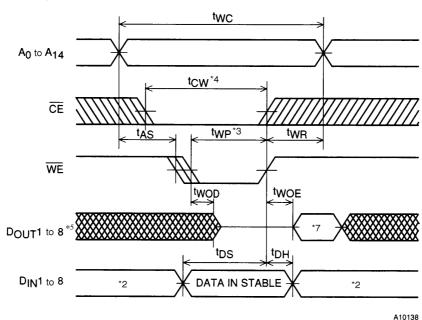

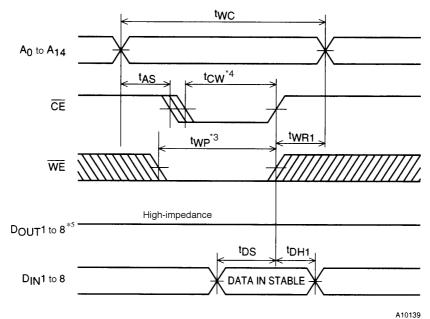

### **Write Cycle**

|                        |                  | LC35256D, DM, DT |     |     |      |    |  |

|------------------------|------------------|------------------|-----|-----|------|----|--|

| Parameter              | Symbol           | -7               | 70* | -1  | Unit |    |  |

|                        |                  | min              | max | min | max  |    |  |

| Write cycle time       | t <sub>WC</sub>  | 70               |     | 100 |      | ns |  |

| Address setup time     | t <sub>AS</sub>  | 0                |     | 0   |      | ns |  |

| Write pulse width      | t <sub>WP</sub>  | 55               |     | 60  |      | ns |  |

| CE setup time          | t <sub>CW</sub>  | 60               |     | 70  |      | ns |  |

| Write recovery time    | t <sub>WR</sub>  | 0                |     | 0   |      | ns |  |

| CE write recovery time | t <sub>WR1</sub> | 0                |     | 0   |      | ns |  |

| Data setup time        | t <sub>DS</sub>  | 35               |     | 40  |      | ns |  |

| Data hold time         | t <sub>DH</sub>  | 0                |     | 0   |      | ns |  |

| CE data hold time      | t <sub>DH1</sub> | 0                |     | 0   |      | ns |  |

| WE output enable time  | twoE             | 5                |     | 5   |      | ns |  |

| WE output disable time | t <sub>WOD</sub> |                  | 30  |     | 30   | ns |  |

Note \*: Specification values for the LC35256DM and LC35256DT.

### [3-V Operation]

## DC Allowable Operating Ranges at $Ta = -40 \ to \ +85^{\circ}C, \ V_{CC} = 2.7 \ to \ 3.6 \ V$

| Parameter      | Symbol          | Conditions |                       | Ratings |                       | Unit  |

|----------------|-----------------|------------|-----------------------|---------|-----------------------|-------|

| Falametei      | Symbol          | Conditions | min                   | typ     | max                   | Offic |

| Supply voltage | V <sub>CC</sub> |            | 2.7                   | 3.0     | 3.6                   | V     |

| Input voltage  | V <sub>IH</sub> |            | V <sub>CC</sub> – 0.2 |         | V <sub>CC</sub> + 0.3 | V     |

| Input voltages | V <sub>IL</sub> |            | -0.3*                 |         | +0.2                  | V     |

Note \*: -2.0 V for pulse widths of up to 30 ns.

### LC35256D-10, LC35256DM, DT-70/10

## DC Electrical Characteristics at $Ta = -40~to~+85^{\circ}C,\,V_{CC}$ = 2.7 to 3.6 V

| Dorr              | ameter                                   | Symbol            | Cono                                                                               | litiono                  |                                      |                       |      | Ratings |       | Unit |

|-------------------|------------------------------------------|-------------------|------------------------------------------------------------------------------------|--------------------------|--------------------------------------|-----------------------|------|---------|-------|------|

| Fair              | ameter                                   | Symbol            | Conc                                                                               | Conditions               |                                      | min                   | typ* | max     | Offic |      |

| Input leakage cu  | rrent                                    | ILI               | V <sub>IN</sub> = 0 to V <sub>CC</sub>                                             |                          |                                      |                       | -1.0 |         | +1.0  | μA   |

| Output leakage    | current                                  | I <sub>LO</sub>   | V <sub>CE</sub> = V <sub>IH</sub> or V <sub>OE</sub> = V <sub>IH</sub> or V        | <u>ME</u> = √            | / <sub>IL</sub> , V <sub>I/O</sub> = | 0 to V <sub>CC</sub>  | -1.0 |         | +1.0  | μA   |

| High-level output | t voltage                                | V <sub>OH</sub>   | I <sub>OH</sub> = -0.5 mA                                                          |                          |                                      | V <sub>CC</sub> – 0.2 |      |         | V     |      |

| Low-level output  | voltage                                  | V <sub>OL</sub>   | I <sub>OL</sub> = 1.0 mA                                                           |                          |                                      |                       |      | 0.2     | V     |      |

| Operating         | V <sub>CC</sub> - 0.2 V/                 |                   | V V V V                                                                            | min                      | LC3525                               | 6DM, DT-70            |      | 7       | 10    | mA   |

| current drain     | 0.2 V inputs                             | I <sub>CCA4</sub> | $V_{\overline{CE}} = V_{IL}, V_{IN} = V_{IH} \text{ or } V_{IL},$                  | TCVCIETECSS2SOD, DIVI. D |                                      | 5D, DM, DT-10         |      | 3       | 5     | mA   |

| current drain     | 0.2 V Inputs                             |                   | $I_{I/O} = 0$ mA, Duty 100%                                                        | 1 µs (                   | cycle                                |                       |      | 1.5     | 2.5   | mA   |

| Standby mode      | V 02V/                                   |                   | V=>V 02V                                                                           |                          |                                      | Ta ≤ 25°C             |      | 0.01    |       | μA   |

| current drain     | V <sub>CC</sub> – 0.2 V/<br>0.2 V inputs | I <sub>CCS1</sub> | $V_{\overline{CE}} \ge V_{CC} - 0.2 \text{ V},$<br>$V_{IN} = 0 \text{ to } V_{CC}$ |                          |                                      | Ta ≤ 60°C             |      |         | 0.8   | μA   |

| current drain     | 0.2 V Inputs                             |                   | VIN = 0 to VCC                                                                     |                          |                                      | Ta ≤ 85°C             |      |         | 4.0   | μA   |

Note \*: Reference value at Ta = 25°C, V<sub>CC</sub> = 3 V.

## AC Electrical Characteristics at $Ta = -40~to~+85^{\circ}C,\,V_{CC}$ = 2.7 to 3.6 V

|                           | AC test conditions |                                                           |  |  |  |  |

|---------------------------|--------------------|-----------------------------------------------------------|--|--|--|--|

| Input pulse voltage leve  | el                 | $V_{IH} = V_{CC} - 0.2 \text{ V}, V_{IL} = 0.2 \text{ V}$ |  |  |  |  |

| Input rise and fall times |                    | 10 ns                                                     |  |  |  |  |

| Input and output timing   | level              | 1.5 V                                                     |  |  |  |  |

| Output load               | LC35256DM, DT-70   | 30 pF (Including jig capacitances.)                       |  |  |  |  |

| LC35256D, DM, DT-10       |                    | 100 pF (Including jig capacitances.)                      |  |  |  |  |

### **Read Cycle**

|                        | Symbol           | LC35256D, DM, DT |     |     |     |      |

|------------------------|------------------|------------------|-----|-----|-----|------|

| Parameter              |                  | -70*             |     | -10 |     | Unit |

|                        |                  | min              | max | min | max |      |

| Read cycle time        | t <sub>RC</sub>  | 200              |     | 500 |     | ns   |

| Address access time    | t <sub>AA</sub>  |                  | 200 |     | 500 | ns   |

| CE access time         | t <sub>CA</sub>  |                  | 200 |     | 500 | ns   |

| OE access time         | t <sub>OA</sub>  |                  | 100 |     | 250 | ns   |

| Output hold time       | tон              | 20               |     | 20  |     | ns   |

| CE output enable time  | t <sub>COE</sub> | 20               |     | 20  |     | ns   |

| OE output enable time  | tooe             | 10               |     | 10  |     | ns   |

| CE output disable time | t <sub>COD</sub> |                  | 60  |     | 120 | ns   |

| OE output disable time | t <sub>OOD</sub> |                  | 50  |     | 100 | ns   |

Note \*: Specification values for the LC35256DM and LC35256DT.

### LC35256D-10, LC35256DM, DT-70/10

### **Write Cycle**

|                        | Symbol           | LC35256D, DM, DT |     |     |     |      |

|------------------------|------------------|------------------|-----|-----|-----|------|

| Parameter              |                  | -70*             |     | -10 |     | Unit |

|                        |                  | min              | max | min | max |      |

| Write cycle time       | t <sub>WC</sub>  | 200              |     | 500 |     | ns   |

| Address setup time     | t <sub>AS</sub>  | 0                |     | 0   |     | ns   |

| Write pulse width      | t <sub>WP</sub>  | 140              |     | 200 |     | ns   |

| CE setup time          | t <sub>CW</sub>  | 150              |     | 250 |     | ns   |

| Write recovery time    | t <sub>WR</sub>  | 0                |     | 0   |     | ns   |

| CE write recovery time | t <sub>WR1</sub> | 0                |     | 0   |     | ns   |

| Data setup time        | t <sub>DS</sub>  | 130              |     | 180 |     | ns   |

| Data hold time         | t <sub>DH</sub>  | 0                |     | 0   |     | ns   |

| CE data hold time      | t <sub>DH1</sub> | 0                |     | 0   |     | ns   |

| WE output enable time  | t <sub>WOE</sub> | 10               |     | 10  |     | ns   |

| WE output disable time | t <sub>WOD</sub> |                  | 60  |     | 120 | ns   |

Note \*: Specification values for the LC35256DM and LC35256DT.

### **Timing Charts**

Read Cycle \*1

Write Cycle 1 (WE write) \*6

Write Cycle 2 (CE write) \*6

Notes: 1. Applications must set WE high during the read cycle.

- 2. External circuits in the application  $\underline{\underline{\underline{\underline{n}}}}$  must  $\underline{\underline{\underline{n}}}$  apply reverse phase signals to the  $\underline{\underline{\underline{D}}}$  pins when those pins are in the  $\underline{\underline{\underline{n}}}$  utput state.

- 3. The time t<sub>WP</sub> is the period when  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  are both low. It is defined as the time from the fall of  $\overline{\text{WE}}$  to the rise of  $\overline{\text{CE}}$  or the rise of  $\overline{\text{WE}}$ , whichever occurs first.

- 4. The time t<sub>CW</sub> is the period when  $\overline{CE}$  and  $\overline{WE}$  are both low. It is defined as the time from the fall of  $\overline{CE}$  to the rise of  $\overline{CE}$  or the rise of  $\overline{WE}$ , whichever occurs first.

- 5.  $\underline{\text{The}}$  data outputs (D<sub>OUT</sub>) go to the high-impedance state if any one of the following conditions hold:  $\overline{\text{OE}}$  is high,  $\overline{\text{CE}}$  is high, or  $\overline{\text{WE}}$  is low.

- 6. OE must be held either high or low during the write cycle.

- 7. The  $D_{\mbox{\scriptsize OUT}}$  pins have the same phase as the write cycle write data.

#### **Notes on Circuit Design**

Take the following operations into account when designing circuits that use these products to assure that none of the items in the maximum ratings are exceeded.

- Supply voltage variations and fluctuations

- Manufacturing variations in the electrical characteristics of the electrical components, including semiconductor devices, resistors, and capacitors.

- Ambient temperature

- Variations and fluctuations in the input and clock signals

- Possible application of abnormal pulses

Parameters listed in the allowable operating ranges must never exceed their stipulated ranges.

If input pins to a CMOS IC are left open, through currents may occur in internal circuits to which intermediate potentials are input and result in incorrect circuit operation. Always verify that any unused pins are set up in appropriate states.

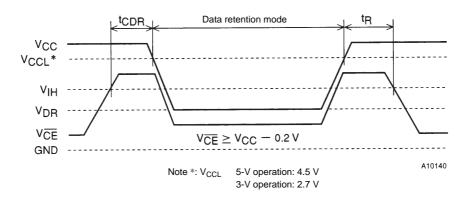

### Data Retention Characteristics at $Ta = -40 \text{ to } +85^{\circ}\text{C}$

| Doromator                     | Cumbal            | Conditions                                                               | Ratings   |                    |      | Unit |    |

|-------------------------------|-------------------|--------------------------------------------------------------------------|-----------|--------------------|------|------|----|

| Parameter                     | Symbol            | Conditions                                                               | min       | typ*1              | max  | Unit |    |

| Data retention supply voltage | V <sub>DR</sub>   | $V_{\overline{CE}} \ge V_{CC} - 0.2 \text{ V}$                           |           | 2.0                |      | 5.5  | V  |

| Data retention current drain  | I <sub>CCDR</sub> | V -30V                                                                   | Ta ≤ 25°C |                    | 0.01 |      | μA |

|                               |                   | $V_{CC} = 3.0 \text{ V},$ $V_{\overline{CE}} \ge V_{CC} - 0.2 \text{ V}$ | Ta ≤ 60°C |                    |      | 0.7  | μA |

|                               |                   |                                                                          | Ta ≤ 85°C |                    |      | 3.5  | μA |

| Chip enable setup time        | t <sub>CDR</sub>  |                                                                          |           | 0                  |      |      | ns |

| Chip enable hold time         | t <sub>R</sub>    |                                                                          |           | t <sub>RC</sub> *2 |      |      | ns |

Notes: 1. Reference value at Ta = 25°C,  $V_{CC}$  = 3 V.

2. t<sub>RC</sub>: Read cycle time

#### **Data Retention Waveforms**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of May, 1998. Specifications and information herein are subject to change without notice.