## 16-Channel Wideband Video Multiplexers

#### **Features**

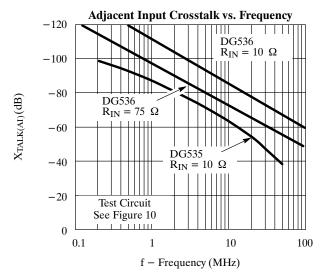

- Crosstalk: −100 dB @ 5 MHz

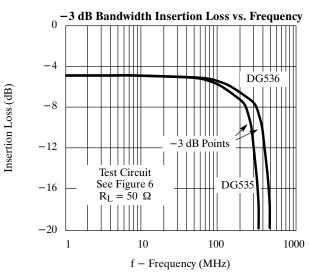

- 300 MHz Bandwidth

- Low Input and Output Capacitance

- Low Power: 75 μW

- Low  $r_{DS(on)}$ : 50  $\Omega$

- On-Board Address Latches

- Disable Output

#### **Benefits**

- High Video Quality

- Reduced Insertion Loss

- Reduced Input Buffer Requirements

- Minimizes Power Consumption

- Simplifies Bus Interface

#### **Applications**

- Video Switching/Routing

- High Speed Data Routing

- RF Signal Multiplexing

- Precision Data Acquisition

- Crosspoint Arrays

- FLIR Systems

#### **Description**

The DG535/536 are 16-channel multiplexers designed for routing one of 16 wideband analog or digital input signals to a single output. They feature low input and output capacitance, low on-resistance, and n-channel DMOS "T" switches, resulting in wide bandwidth, low crosstalk and high "off" isolation. In the on state, the switches pass signals in either direction, allowing them to be used as multiplexers or as demultiplexers.

On-chip address latches and decode logic simplify microprocessor interface. Chip Select and Enable inputs simplify addressing in large matrices. Single-supply operation and a low 75- $\mu$ W power consumption vastly reduces power supply requirements.

Theses devices are built on a proprietary D/CMOS process which creates low-capacitance DMOS FETs and high-speed, low-power CMOS logic on the same substrate.

For more information please refer to Siliconix Application Note AN501.

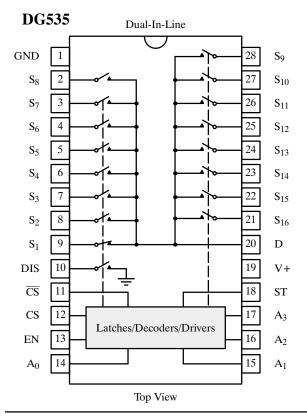

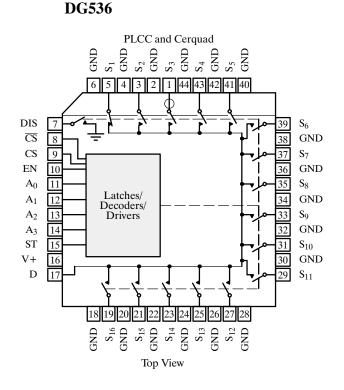

### **Functional Block Diagrams and Pin Configurations**

# **Truth Tables and Ordering Information**

#### **Ordering Information**

| Temp<br>Range | Package               | Part Number |  |  |  |

|---------------|-----------------------|-------------|--|--|--|

| 40.4~ 959.0   | 28-Pin Plastic<br>DIP | DG535DJ     |  |  |  |

| −40 to 85°C   | 28-Pin Sidebraze      | DG535AP     |  |  |  |

|               | 20-1 III Sidebraze    | DG535AP/883 |  |  |  |

| -55 to        | 44-Pin PLCC           | DG536DN     |  |  |  |

| 125°C         | 44-Pin Cerquad        | DG536AM/883 |  |  |  |

#### **Truth Table**

| EN | cs | $\overline{\text{CS}}$ | STa | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Channel<br>Selected                       | Disable <sup>b</sup>  |                |   |   |   |   |   |                |       |

|----|----|------------------------|-----|----------------|----------------|----------------|----------------|-------------------------------------------|-----------------------|----------------|---|---|---|---|---|----------------|-------|

| 0  | X  | X                      |     |                | X              | Х              | X              | None                                      |                       |                |   |   |   |   |   |                |       |

| X  | 0  | X                      | 1   | X              | High Z         |                |                |                                           |                       |                |   |   |   |   |   |                |       |

| X  | X  | 1                      |     |                |                |                |                |                                           |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 0              | 0              | 0              | 0              | $S_1$                                     |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 0              | 0              | 0              | 1              | $S_2$                                     |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 0              | 0              | 1              | 0              | S <sub>3</sub>                            |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 0              | 0              | 1              | 1              | S <sub>4</sub>                            |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 0              | 1              | 0              | 0              | S <sub>5</sub>                            |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     |                |                | 0              | 1              | 0                                         | 1                     | S <sub>6</sub> |   |   |   |   |   |                |       |

|    |    |                        |     |                | 0              | 1              | 1              | 0                                         | S <sub>7</sub>        |                |   |   |   |   |   |                |       |

| 1  | 1  | 0                      | 1   | 1              | 0              | 1              | 1              | 1                                         | S <sub>8</sub>        | Low Z          |   |   |   |   |   |                |       |

| 1  | 1  | U                      |     | Ů              |                | ľ              | ľ              |                                           | ľ                     | 0              | 1 | 1 | 0 | 0 | 0 | S <sub>9</sub> | LOW Z |

|    |    |                        |     | 1              | 0              | 0              | 1              | S <sub>10</sub>                           |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 1              | 0              | 1              | 0              | S <sub>11</sub>                           |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 1              | 0              | 1              | 1              | S <sub>12</sub>                           |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 1              | 1              | 0              | 0              | S <sub>13</sub>                           |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 1              | 1              | 0              | 1              | S <sub>14</sub>                           |                       |                |   |   |   |   |   |                |       |

|    |    |                        | İ   | 1              | 1              | 1              | 0              | S <sub>15</sub>                           |                       |                |   |   |   |   |   |                |       |

|    |    |                        |     | 1              | 1              | 1              | 1              | S <sub>16</sub>                           |                       |                |   |   |   |   |   |                |       |

| X  | X  | X                      | 0   | X              | X              | X              | X              | Maintains<br>previous switch<br>condition | High Z<br>or<br>Low Z |                |   |   |   |   |   |                |       |

Logic "0" =  $V_{AL} \le 4.5 \text{ V}$ Logic "1" =  $V_{AH} \ge 10.5 \text{ V}$

#### Notes:

- a. Strobe input (ST) is level triggered.

- Low Z, High Z = impedance of Disable Output to GND. Disable output sinks current when any channel is selected.

# **Absolute Maximum Ratings**

| V+ to GND                   | 0.3 V to +18 V                           |

|-----------------------------|------------------------------------------|

| Digital Inputs              | . $(GND - 0.3 V)$ to $(V + plus 2 V)$ or |

|                             | 20 mA, whichever occurs first            |

| $V_S, V_D \dots \dots$      | $\dots$ (GND – 0.3 V) to V+ plus 2 V) or |

|                             | 20 mA, whichever occurs first            |

| Current (any terminal) Con  | tinuous 20 mA                            |

| Current (S or D) Pulsed 1 n | ns 10% duty cycle 40 mA                  |

| Storage Temperature (A      | A Suffix)65 to 150°C                     |

| ()                          | D Suffix)65 to 125°C                     |

| Power Dissipation (Package  |                                          |

| 28-Pin Plastic DIPb         | 625 mW                                   |

| 28-Pin Sidebraze <sup>c</sup> | 0 mW |

|-------------------------------|------|

| 44-Pin PLCC <sup>d</sup>      | 0 mW |

| 44-Pin Cerquad <sup>e</sup>   | 5 mW |

- a. All leads soldered or welded to PC board.

- b. Derate 8.6 mW/°C above 75°C.

c. Derate 16 mW/°C above 75°C.

- d. Derate 6 mW/°C above 75°C.

- e. Derate 11 mW/°C above 75°C.

# **TEMIC**

# **Siliconix**

# $Specifications^{a} \\$

|                                             |                              | Test Conditions<br>Unless Otherwise Specified                                                             |            |                   |       | <b>A Suffix</b> −55 to 125°C |            | <b>D Suffix</b><br>-40 to 85°C |             |      |

|---------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|------------|-------------------|-------|------------------------------|------------|--------------------------------|-------------|------|

| Parameter                                   | Symbol                       | V+ = 15 V, ST, CS = 10.5 V<br>$\overline{\text{CS}}$ = 4.5 V, $V_{\text{A}}$ = 4.5 or 10.5 V <sup>f</sup> |            | Temp <sup>b</sup> | Турс  | Min <sup>c</sup>             | Maxc       | Min <sup>c</sup>               | Maxc        | Unit |

| Analog Switch                               |                              |                                                                                                           |            |                   | •     |                              |            |                                |             |      |

| Analog Signal Rangee                        | V <sub>ANALOG</sub>          |                                                                                                           |            | Full              |       | 0                            | 10         | 0                              | 10          | V    |

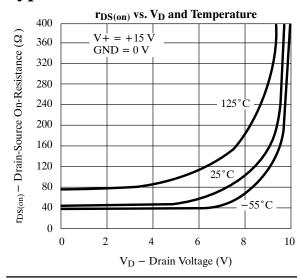

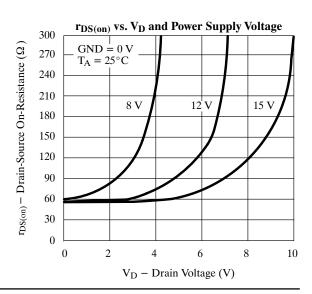

| Drain-Source<br>On-Resistance               | r <sub>DS(on)</sub>          | $I_S = -1 \text{ mA}, V_D = EN = 10.5 \text{ V}$                                                          |            | Room<br>Full      | 55    |                              | 90<br>120  |                                | 90<br>120   | Ω    |

| Resistance Match                            | $\Delta r_{\mathrm{DS(on)}}$ | Sequence Each Swite                                                                                       | Room       |                   |       | 9                            |            | 9                              |             |      |

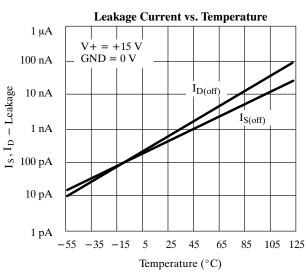

| Source Off<br>Leakage Current               | I <sub>S(off)</sub>          | $V_{S} = 3 \text{ V}, V_{D} = 0 \text{ V}, \text{EN}$                                                     | N = 4.5  V | Room<br>Full      |       | -10<br>-100                  | 10<br>100  | -10<br>-100                    | 10<br>100   |      |

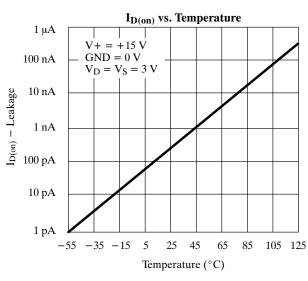

| Drain On<br>Leakage Current                 | $I_{D(on)}$                  | $V_S = V_D = 3 \text{ V}, \text{EN} =$                                                                    | 10.5 V     | Room<br>Full      |       | -10<br>-100<br>0             | 10<br>1000 | -10<br>-100                    | -10<br>-100 | nA   |

| Disable Output                              | R <sub>DISABLE</sub>         | I <sub>DISABLE</sub> = 1 mA, EN                                                                           | = 10.5 V   | Room<br>Full      | 100   |                              | 200<br>250 |                                | 200<br>250  | Ω    |

| Digital Control                             |                              |                                                                                                           |            |                   | •     |                              |            |                                |             |      |

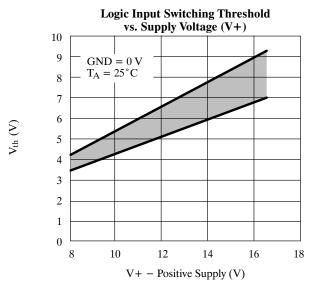

| Input Voltage High                          | $V_{ m AIH}$                 |                                                                                                           |            | Full              |       | 10.5                         |            | 10.5                           |             | V    |

| Input Voltage Low                           | V <sub>AIL</sub>             |                                                                                                           | Full       |                   |       | 4.5                          |            | 4.5                            |             |      |

| Address Input Current                       | $I_{AI}$                     | $V_A = GND \text{ or } V+$                                                                                |            | Room<br>Full      | <0.01 | -1<br>-100                   | 1<br>100   | $-1 \\ -100$                   | 1<br>100    | μΑ   |

| Address Input<br>Capacitance                | $C_{A}$                      |                                                                                                           |            | Full              | 5     |                              |            |                                |             | pF   |

| Dynamic Characteristic                      | es                           |                                                                                                           |            |                   | •     | •                            |            | •                              |             |      |

|                                             |                              |                                                                                                           | PLCC       | Room              | 32    |                              | 45         |                                | 45          |      |

| On State Input<br>Capacitance <sup>e</sup>  | $C_{S(on)}$                  | $V_D = V_S = 3 V$                                                                                         | Cerquad    | Room              | 35    |                              |            |                                |             |      |

|                                             |                              |                                                                                                           | DIP        | Room              | 40    |                              | 55         |                                | 55          | pF   |

| Office a T                                  |                              | $V_S = 3 V$                                                                                               | PLCC       | Room              | 2     |                              | 8          |                                | 8           |      |

| Off State Input<br>Capacitance <sup>e</sup> | $C_{S(off)}$                 |                                                                                                           | Cerquad    | Room              | 5     |                              |            |                                |             |      |

| •                                           |                              |                                                                                                           | DIP        | Room              | 3     |                              |            |                                |             |      |

| Off State Output                            |                              |                                                                                                           | PLCC       | Room              | 8     |                              | 20         |                                | 20          |      |

| Capacitance <sup>e</sup>                    | $C_{D(off)}$                 | $V_D = 3 V$                                                                                               | Cerquad    | Room              | 12    |                              |            |                                |             |      |

|                                             |                              |                                                                                                           | DIP        | Room              | 9     |                              |            |                                |             |      |

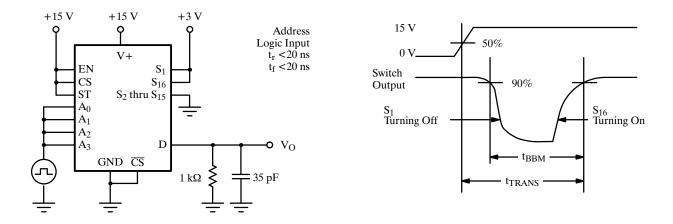

| Multiplexer Switching<br>Time               | t <sub>TRANS</sub>           | See Figure 4                                                                                              |            | Full              |       |                              | 300        |                                | 300         |      |

| Break-Before-Make<br>Interval               | t <sub>OPEN</sub>            | See Figure 4                                                                                              |            | Full              |       | 25                           |            | 25                             |             | ns   |

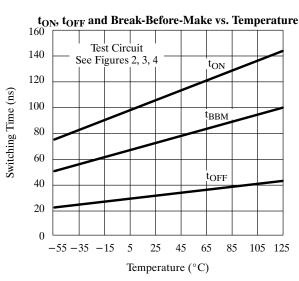

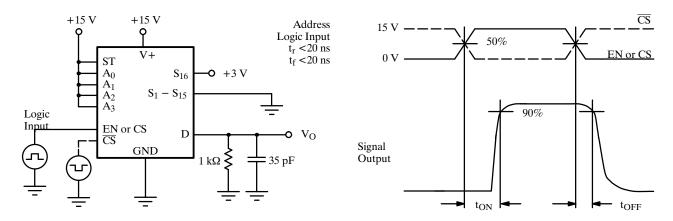

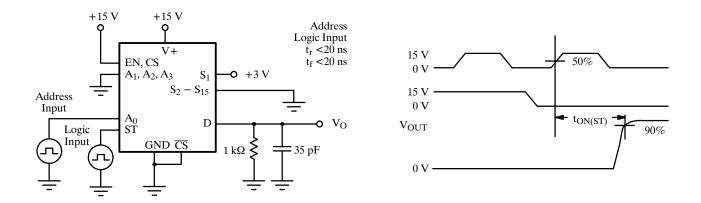

| $EN, CS, \overline{CS}, ST, t_{ON}$         | t <sub>ON</sub>              | See Figure 2 and 3                                                                                        |            | Full              |       |                              | 300        |                                | 300         |      |

| $EN, CS, \overline{CS}, ST, t_{OFF}$        | $t_{ m OFF}$                 | See Figure 2                                                                                              |            | Full              |       |                              | 150        |                                | 150         |      |

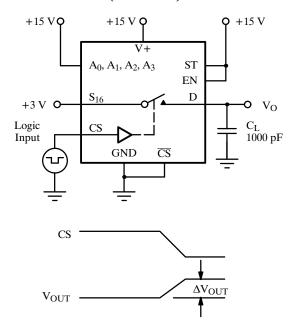

| Charge Injection                            | Q                            | See Figure 5                                                                                              |            | Room              | -35   |                              |            |                                |             | рC   |

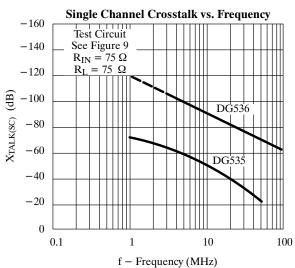

|                                             |                              | $R_{IN} = 75 \Omega,$<br>$R_{I.} = 75 \Omega$                                                             | PLCC       | Room              | -100  |                              |            |                                |             |      |

| Single-Channel Crosstalk                    | X <sub>TALK(SC)</sub>        | f = 5  MHz                                                                                                | Cerquad    | Room              | -93   |                              |            |                                |             |      |

|                                             |                              | See Figure 9                                                                                              | DIP        | Room              | -60   |                              |            |                                |             | dB   |

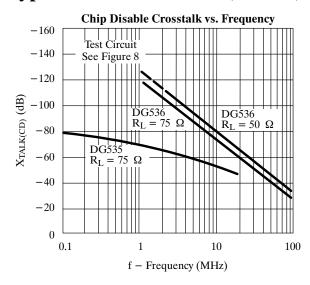

| di pi i i                                   |                              | $R_{IN} = R_L = 75 \Omega$<br>f = 5  MHz,                                                                 | PLCC       | Room              | -85   |                              |            |                                |             |      |

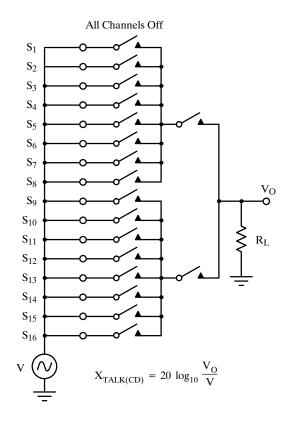

| Chip Disabled Crosstalk                     | X <sub>TALK(CD)</sub>        | EN = 4.5  V                                                                                               | Cerquad    | Room              | -84   |                              |            |                                |             |      |

|                                             |                              | See Figure 8                                                                                              | DIP        | Room              | -60   |                              | I          |                                | I           |      |

| Specification                                                                                                          | s <sup>a</sup>        |                                                                                            |         |              |                              |                  |                             |      |           |     |

|------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|---------|--------------|------------------------------|------------------|-----------------------------|------|-----------|-----|

|                                                                                                                        |                       | Test Condition<br>Unless Otherwise Sp                                                      |         |              | <b>A Suffix</b> −55 to 125°C |                  | <b>D Suffix</b> -40 to 85°C |      |           |     |

| Parameter                                                                                                              | Symbol                | $V + = 15 \text{ V, ST, CS} = \overline{\text{CS}} = 4.5 \text{ V, V}_{A} = 4.5 \text{ o}$ | Tempb   | Турс         | Min <sup>c</sup>             | Max <sup>c</sup> | Min <sup>c</sup>            | Maxc | Unit      |     |

| Dynamic Characteristic                                                                                                 | cs (Cont'd)           |                                                                                            |         |              |                              |                  |                             |      |           |     |

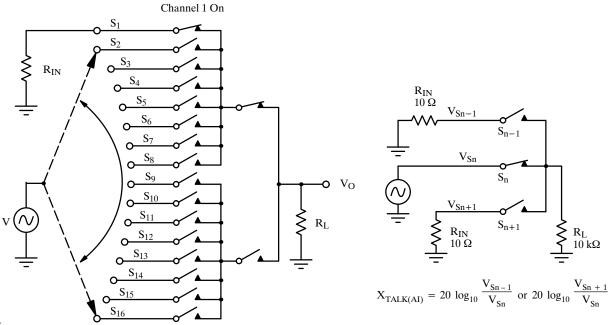

|                                                                                                                        |                       | $R_{IN} = 10 \Omega$ ,                                                                     | PLCC    | Room         | -92                          |                  |                             |      |           |     |

| Adjacent Input Crosstalk                                                                                               | X <sub>TALK(AI)</sub> | $R_L = 10 \text{ k}\Omega,$<br>f = 5  M H z<br>See Figure 10                               | Cerquad | Room         | -87                          |                  |                             |      |           | dB  |

|                                                                                                                        |                       |                                                                                            | DIP     | Room         | -72                          |                  |                             |      |           |     |

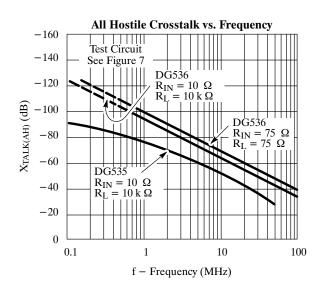

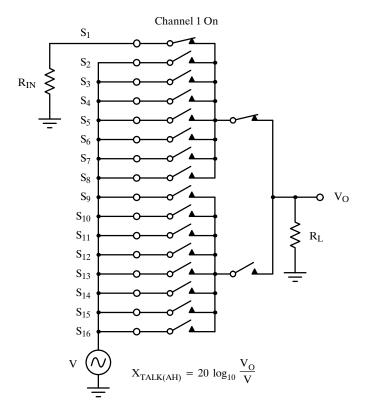

|                                                                                                                        | X <sub>TALK(AH)</sub> | $R_{IN} = 10 \Omega,$ $R_L = 10 k\Omega,$ $f = 5 MHz$ $See \ Figure \ 7$                   | PLCC    | Room         | -74                          | -60              |                             | -60  |           |     |

| All Hostile Crosstalke                                                                                                 |                       |                                                                                            | Cerquad | Room         | -74                          |                  |                             |      |           |     |

|                                                                                                                        |                       |                                                                                            | DIP     | Room         | -60                          |                  |                             |      |           |     |

| Bandwidth                                                                                                              | BW                    | $R_L = 50 \Omega$ , See Figure 6                                                           |         | Room         | 500                          |                  |                             |      |           | MHz |

| <b>Power Supplies</b>                                                                                                  |                       |                                                                                            |         |              |                              |                  |                             |      |           |     |

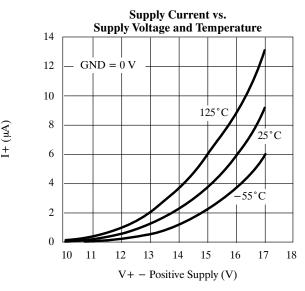

| Positive Supply Current                                                                                                | I+                    | Any One Channgel Selected with All Logic Inputs at GND or V+                               |         | Room<br>Full | 5                            |                  | 50<br>100                   |      | 50<br>100 | μΑ  |

| Supply Voltage Range                                                                                                   | V+                    |                                                                                            |         | Full         |                              | 10               | 16.5                        | 10   | 16.5      | V   |

| Minimum Input Timing                                                                                                   | g Requireme           | nts                                                                                        |         |              |                              |                  |                             |      |           |     |

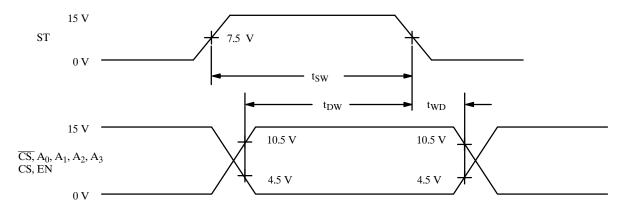

| Strobe Pulse Width                                                                                                     | t <sub>SW</sub>       | See Figure 1                                                                               |         | Full         |                              | 200              |                             | 200  |           |     |

| A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> CS, $\overline{\text{CS}}$ , EN Data Valid to Strobe | t <sub>DW</sub>       |                                                                                            |         | Full         |                              | 100              |                             | 100  |           | ns  |

| A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub> CS, <del>CS</del> ,<br>EN Data Valid after<br>Strobe | $t_{ m WD}$           |                                                                                            |         | Full         |                              | 50               |                             | 50   |           |     |

#### Notes

- a. Refer to PROCESS OPTION FLOWCHART (Section 5 of the 1994 Data Book or FaxBack number 7103).

- b. Room =  $25^{\circ}$ C, Full = as determined by the operating temperature suffix.

- c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- d. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- e. Guaranteed by design, not subject to production test.

- f.  $V_A$  = input voltage to perform proper function.

#### **Typical Characteristics**

#### **Siliconix**

# Typical Characteristics (Cont'd)

### **Typical Characteristics (Cont'd)**

## **Input Timing Requirements**

Figure 1.

#### **Test Circuits**

Figure 2. EN, CS,  $\overline{CS}$ , Turn On/Off Time

Figure 3. Strobe ST Turn On Time

Figure 4. Transition Time and Break-Before-Make Interval

### **Test Circuits (Cont'd)**

$\Delta V_{OUT}$  is the measured voltage error due to charge injection. The charge injection in Coulombs is Q =  $C_L\,x\,\Delta V_{OUT}$

Figure 5. Charge Injection

Figure 7. All Hostile Crosstalk

Figure 6. Bandwidth

Figure 8. Chip Disabled Crosstalk

#### **Siliconix**

# Test Circuits (Cont'd)

Notes:

- 1. Any individual channel between  $S_2 \ \mbox{and} \ S_{16} \ \mbox{can}$  be selected

- 2.  $X_{TALK(SC)} = 20 \log_{10} \frac{V_O}{V}$  is scanned sequentially from  $S_2$  to  $S_{16}$

Figure 9. Single Channel Crosstalk

Figure 10. Adjacent Input Crosstalk

# **Pin Description**

| Symbol                              | Description                                                                                                                   |  |  |  |  |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| S <sub>1</sub> thru S <sub>16</sub> | Analog inputs/outputs                                                                                                         |  |  |  |  |  |  |

| D                                   | Multiplexer output/demultiplexer input                                                                                        |  |  |  |  |  |  |

| DIS                                 | Open drain low impedance to analog ground when any channel is selected                                                        |  |  |  |  |  |  |

| $\overline{\text{CS}}$ , CS, EN     | Logic inputs to selected desired multiplexer(s) when using several multiplexers in a system                                   |  |  |  |  |  |  |

| A <sub>0</sub> thru A <sub>3</sub>  | Binary address inputs to determine which channel is selected                                                                  |  |  |  |  |  |  |

| ST                                  | Strobe input that latches $A_0$ , $A_1$ , $A_2$ , $A_3$ , $\overline{CS}$ , $CS$ , $EN$                                       |  |  |  |  |  |  |

| V+                                  | Positive supply voltage input                                                                                                 |  |  |  |  |  |  |

| GND                                 | Analog signal ground and most negative potential All ground pins should be connected externally to ensure dynamic performance |  |  |  |  |  |  |

#### **Detailed Description**

The DG535/536 are 16-channel single-ended multiplexers with on-chip address logic and control latches.

The multiplexer connects one of sixteen inputs  $(S_1, S_2)$  through  $S_{16}$  to a common output (D) under the control of a 4-bit binary address  $(A_0 \text{ to } A_3)$ . The specific input channel selected for each address is given in the Truth Table.

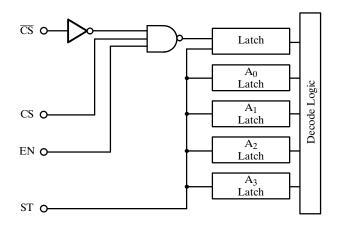

All four address inputs have on-chip data latches which are controlled by the Strobe (ST) input. These latches are transparent when Strobe is high but they maintain the chosen address when Strobe goes low. To facilitate easy microprocessor control in large matrices a choice of three independent logic inputs (EN, CS and  $\overline{CS}$ ) are provided on chip. These inputs are gated together (see Figure 11) and only when EN = CS = 1 and  $\overline{CS}$  = 0 can an output switch be selected. This necessary logic condition is then latched-in when Strobe (ST) goes low

Figure 11. CS, CS, EN, ST Control Logic

Break-before-make switching prevents momentary shorting when changing from one input to another.

The devices feature a two-level switch arrangement whereby two banks of eight switches (first level) are connected via two series switches (second level) to a common DRAIN output.

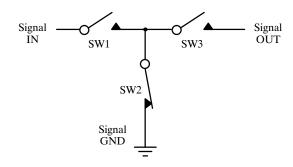

In order to improve crosstalk all sixteen first level switches are configured as "T" switches (see Figure 12).

10

With this method  $SW_2$  operates out of phase with  $SW_1$  and  $SW_3$ . In the on condition  $SW_1$  and  $SW_3$  are closed with  $SW_2$  open whereas in the off condition  $SW_1$  and  $SW_3$  are open and  $SW_2$  closed. In the off condition the input to  $SW_3$  is effectively the isolation leakage of  $SW_1$  working into the on-resistance of  $SW_2$  (typically  $200 \ \Omega$ ).

Figure 12. "T" Switch Arrangement

The two second level series switches further improve crosstalk and help to minimize output capacitance.

The DIS output can be used to signal external circuitry. DIS is a high impedance to GND when no channel is selected and a low impedance to GND when any one channel is selected.

The DG535/536 have extensive applications where any high frequency video or digital signals are switched or routed. Exceptional crosstalk and bandwidth performance is achieved by using n-channel DMOS FETs for the "T" and series switches.

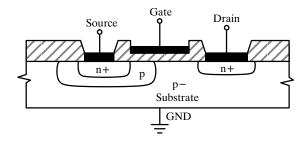

Figure 13. Cross-Section of a Single DMOS Switch

It can clearly be seen from Figure 13 that there exists a PN junction between the substrate and the drain/source terminals.

#### **Detailed Description (Cont'd)**

Should a signal which is negative with respect to the substrate (GND pin) be connected to a source or drain terminal, then the PN junction will become forward biased and current will flow between the signal source and GND. This effective shorting of the signal source to GND will not necessarily cause any damage to the device, provided that the total current flowing is less than the maximum rating, (i.e., 20 mA).

Since no PN junctions exist between the signal path and V+, positive overvoltages are not a problem, unless the breakdown voltage of the DMOS drain terminal (see Figure 13) (+18 V) is exceeded. Positive overvoltage conditions must not exceed +18 V with respect to the GND pin. If this condition is possible (e.g. transients in the signal), then a diode or Zener clamp may be used to prevent breakdown.

The overvoltage conditions described may exist if the supplies are collapsed while a signal is present on the inputs. If this condition is unavoidable, then the necessary steps outlined above should be taken to protect the device

#### **DC** Biasing

To avoid negative overvoltage conditions and subsequent distortion of ac analog signals, dc biasing may be necessary. Biasing is not required, however, in applications where signals are always positive with respect to the GND or substrate connection, or in applications involving multiplexing of low level (up to  $\pm 200$  mV) signals, where forward biasing of the PN substrate-source/drain terminals would not occur.

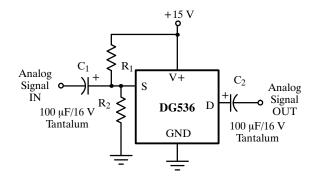

Biasing can be accomplished in a number of ways, the simplest of which is a resistive potential divider and a few dc blocking capacitors as shown in Figure 14.

Figure 14. Simple Bias Circuit

$R_1$  and  $R_2$  are chosen to suit the appropriate biasing requirements. For video applications, approximately 3 V of bias is required for optimal differential gain and phase performance. Capacitor  $C_1$  blocks the dc bias voltage from being coupled back to the analog signal source and  $C_2$  blocks the dc bias from the output signal. Both  $C_1$  and  $C_2$  should be tantalum or ceramic disc type capacitors in order to operate efficiently at high frequencies. Active bias circuits are recommended if rapid switching time between channels is required.

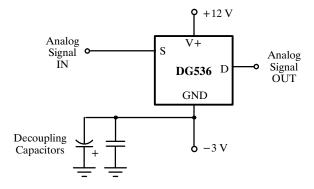

An alternative method is to offset the supply voltages (see Figure 15).

Decoupling would have to be applied to the negative supply to ensure that the substrate is well referenced to signal ground. Again the capacitors should be of a type offering good high frequency characteristics.

Level shifting of the logic signals may be necessary using this offset supply arrangement.

Figure 15. DG536 with Offset Supply

TTL to CMOS level shifting is easily obtained by using a MC14504B.

#### Circuit Layout

Good circuit board layout and extensive shielding is essential for optimizing the high frequency performance of the DG536. Stray capacitances on the PC board and/or connecting leads will considerably degrade the ac performance. Hence, signal paths must be kept as short as practically possible, with extensive ground planes separating signal tracks.