# Low-Noise JFETs — Superior Performance to Bipolars

# Introduction

Junction field effect transistors continue to outperform the best bipolar transistors on low-frequency noise at source impedances as low as 5 k $\Omega$ . With higher source impedances, common in sensitive transducers, the JFET amplifiers exhibit dramatically lower noise figures.

A close examination of bipolar and JFET specification and typical curves, along with circuit breadboarding, will startle most designers.

Many currently available JFET devices offer ultra-low noise performance over a wide range of operating conditions without compromising other desirable JFET features. Recommended applications and part types are described in Table 1.

This application note will review the important noise areas including:

- Considerations in determining noise figure.

- Defining the types of noise.

- Equivalent noise voltage and current.

- Operating point considerations and minimizing noise figure.

- Comparative low frequency performance of JFETs versus bipolars.

- Curves comparing noise current and voltage.

- Source impedance effect on circuit NF.

### **Defining the JFET Noise Figure**

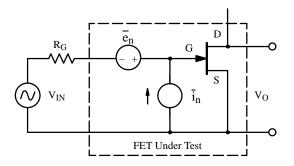

Figure 1 represents the basic circuit identifying the equivalent noise sources  $\overline{e}_n$  and  $\overline{i}_n$  found in a JFET (or bipolar transistor). The  $\overline{e}_n$ -noise voltage referred to the input is independent of source impedance –  $R_G$ . The  $\overline{i}_n$ -noise current effect is directly dependent upon the source impedance –  $R_G$ ; thus  $\overline{i}_n \times R_G$  gives a resulting noise voltage 90 degrees out of phase with  $\overline{e}_n$ .

Figure 1. Equivalent Noise Sources

| General Low-Noise Application           | Metal Can<br>Hermetic | TO-226AA (TO-92)<br>Plastic | TO-236 (SOT-23)<br>Surface Mount |

|-----------------------------------------|-----------------------|-----------------------------|----------------------------------|

| Low current/low voltage amplifier       | 2N4338/2N4339         | J201/J204                   | SST201/SST204                    |

| Medium current ( $\leq$ 5 mA) amplifier | 2N4393                | PN4393                      | SST4393                          |

| High-performance monolithic dual        | U401/U404/U406        | _                           | SST404/SST406                    |

# AN106

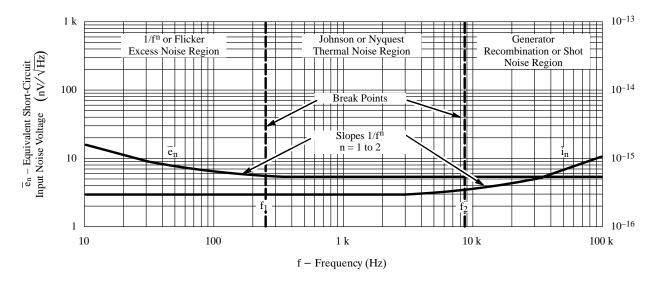

Excess Noise Region – Results from random fluctuations in conductivity and surface effect varying with the reciprocal of frequency and is usually referred to as "1/f" noise. Negligible in low-noise JFETs, it increases approximately 3 dB per octave in bipolars starting below 100 Hz.

Thermal Noise Region - Represents the noise generated in the resistive channel portion of the JFET as identified in equation (1).

Shot Noise Region – Associated with the flow of dc currents in the real part of the gate-to-source device input impedance. The corner frequency is normally above 10 kHz in JFET devices.

Figure 2. Characteristics of Junction FET Noise

#### **Describing Junction FET Noise Characteristic**

Junction FET  $\overline{e}_n$  and  $\overline{i}_n$  characteristics are frequency- dependent within the audio noise spectrum and take the form shown in Figure 2.

$\overline{e}_n$ , the equivalent short circuit input noise voltage (with the exception of the  $1/f^n$  region), is defined as

$$\overline{\mathbf{e}}_{\mathrm{n}} = \sqrt{4k\mathrm{TR}_{\mathrm{N}}\mathbf{B}} \tag{1}$$

where K = 1.38 x 10<sup>-23</sup> Joules/°K (Boltzmann's Constant). T = temperature in °K (°K = °C + 273), B = bandwidth in Hz, and  $R_N \approx 0.67/g_{fs}$ , the equivalent resistance for noise. The  $\bar{e}_n$ , except in the 1/f<sup>n</sup> region, closely approximates the equivalent thermal noise voltage of the channel resistance.

In the so-called  $1/f^n$  region,  $\overline{e}_n$  is expressed as

$$\overline{e}_{n} = \sqrt{4kTR_{N}B (1 + f_{1}/f^{n})}$$

<sup>(2)</sup>

where n varies from 1 to 2 depending upon the device  $i_n$ , the equivalent open-circuit input noise current, with the exception of the shot noise region shown in Figure 2, due

to thermally-generated reverse current in the gate channel junction. It is defined as

$$\bar{i}_n = \sqrt{2 q I_G B}$$

(3)

where  $q = 1.602 \times 10^{-19}$  coulomb (the magnitude of the electron charge), I<sub>G</sub> is the measured dc operating gate current in amperes, and B is bandwidth in Hz. The expression is accurate only when the measured gate current is the result of bulk device conductance. This conductance may stem from contamination across the leads of the semiconductor package.

At higher frequencies, as in the shot noise region shown in Figure 2,  $\overline{i}_n$  can be approximated as being equal to the Nyquist thermal noise current generated by a resistor:

$$\bar{i}_{n} = \sqrt{\frac{4kTB}{R_{p}}}$$

(4)

where  $R_p$  is the real part of the gate-to-source input impedance. The breakpoint or corner frequency  $f_2$  in Figure 2 is lot- and device design-oriented and can vary from 5 kHz to 50 kHz.

# **Defining the JFET Noise Figure**

A noise factor (F) is a figure of merit for a device with respect to the resistance of a generator. To calculate a noise factor, a source resistor,  $R_G$ , with a thermal noise voltage,  $\overline{e_T}$ , is added to the circuit.

A noise factor (F) may be defined as

Noise power output due to  $R_G$  + noise power output due to JFET

or

$$F = 1 + \frac{\text{Noise power of FET referred to input}}{\text{Noise power output due to } R_G}$$

The thermal noise voltage across R<sub>G</sub> is

$$\overline{\mathbf{e}}_{\mathrm{T}} = \sqrt{4\mathrm{k}\mathrm{T}\mathrm{R}_{\mathrm{G}}\mathrm{B}} \tag{6}$$

Therefore, noise power due to R<sub>G</sub> is

$$\frac{\overline{e}_{T}^{2}}{R_{G}} = \frac{4kTR_{G}B}{R_{G}} = 4kTB$$

(7)

The noise power of the FET referred to the input is

$$\frac{\overline{e}_n^2}{R_G} = + \overline{i}_n^2 \cdot R_G$$

(8)

When expressions for the noise power of both the FET and  $R_G$  are substituted, the noise factor becomes

$$F = 1 + \frac{\overline{e}_{n}^{2} + \overline{i}_{n}^{2} R_{G}^{2}}{4kTR_{G}B}$$

(9)

A noise figure (NF) expressed in dB indicates the presence of added noise power from the FET or another active device. The noise figure is always given with reference to a standard, specifically the generator resistance  $R_G$ :

$$NF = 10 \log_{10} [F]$$

(10)

The noise figure of the FET is

NF = 10 log<sub>10</sub>

$$\left[ 1 + \frac{\overline{e}_n^2 + \overline{i}_n^2 R_G^2}{4kTR_G B} \right] dB$$

(11)

When JFET noise is expressed in terms of the noise figure (NF), an inherent disadvantage arises because the noise figure value is dependent upon the value of the generator

resistance,  $R_G$ . Therefore, the  $\overline{e}_n$ ,  $\overline{i}_n$  method remains the best way to quantitatively express the noise characteristics of the FET.

# **Optimized Noise Figure**

(5)

$R_G$  can be chosen to give the lowest noise figure in designs where minimal noise is extremely critical and the source resistance is flexible. This  $R_G$  can be determined by taking the derivative of the terms in Equation (11) with respect to  $R_G$  and setting it equal to zero resulting in

$$R_s = \frac{\overline{e}_n}{\overline{i}_n}$$

for NF min (12)

### **Operating Point Considerations**

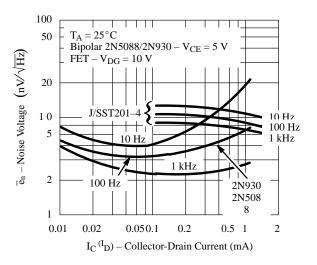

Unlike bipolar transistors, where  $\overline{e}_n$  and  $\overline{i}_n$  characteristics vary directly with changes in the collector current (I<sub>C</sub>), similar characteristics in JFETs will vary only slightly as drain current (I<sub>D</sub>) is varied. This is true as long as the FET is biased so that the drain-source voltage is greater than the pinch-off voltage (V<sub>DS</sub> > V<sub>p</sub> or V<sub>GS(off)</sub>).

The  $\bar{e}_n$  in JFETs will be lowest when the devices are operated at  $V_{GS} = 0$  V ( $I_D = I_{DSS}$ ), where transconductance ( $g_{fs}$ ) is at its highest value. This will be true only if device dissipation is moderate in relation to the total dissipation capability of the FET.

The curves shown in Figure 3 illustrate changes in  $\overline{e}_n$  as the operating drain current (I<sub>D</sub>) is varied. Note the more significant changes in  $\overline{e}_n$  on the bipolar transistors.

Figure 3. Equivalent Input Noise Voltage vs. Current

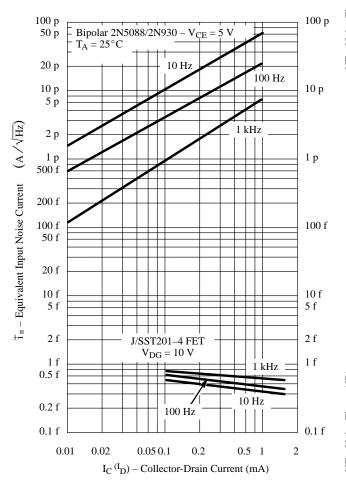

The optimum (lowest)  $\overline{i}_n$  in depletion-mode JFETs should occur at  $V_{GS} = 0$  V ( $I_D = I_{DSS}$ ). In practice, very little change will be seen in  $\overline{i}_n$  when the operating point is changed, provided that the drain-gate voltage is maintained below the gate current ( $I_G$ ) breakpoint and power dissipation is kept at a low level,  $\overline{i}_n$  increases typically only 10% from  $V_{DS} = 5$  to 15 V for the popular low-noise JFETs. Even the typical order of magnitude increase from 15 to 30 V is still far lower than the best bipolar at  $I_C = 10$  µA. The curves shown in Figure 4 illustrate the negligible change versus  $I_D$  for the JFET, while the  $\overline{i}_n$  increases dramatically with increasing  $I_C$  for bipolars.

Figure 4. Equivalent Input Noise Current vs. Current

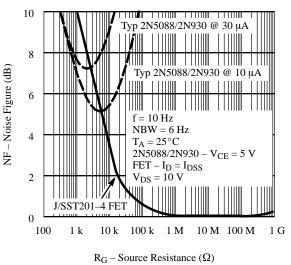

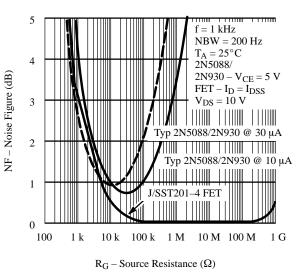

Bipolar collector currents greater than 30  $\mu$ A will have a noise figure much worse with higher R<sub>G</sub> while the JFET noise figure—even with R<sub>G</sub> = 1 GΩ—is well under 1 dB, based upon calculating NF in Equation (11).

Figure 5. Noise Figure vs. Source Resistance @ 10 Hz

# JFET vs. Bipolar Noise Figure

The dramatic noise performance improvement using lownoise JFETs in higher source impedance circuits versus bipolar transistors is clearly illustrated in Figures 5 and 6.

Figure 6. Noise Figure vs. Source Resistance @ 1 kHz

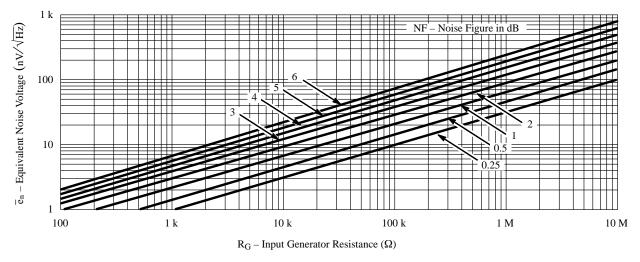

Figure 7. JFET Noise Figure—Noise Voltage Conversion Chart

# **Noise Voltage Conversion**

Practically all JFETs being manufactured today have  $\bar{i}_n$  sufficiently low that it can be neglected for source impedance values up to 10 M $\Omega$ . On this basis, the simplified approximate chart can be used as given in Figure 7.

# **Ideal Low-Noise JFET Applications**

Many currently available JFET devices offer ultra-low noise performance over a wide range of operating conditions without compromising other desirable JFET features. Recommended applications and part types are described in Table 1.

| General<br>Low-Noise<br>Application            | Metal Can<br>Hermetic | TO-226A<br>A (TO-92)<br>Plastic | TO-236<br>(SOT-23)<br>Surface<br>Mount |

|------------------------------------------------|-----------------------|---------------------------------|----------------------------------------|

| Low current/low voltage amplifier              | 2N4338/<br>2N4339     | J201/J204                       | SST201/<br>SST204                      |

| Medium current $(\leq 5 \text{ mA})$ amplifier | 2N4393                | PN4393                          | SST4393                                |

| High-performance monolithic dual               | U401/U404/<br>U406    | _                               | SST404/<br>SST406                      |

Table 1: Recommended Application and Parts

Today's instrumentation and other products require detecting and amplifying extremely low-level signals where noise could "mask" results, and even contribute to a misdiagnosis. In general, sensor output impedance has increased along with sensitivity, making the JFET amplifier the ideal input stage choice.

There are numerous sensors to detect changes in our "analog world." Common JFET amplifier applications in-

clude the input amplifier in high-performance microphones, hearing-aids, sonobuoys, ultrasound, oil exploration, CAT scan, and telemetry equipment. Types of sensors include:

• Meteorological

Mass

• Moisture

Optical

Position

• Pressure

- Acceleration

Level

- Acoustic

- Chemical

- Displacement

- Electrical

- Flow

- Gas/Vapor

- Conclusion

Contemporary JFETs have noise voltages  $(\overline{e}_n)$  equal to those found in low-noise bipolar transistors. The JFET is voltage-actuated, while the bipolar transistor is currentactuated. Hence, FETs have an inherently lower noise current  $(\overline{i}_n)$  and are preferred over bipolar devices in most audio-frequency applications where low-noise performance is a design requirement. The process geometry inherent to the FET governs the noise characteristics of product types derived from it. Readers are invited to refer to the Siliconix FET data sheet curves for full device performance data.

The device  $\overline{e_n}$  typical curves are included in the data sheets, while  $\overline{i_n}$  can be guaranteed at frequencies below 100 Hz by measuring the dc operating gate current (I<sub>G</sub>). When I<sub>G</sub> is known,  $\overline{i_n}$  can be extrapolated from frequencies below 100 Hz to predict noise performance at frequencies to 100 kHz.

- Radioactive Strain Gauges

- Tactile

- Temperature

- Velocity

- Vibration