## M48Z2M1 M48Z2M1Y

# 16 Mb (2Mb x 8) ZEROPOWER<sup>®</sup> SRAM

### DATA BRIEFING

- INTEGRATED LOW POWER SRAM, POWER-FAIL CONTROL CIRCUIT and BATTERIES

- CONVENTIONAL SRAM OPERATION; UNLIMITED WRITE CYCLES

- 10 YEARS of DATA RETENTION in the ABSENCE of POWER

- AUTOMATIC POWER-FAIL CHIP DESELECT and WRITE PROTECTION

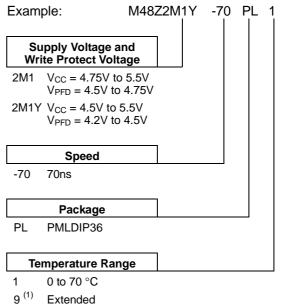

- WRITE PROTECT VOLTAGES (V<sub>PFD</sub> = Power-fail Deselect Voltage):

- M48Z2M1:  $4.5V \le V_{PFD} \le 4.75V$

- M48Z2M1Y:  $4.2V \le V_{PFD} \le 4.50V$

- BATTERIES ARE INTERNALLY ISOLATED UNTIL POWER IS APPLIED

- PIN and FUNCTION COMPATIBLE with JEDEC STANDARD 2Mb x 8 SRAMs

## DESCRIPTION

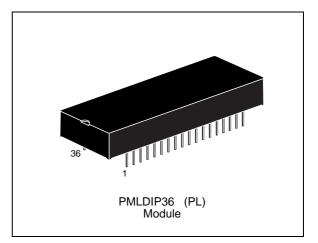

The M48Z2M1/2M1Y ZEROPOWER<sup>®</sup> RAM is a non-volatile 16,777,216 bit Static RAM organized as 2,097,152 words by 8 bits. The device combines two internal lithium batteries, CMOS SRAMs and a control circuit in a plastic 36 pin DIP long Module.

The ZEROPOWER RAM replaces industry standard SRAMs. It provides the nonvolatility of PROMs without any requirement for special write timing or limitations on the number of writes that can be performed.

The M48Z2M1/2M1Y has its own Power-fail Detect Circuit. The control circuitry constantly monitors the single 5V supply for an out of tolerance condition. When  $V_{CC}$  is out of tolerance, the circuit write protects the SRAM, providing a high degree of data security in the midst of unpredictable system operations brought on by low  $V_{CC}$ . As  $V_{CC}$  falls below approximately 3V, the control circuitry connects the batteries which sustain data until valid power returns.

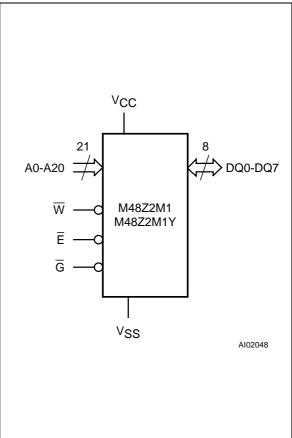

## Logic Diagram

#### B48Z2M1/801

Complete data available on DATA-on-DISC CD-ROM or at www.st.com

## **DIP Pin Connections**

| NC                | 1  | $\cup$   | 36    | lvcc  |

|-------------------|----|----------|-------|-------|

| A20 [             | 2  |          | 35    | A19   |

| A18 [             | 3  |          | 34    | D NC  |

| A16 [             | 4  |          | 33    | ] A15 |

| A14 [             | 5  |          | 32    | ] A17 |

| A12 [             | 6  | M48Z2M1  | 31    | þ₩    |

| A7 [              | 7  |          | 30    | ] A13 |

| A6 [              | 8  |          | 29    | ] A8  |

| A5 [              | 9  | M48Z2M1Y | 28    | ] A9  |

| A4 [              | 10 |          | 27    | DA11  |

| A3 [              | 11 |          | 26    | ₫Ġ    |

| A2 [              | 12 |          | 25    | ] A10 |

| A1 [              | 13 |          | 24    | þē    |

| A0 [              | 14 |          | 23    | DQ7   |

| DQ0 [             | 15 |          | 22    | DQ6   |

| DQ1 [             | 16 |          | 21    | ] DQ5 |

| DQ2 [             | 17 |          | 20    | DQ4   |

| V <sub>SS</sub> [ | 18 |          | 19    | DQ3   |

|                   |    | Ald      | 02049 | )     |

|                   |    |          |       |       |

|                   |    |          |       |       |

## Warning: NC = Not Connected.

## **Signal Names**

| A0-A20          | Address Inputs        |  |

|-----------------|-----------------------|--|

| DQ0-DQ7         | Data Inputs / Outputs |  |

| Ē               | Chip Enable           |  |

| G               | Output Enable         |  |

| W               | Write Enable          |  |

| Vcc             | Supply Voltage        |  |

| V <sub>SS</sub> | Ground                |  |

## **Ordering Information Scheme**

For a list of available options or for further information on any aspect of this device, please contact the SGS-THOMSON Sales Office nearest to you.

Temperature

Note: 1. Contact Sales Offices for availability of Extended Temperature.