=AIRCHILD

Application Note

September 1993

AN-7512

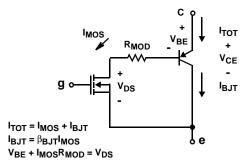

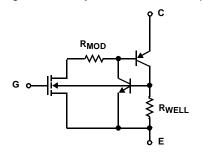

In the November issue of Powertechnics, the general considerations of paralleling semiconductor switches were presented. Some of the important factors include the characteristics of different types of load reactances and the action of the switching device during its turn-on delay, rise time and turn-off delay times. Different types of switching devices must be handled differently when operated in parallel. Power bipolar transistors, SCRs, MOSFETs and IGTs all have different characteristics which must be taken into consideration. The IGT transistor combines the high input impedance, voltage controlled turn on/turn off capabilities of power MOSFETs and the low on-state conduction losses of bipolar transistors. Like MOSFETs, the output characteristics of IGTs are generated by plotting collector-emitter current, collector-emitter voltage and gate voltage. Unlike the MOS-FET, there is an offset voltage generated by the collectoremitter junction of the npn transistor. However, once this offset is overcome, the effective on-resistance in the saturation region is much lower for the IGT than for the MOSFET. A steady state equivalent circuit is shown in Figure 1. Total device current equals MOSFET current (I<sub>MOS</sub>) plus bipolar current (I<sub>BIT</sub>) and since the MOSFET current is the base current of the pnp, these current components are related by the gain of the pnp.

# FIGURE 1. N-CHANNEL IGT TRANSISTOR STEADY STATE EQUIVALENT CIRCUIT

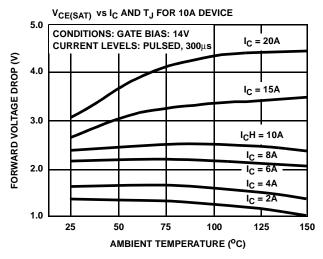

To understand the unusual behavior of its temperature coefficient, negative at low current, almost zero at normal current, and positive at high current, we analyzed the IGT by treating the two branch currents comprising the conduction path as two separated devices. The IGT's on-state voltage drop is composed of the MOSFET voltage drop plus the bipolar V<sub>BE</sub> drop apparently parallel by a pnp-transistor. Note that the only part of the bipolar in parallel to the MOSFET and modulation resistance is the base-collector junction, but the base-emitter junction is common to both branches.

We also know from measurements, the MOSFET's temperature coefficient in the epi-resistance is positive. We know further that as the device temperature increases, the bipolar transistor's gain increases, the V<sub>BE</sub> drop decreases, which both tend to reduce on-voltage drop. On the other hand, the MOSFET and epi-resistance voltage drop will increase with temperature, tending to increase on-voltage voltage.

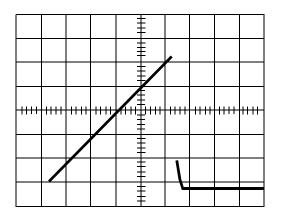

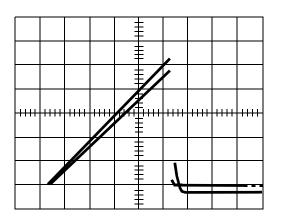

These effects cancel and the net result is that the IGT exhibits much less variation of on-voltage voltage with temperature than either bipolars or MOSFETs. The temperature coefficient goes from a bipolar like negative (at low currents) to zero (at rated current) and to a MOSFET-like positive coefficient as current density increases (Figure 2).

FIGURE 2. V<sub>CE</sub> vs T<sub>A</sub> OF IGT, AT DIFFERENT COLLECTOR CURRENT

### **Turn-On Switching Performance**

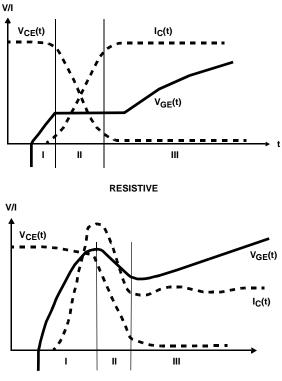

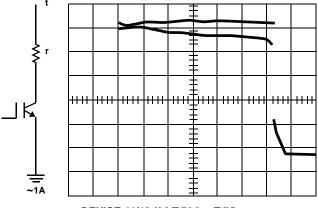

Like the MOSFET, the IGT gate presents a capacitive load to the drive circuit. The IGT capacitive elements and their typical variation with voltage is analogous to the MOSFET, hence the IGT turn-on interval can be divided into three distinct regions (refer to Figure 3). In region I, the input capacitance is charged until the gate voltage reaches the value needed to initiate collector current conduction. In region II, turn-on is essentially completed as the collector voltage falls rapidly to the 10% level. The effective capacitance increases dramatically in this region due to the Miller effect. In region III, the collector voltage slowly settles to its saturation level. At the start of Section III, the effective input capacitance remains high because as the collector voltage is driven below the gate voltage, the polarity of the collector gate voltage reverses and CGC increases dramatically. When the collector reaches the saturation voltage level, the gate rises to the gate-emitter supply level (typically 15 volts).

INDUCTIVE WITH DIODE RECOVERY

#### FIGURE 3. IGT TRANSISTOR TURN ON WAVEFORM

### **Turn-Off Switching Performance**

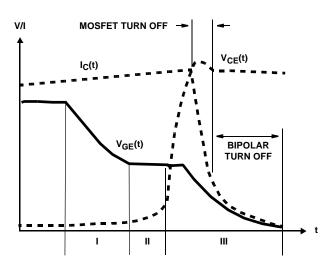

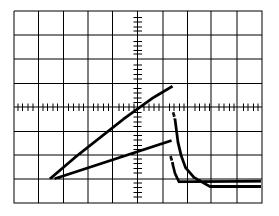

The turn off interval is also composed of three regions as shown in Figure 4 for the case of an inductive load. Region I represents the discharge of the gate to the point where the gate voltage just sustains the collector current.

Region II corresponds to reversing the voltage on  $C_{GC}$  whose value is very high at this point. The gate voltage changes very little during this period and the collector-emitter voltage begins to rise slightly. Taken together, regions I and II represent a turn-off delay. Referring back to the equivalent circuit of Figure 1 when the device is fully on, the MOS-FET voltage prevents the base-collector junction of the pnp from becoming forward biased. Thus the pnp contributes no significant storage time delay during turn off. In region III, the collector voltage rises rapidly at a rate controlled by the amount of current supplied by the gate drive to reverse charge  $C_{GC}$ .

The turn off current fall exhibits two distinct phases: an initial fast drop followed by a slow exponential fall. The initial fast drop is due to the fast cutoff of the MOSFET current. After the MOSFET channel cuts off, the pnp transistor undergoes an open base turn off. The gate drive circuit only controls the initial turn off delay and the slope of the MOSFET current fall by how fast it withdraws gate charge. The pnp exponential turn off tail is a characteristic of the device design.

FIGURE 4. IGT TRANSISTOR TURN OFF WAVEFORMS

### Device Design To Optimize Turn Off

The bipolar current tail was the cause of the excessive switching times of the first-generation IGT. Turn off of the pnp transistor is a function of the stored base charge and the lifetime of carriers in the base region.

Shortening the pnp turn-off time involves decreasing the bipolar current component and/or reducing the carrier lifetime. The carrier recombination rate can be reduced by localized techniques such as electron or proton irradiation. In addition to a faster decay rate, an irradiated device will have a power pnp gain. By decreasing the bipolar current component, the MOSFET current and the amount of initial drop in the turn-off waveform both increase, resulting in a substantially lower current level for the bipolar decay.

### **Turn-Off SOA Optimization**

The dynamic equivalent circuit of the IGT includes a parasitic pnp thyristor (Figure 5). When the sum of the current gains of the npn and pnp exceeds one, the four layer pnp structure latches on and gate control is lost. The npn is effectively shorted by the emitter metal but there is a finite well resistance,  $P_{WELL}$ , below the surface. The npn gain is very low until sufficient current flows through  $P_{WELL}$  to exceed its  $V_{BE}$  threshold. Thus,  $V_{BE(ON)} = (I_{WELL})$  ( $P_{WELL}$ ) provides a latching criteria.

The R<sub>WELL</sub> resistance increases with temperature due to falling carrier mobility in the P<sub>WELL</sub> region. The I<sub>WELL</sub> current is the pnp collector current and hence depends upon the pnp gain. I<sub>WELL</sub> can be increased dramatically by displacement currents from high dv/dt. Increased temperature causes in- creased pnp gain and hence increased I<sub>WELL</sub>. The V<sub>BE(ON)</sub> threshold will decrease with increasing temperature.

Clearly, high-temperature, fast turn-off of an inductive load represents a worse case test. Second generation IGT are SOA limited and not latching-current limited. They will fail due to operation outside the power related current at  $150^{\circ}C$

$\Delta\%$

0%

12%

under the fast ( $R_{GE} = 100\Omega$ ), inductive turn off conditions. This performance has been achieved by minimizing PWELL through cell design and the addition of a deep p+ diffusion and by utilizing the buffer layer structure to lower pnp gain.

### FIGURE 5. DYNAMIC EQUIVALENT CIRCUIT OF THE IGT TRANSISTOR

### **Results Of Paralleling IGT**

From our experience with paralleling devices like bipolars and MOSFETs, there seemed to be no reason why IGTs should not perform reasonably well.

To perform the measurement, we used the IGT-4E10 and the IGT-4E11 both rated at  $I_C = 10A$  at  $T_C = 100^{\circ}C$  and a  $V_{CE} =$ 500V. We also used a 20A device the IGT-6E21.

The parameters we considered important for parallel operation, the saturation voltage  $V_{\mbox{CE}(\mbox{SAT})}$  which we measured at different current levels and a gate voltage VGE = 14V. Gate threshold voltage (V<sub>G(TH)</sub>) which we measured at  $250\mu A$ and 1A (at that level, we can call it an input voltage versus output current) and transconductance (G<sub>ES</sub>).

TABLE 1.

| NO.        | V <sub>CE(SA</sub><br>T)<br>10A | V <sub>G(TH)</sub><br>1A | G <sub>FS</sub> | I           | T <sub>DELAY</sub><br>ON | T <sub>R</sub> | T <sub>DELAY</sub><br>OFF | T <sub>F</sub> |

|------------|---------------------------------|--------------------------|-----------------|-------------|--------------------------|----------------|---------------------------|----------------|

| 44<br>48   | 2.35<br>2.55                    | 5.38<br>5.50             | 4.3<br>3.8      | 10.5<br>9.5 | 51<br>51                 | 225<br>236     | 250<br>230                | 402<br>381     |

| $\Delta$ % | 85%                             | 22%                      | 13%             | 10%         | 0%                       | 4.8%           | 8.6%                      | 5.5%           |

DEVICE 44/48 (2A/DIV 2us/DIV)

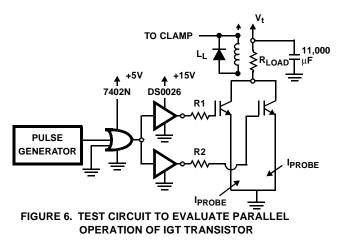

The circuit we used consisted of HP pulse generators 222 and 214A driving a logic gate (7402N) and the memory

driver D50026 connected to the gate through resistors R1 and R<sub>2</sub> to the gate of the IGT, a Tektronix scope 7854 and current probes 6021 and 6302.

Device 44 and 48 were selected as an average combination and deltas of the different parameters can be seen in Table 1. Parallel operation is good, delta I = 1A at 9.5A and 10.5A in each device. We see clearly the FET and bipolar turn off.

The same devices were used to increase the current to about 40A, checking for latching problems, which did not occur.

We then changed the gate resistor from  $50\Omega$  to  $4.7\Omega$  and increased case temperature to the rated 150°C. Still no problems became apparent. Note that the peak current was over four times the rated continuous current.

The same pair was also used to switch on an inductive load (L = 182µH). Excellent parallel operation is achieved with this combination. Even 500ns resolution did not reveal any problems.

The first interesting combination 14 specified  $T_{FMAX}$  = 1µs and 15 specified t<sub>FMAX</sub> = 605µs. The trade-off in switching speed versus V<sub>CE(SAT)</sub> can be seen in Table 2.

| TABLE 2A:                               |                          |                 |                                               |                                                                                          |                       |                                                                                 |                                                                                                   |  |  |

|-----------------------------------------|--------------------------|-----------------|-----------------------------------------------|------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| V <sub>CE(SA</sub><br>T) <sup>10A</sup> | V <sub>G(TH)</sub><br>1A | G <sub>FS</sub> | I                                             | T <sub>DELAY</sub><br>ON                                                                 | T <sub>R</sub>        | T <sub>DELAY</sub><br>OFF                                                       | Τ <sub>F</sub>                                                                                    |  |  |

| 2.15<br>2.15                            | 5.55<br>4.95             | 4.7<br>4.3      | 10.2<br>9.8                                   | 58<br>46                                                                                 | 244<br>252            | 277<br>269                                                                      | 835<br>871                                                                                        |  |  |

|                                         | ,<br>2.15                | 2.15 5.55       | VCE(SA<br>T) VG(TH)<br>1A GFS   2.15 5.55 4.7 | V <sub>CE(SA</sub><br>T) V <sub>G(TH)</sub><br>1A G <sub>FS</sub> I   2.15 5.55 4.7 10.2 | 2.15 5.55 4.7 10.2 58 | VCE(SA<br>T) 10A VG(TH)<br>1A GFS I TDELAY<br>ON TR   2.15 5.55 4.7 10.2 58 244 | VCE(SA<br>T) 10A VG(TH)<br>1A GFS I TDELAY<br>ON TR TDELAY<br>OFF   2.15 5.55 4.7 10.2 58 244 277 |  |  |

4%

9%

TABIE 24

### DEVICE 14/15 60% DIFFERENCE $\approx$ V\_CE(SAT) AND LARGE **DIFFERENCE IN SWITCHING TIME**

Excellent parallel operation is achieved with this combination, even the 500ns resolution does not reveal any problems.

Device 20 having the lower  $V_{\mbox{CE}(\mbox{SAT})}$  and lower  $V_{\mbox{G}(\mbox{TH})}$  is taking the higher share of current. Both parameters V<sub>CE(SAT)</sub> and V<sub>G(TH)</sub> are important in the overall performance. Turn off showing is excellent, but the 500ns time scale shows the result of the difference in the tDFLAY off, of

2.9%

4.3%

23ns and the difference in device 15 and 16, are the devices having low  $V_{CE(SAT)}$  and long turn off times. If paralleled with the proper device (same type), excellent parallel operation is achieved.

| ΤА | BL | E | 2B. |  |

|----|----|---|-----|--|

|    |    | _ |     |  |

| NO.        | V <sub>CE(SA</sub><br>T)<br>10A | V <sub>G(TH)</sub><br>1A | G <sub>FS</sub> | I    | T <sub>DELAY</sub><br>ON | T <sub>R</sub> | T <sub>DELAY</sub><br>OFF | T <sub>F</sub> |

|------------|---------------------------------|--------------------------|-----------------|------|--------------------------|----------------|---------------------------|----------------|

| 14         | 2.25                            | 5.75                     | 4.3             | 6.0  | 53                       | 264            | 246                       | 750            |

| 15         | 1.40                            | 5.35                     | 5.7             | 14.8 | 54                       | 228            | 436                       | 4317           |

| $\Delta$ % | 60%                             | 7%                       | 32%             | 47%  | 1.8%                     | 16%            | 102%                      | 575%           |

CURRENT SHARING OF DEVICE 19/20 (2A/DIV, 5µs/DIV)

Note that 15 paralleled before with the much faster 14 showing extremely poor current sharing.

The 38 and 48 were paralleled to show an inductive load and the recovery current of diode. This is a realistic waveform found in many applications.

Here we paralleled two 20A IGT transistors. Also excellent current showing which is confirmed at the  $500\mu\text{s}/\text{div}$  time scale in.

We paralleled the device 50 and 14 which have a relatively large delta 78% in fall time.

They can be operated in parallel and share much better than we might expect. The large deltas in fall time are the result of the relatively large delta at the current tail in comparison to the rest of the fall time.

| NO.      | V <sub>CE(SA</sub><br>T)<br>10A | V <sub>G(TH)</sub><br>1A | G <sub>FS</sub> | I           | T <sub>DELAY</sub><br>ON | T <sub>R</sub> | T <sub>DELAY</sub><br>OFF | T <sub>F</sub> |

|----------|---------------------------------|--------------------------|-----------------|-------------|--------------------------|----------------|---------------------------|----------------|

| 14<br>15 | 2.25<br>2.15                    | 5.75<br>4.95             | 4.3<br>4.3      | 9.2<br>10.4 | 53<br>46                 | 264<br>252     | 246<br>269                | 750<br>871     |

| Δ%       | 5%                              | 16%                      | 0%              | 13%         |                          |                | 9.3%                      | 16%            |

CURRENT SHARING OF DEVICE 14/20 (2A/DIV, 5µs/DIV)

# Conclusion

All the conventional wisdom applied in the past to parallel bipolar type devices and MOSFET type devices can be applied to parallel operation of IGT Transistors.

- 1. V<sub>CE(SAT)</sub> voltage should be compared at rated current and should not exceed approximately 20% difference.

- 2. Gate threshold voltage which we measured and compared is important, but could be replaced by  $V_{GATE}$  vs  $I_C$  at rated current. Maximum differences should not exceed 10-20%.

- Transconductance g<sub>FS</sub> differences are not as critical as assumed and may be ignored.

- 4.  $t_{D(ON)}$  and rise time are important for current sharing when switching resistive or inductive loads with reverse recovery currents at turn on, but tolerances are small, seldom posing a problem. Check FBSOA. Note that the fastest device takes most of the current. Emitter inductors can be inserted.

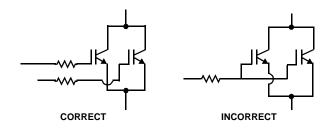

- 5.  $t_{D(OFF)}$  and fall time show also small tolerances, but don't seem to pose a problem. Different device types and different manufacturers should never be paralleled. Note that the slowest device takes most of the current. Removal rate of gate voltage may become a factor. Emitter inductors less than 100µH show excellent results [3].

- Circuit layout should be mechanically and electrically symmetrical. All lead length and differences in lead length become a factor (12-15nH/inch). Separate the gate circuit from the collector circuit (to avoid magnetic coupling).

- Always use separate gate resistor to avoid oscillation. We did not see a problem of rated current but we have not made sufficient measurements to insure no problems.

- 8. Close thermal coupling is recommended (common heatsink) resulting in only small differences in junction temperature.

The IGT's key parameters show relatively close distribution making it difficult to establish exact limits for parallel operation but following the above recommendations will give very good results. Additional measurements were made and in no instances did I exceed 2.5A.

IGT Transistors can be paralleled with a relatively small amount of difficulty. Some current derating may be advisable, which tends to improve current sharing. (We can see on the inductive switching waveform up to 6A sharing is almost perfect.)

In the future, switching modules rated at 100A and 200A or higher having blocking voltages of 500V or 1200V are realistic possibilities.

FIGURE 7. PROBLEM GATE CONNECTION

## References

- SCR Manual, 6th Edition, General Electric Semiconductor Department, Auburn, New York, Chapter 6.2, Parallel Operation of SCR's.

- [2] Use Equations to Parallel Transistors. Otto R. Buhler, IBM, Boulder, Colorado, Electronics Design 4, February 15,1977.

- [3] Parallel Operations of Power Transistors in Switching Applications. Sebald R. Korn, General Electric Company, Application Note 660.39, 10/79.

- [4] Paralleling Switching Bipolar Power Transistors, J. T. Hutchinson, PCIM, September 1985.

- [5] Paralleling High Current Darlingtons, Warren Schulz, Motorola, Phoenix, Arizona, Powertechnics Magazine, December1985.

- [6] Paralleling Power MOSFET's in Switching Applications, by Kim Gauen, Motorola, Application Note AN-918, 1984.

- [7] Parallel Operation of MOSFET's in DC-DC Converters, Rudy Severns, Siliconix, Powertechnics Magazine, June 1985.

- [8] A Chopper for Motor Speed Control Using Parallel Connected Power HEXFET's, by S. Clemente, B. Pelly, IR.

- [9] MOS Power Applications Handbook, Siliconix, Inc., Chapter 5.3, Parallel Operation of Power MOSFET's (TA84-5).

- [10] Motor Control Applications of Second Generation IGT Power Transistors, by Donald J. MacIntyre, Jr., Application Note 200.95.

- [11] Non-destructive Forward Biased Second Breakdown Testing, No. 78-3, by Sebald Korn, Internal General Electric Report.

|                       | V <sub>CE(</sub> | <sub>SAT)</sub> AT V <sub>GE</sub> | = 14V | GATE TH       | RESHOLD | TRANS-<br>CONDUC-<br>TANCE<br>G <sub>FS</sub> | RESIS                    | RESISTIVE      |                           | INDUCTIVE      |  |

|-----------------------|------------------|------------------------------------|-------|---------------|---------|-----------------------------------------------|--------------------------|----------------|---------------------------|----------------|--|

| DEVICE<br>NUMBER      | 2A               | 5A                                 | 10A   | <b>250</b> μΑ | 1A      |                                               | T <sub>DELAY</sub><br>ON | T <sub>R</sub> | T <sub>DELAY</sub><br>OFF | Τ <sub>F</sub> |  |

| TO-3 LOT <sup>2</sup> | 4353             |                                    |       |               |         |                                               |                          |                |                           |                |  |

| 37                    | 1.42V            | 1.82V                              | 2.30  | 3.60V         | 5.50    | 4.3                                           | 51ns                     | 230ns          | 23ns                      | 390            |  |

| 38                    | 1.54             | 2.05                               | 2.70  | 3.70          | 5.75    | 4.2                                           | 53                       | 253            | 230                       | 427            |  |

| 42                    | 1.4              | 1.78                               | 2.25  | 3.75          | 5.60    | 5.4                                           | 45                       | 223            | 226                       | 421            |  |

| 44                    | 1.42             | 1.82                               | 2.35  | 3.50          | 5.38    | 4.3                                           | 51                       | 225            | 250                       | 402            |  |

| 47                    | 1.50             | 1.98                               | 2.60  | 3.75          | 5.75    | 4.2                                           | 58                       | 238            | 226                       | 422            |  |

| 48                    | 1.49             | 1.94                               | 2.55  | 3.50          | 5.50    | 3.8                                           | 51                       | 236            | 230                       | 381            |  |

| 50                    | 1.45             | 1.87                               | 2.40  | 3.62          | 5.60    | 4.4                                           | 58                       | 232            | 240                       | 389            |  |

| $\Delta MAX$          |                  |                                    | 0.45  |               | 0.25    | 1.6                                           |                          |                |                           |                |  |

|                       |                  | -                                  |       |               | -       |                                               |                          |                |                           |                |  |

|                       | V <sub>CE(</sub> | <sub>SAT)</sub> AT V <sub>GE</sub> | = 14V | GATE TH       | RESHOLD | TRANS-<br>CONDUC-                             | RESIS                    | STIVE          | INDUC                     | CTIVE          |  |

| DEVICE<br>NUMBER      | 2A               | 6A                                 | 10A   | <b>250</b> μΑ | 1A      | TANCE<br>G <sub>FS</sub>                      | T <sub>DELAY</sub><br>ON | T <sub>R</sub> | T <sub>DELAY</sub><br>OFF | Τ <sub>F</sub> |  |

| TO-3 LOT <sup>2</sup> | 4933.1 — I       | GT 6E11                            |       |               |         |                                               |                          |                |                           |                |  |

| 13                    | 1.34             | 1.79                               | 2.13  | 3.70          | 5.90    | 4.7                                           | 55                       | 261            | 277                       | 808            |  |

| 14                    | 1.37             | 1.85                               | 2.25  | 3.94          | 5.75    | 4.4                                           | 53                       | 264            | 246                       | 750            |  |

| 19                    | 1.32             | 1.78                               | 2.15  | 3.75          | 5.55    | 4.7                                           | 58                       | 244            | 277                       | 835            |  |

| 20                    | 1.30             | 1.78                               | 2.15  | 3.10          | 4.95    | 4.3                                           | 46                       | 252            | 269                       | 871            |  |

| Δ                     |                  |                                    | 0.18  |               | 0.8     | 0.4                                           |                          |                |                           |                |  |

| TO-3 LOT (            | X) — IGT 6       | E10                                |       |               | 1       |                                               |                          |                |                           |                |  |

|                       |                  |                                    |       |               |         |                                               |                          |                |                           |                |  |

### TABLE 4. RESULTS OF PARALLELING IGT TRANSISTORS

0.95

0.96

15

16

1.20

1.21

1.40

1.42

4.00

3.95

5.35

5.30

5.7

5.7

228

227

54

58

496

515

4317

4190

### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEx™ Bottomless™ CoolFET™ CROSSVOLT™ DenseTrench™ DOME™ **EcoSPARK™** E<sup>2</sup>CMOS<sup>™</sup> EnSigna™ FACT™ FACT Quiet Series<sup>™</sup> MicroPak<sup>™</sup>

FAST ® FASTr™ FRFET™ GlobalOptoisolator™ GTO™ HiSeC™ I<sup>2</sup>C<sup>™</sup> **ISOPLANAR™** LittleFET™ MicroFET™

MICROWIRE™ OPTOLOGIC<sup>®</sup> **OPTOPLANAR™** PACMAN™ POP™ Power247™ PowerTrench ® QFET™ QS™ QT Optoelectronics™ Quiet Series™

SILENT SWITCHER® SMART START™ SPM™ STAR\*POWER™ Stealth™ SuperSOT™-3 SuperSOT™-6 SuperSOT<sup>™</sup>-8 SyncFET™ TinyLogic™ TruTranslation<sup>™</sup>

UHC™ UltraFET® VCX™

### STAR\*POWER is used under license

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY. FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

Definition of Terms

| Product Status            | Definition                                                                                                                                                                                                                        |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Formative or<br>In Design | This datasheet contains the design specifications for<br>product development. Specifications may change in<br>any manner without notice.                                                                                          |

| First Production          | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| Full Production           | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Not In Production         | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |

|                           | Formative or<br>In Design<br>First Production<br>Full Production                                                                                                                                                                  |