# ADC10061/ADC10062/ADC10064 10-Bit 600 ns A/D Converter with Input Multiplexer and Sample/Hold

#### **General Description**

Using an innovative, patented multistep\* conversion technique, the 10-bit ADC10061, ADC10062, and ADC10064 CMOS analog-to-digital converters offer sub-microsecond conversion times yet dissipate a maximum of only 235 mW. The ADC10061, ADC10062, and ADC10064 perform a 10-bit conversion in two lower-resolution "flashes", thus yielding a fast A/D without the cost, power dissipation, and other problems associated with true flash approaches. The ADC10061 is pin-compatible with the ADC1061 but much faster, thus providing a convenient upgrade path for the ADC1061.

The analog input voltage to the ADC10061, ADC10062, and ADC10064 is sampled and held by an internal sampling circuit. Input signals at frequencies from dc to over 200 kHz can therefore be digitized accurately without the need for an external sample-and-hold circuit.

The ADC10062 and ADC10064 include a "speed-up" pin. Connecting an external resistor between this pin and ground reduces the typical conversion time to as little as 350 ns with only a small increase in linearity error.

For ease of interface to microprocessors, the ADC10061, ADC10062, and ADC10064 have been designed to appear as a memory location or I/O port without the need for external interface logic.

\*U.S. Patent Number 4918449

#### **Features**

- Built-in sample-and-hold

- Single +5V supply

- 1, 2, or 4-input multiplexer options

- No external clock required

- Speed adjust pin for faster conversions (ADC10062 and ADC10064). See ADC10662/4 for high speed quaranteed performance.

#### **Key Specifications**

■ Conversion time to 10 bits 600 ns typical,

■ 900 ns max over temperature

■ Sampling Rate 800 kHz

■ Low power dissipation 235 mW (max)

■ Total unadjusted error ±1.0 LSB (max)

■ No missing codes over temperature

#### **Applications**

- Digital signal processor front ends

- Instrumentation

- Disk drives

- Mobile telecommunications

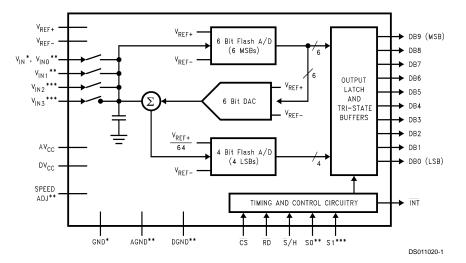

## **Simplified Block Diagram**

- \*ADC10061 Only

- \*\*ADC10062 and ADC10064 Only

- \*\*\*ADC10064 Only

# **Ordering Information**

| Industrial (-40°C ≤ T <sub>A</sub> ≤ +85°C) | Package            |

|---------------------------------------------|--------------------|

| ADC10061CIWM                                | M20B Small Outline |

| ADC10062CIWM                                | M24B Small Outline |

| ADC10064CIWM                                | M28B Small Outline |

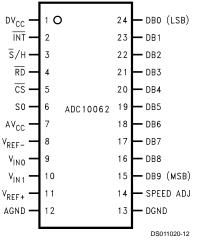

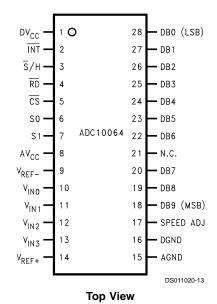

#### **Connection Diagrams**

**Top View**

www.national.com 2

#### **Pin Descriptions**

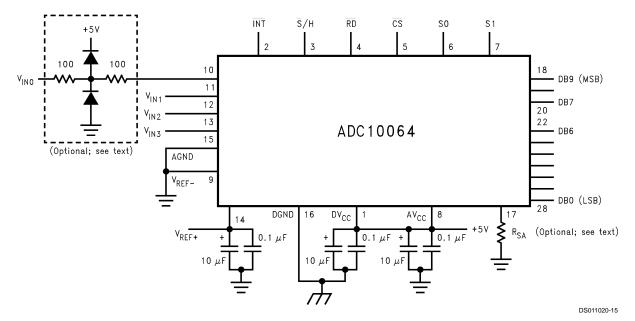

DV<sub>CC</sub>, AV<sub>CC</sub> These are the digital and analog positive supply voltage inputs. They should always be connected to the same voltage source, but are brought out separately to allow for separate bypass capacitors. Each supply pin should be bypassed with a 0.1 µF ceramic capacitor in parallel with a 10 µF tantalum capacitor to

ground.

ĪNT This is the active low interrupt output. INT goes low at the end of each conversion, and returns to a high state following the rising edge

S/H This is the Sample/Hold control input. When this pin is forced low (and  $\overline{CS}$  is low), it causes the analog input signal to be sampled and initiates a new conversion.

$\overline{\mathsf{RD}}$ This is the active low Read control input. When this  $\overline{RD}$  and  $\overline{CS}$  are low, any data present in the output registers will be placed on the data bus.

$\overline{\mathsf{CS}}$ This is the active low Chip Select control input. When low, this pin enables the  $\overline{RD}$  and  $\overline{S}/H$ pins.

S0, S1 On the multiple-input devices (ADC10062 and ADC10064), these pins select the analog input that will be connected to the A/D during the conversion. The input is selected based on the state of S0 and S1 when \$\overline{S}\$/H makes its High-to-Low transition (See the Timing Diagrams). The ADC10064 includes both S0 and S1. The ADC10062 includes just S0, and the ADC10061 includes neither.

These are the reference voltage inputs. They V<sub>REF-</sub>, may be placed at any voltage between GND  $V_{REF+}$ and  $V_{\text{CC}}, \mbox{ but } \mbox{ } V_{\text{REF+}} \mbox{ must be greater than }$

V<sub>REF</sub>. An input voltage equal to V<sub>REF</sub> produces an output code of 0, and an input voltage equal to (V<sub>REF+</sub> - 1 LSB) produces an

output code of 1023.

$V_{IN}, V_{INO},$  $V_{IN1}, V_{IN2},$  $V_{IN3}$

These are the analog input pins. The ADC10061 has one input (V<sub>IN</sub>), the ADC10062 has two inputs  $(V_{IN0}$  and  $V_{IN1})$ , and the ADC10064 has four inputs ( $V_{IN0}$ ,  $V_{IN1}$ ,  $V_{IN2}$ and V<sub>IN3</sub>). The impedance of the source should be less than  $500\Omega$  for best accuracy and conversion speed. For accurate conversions, no input pin (even one that is not selected) should be driven more than 50 mV above V<sub>CC</sub> or 50 mV below ground.

**DGND**

GND, AGND, These are the power supply ground pins. The ADC10061 has a single ground pin (GND), and the ADC10062 and ADC10064 have separate analog and digital ground pins (AGND and DGND) for separate bypassing of the analog and digital supplies. The ground pins should be connected to a stable, noise-free system ground. For the devices with two ground pins, both pins should be returned to the same potential.

DB0-DB9 These are the TRI-STATE® output pins.

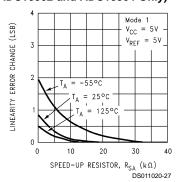

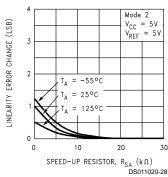

SPEED ADJ (ADC10062 and ADC10064 only). This pin is normally left unconnected, but by connecting a resistor between this pin and ground, the conversion time can be reduced. See the Typical Performance Curves and the table of Electrical Characteristics.

#### Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V^+ = AV_{CC} = DV_{CC}$ ) -0.3V to +6VVoltage at Any Input or Output -0.3V to  $V^+ + 0.3V$ Input Current at Any Pin (Note 3) 5 mA Package Input Current (Note 3) 20 mA Power Dissipation (Note 4) 875 mW ESD Susceptability (Note 5) 2000V Soldering Information (Note 6) Vapor Phase (60 Sec) Infrared (15 Sec) 215°C

Storage Temperature Range -65°C to +150°C Junction Temperature 150°C

#### Operating Ratings (Notes 1, 2)

Temperature Range  $T_{MIN} \le T_A \le T_{MAX}$ ADC10061CIWM, ADC10062CIWM,  $-40^{\circ}C \le T_A \le +85^{\circ}C$ ADC10064CIWM Supply Voltage Range 4.5V to 5.5V

#### **Converter Characteristics**

The following specifications apply for V<sup>+</sup> = +5V,  $V_{REF(+)}$  = +5V,  $V_{REF(-)}$  = GND, and Speed Adjust pin unconnected unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>Min</sub> to T<sub>Max</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = +25°C.

220°C

| Symbol              | Parameter                         | Conditions                                                                                          | Typical<br>(Note 7) | Limit<br>(Note 8)     | Units<br>(Limit) |

|---------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------|

|                     | Resolution                        |                                                                                                     |                     | 10                    | Bits             |

|                     | Integral Linearity Error          | $R_{SA} = 18 \text{ k}\Omega$                                                                       | ±0.5                | ±1.0/ <b>±1.5</b>     | LSB (max)        |

|                     | Offset Error                      |                                                                                                     |                     | ±1                    | LSB (max)        |

|                     | Full-Scale Error                  |                                                                                                     |                     | ±1                    | LSB (max)        |

|                     | Total Unadjusted Error            | All Suffixes, $R_{SA} = 18 \text{ k}\Omega$                                                         | ±0.5                | ±1.5/ <b>±2.0</b>     | LSB (max)        |

|                     | Missing Codes                     |                                                                                                     |                     | 0                     | (max)            |

|                     | Power Supply Sensitivity          | $V^{+} = 5V \pm 5\%, V_{REF} = 4.5V$<br>$V^{+} = 5V \pm 10\%, V_{REF} = 4.5V$                       | ±1/16               | ±3/ <sub>8</sub>      | LSB<br>LSB (max) |

| THD                 | Total Harmonic Distortion         | $f_{IN} = 10 \text{ kHz}, 4.85 \text{ V}_{P-P}$<br>$f_{IN} = 160 \text{ kHz}, 4.85 \text{ V}_{P-P}$ | 0.06<br>0.08        |                       | %<br>%           |

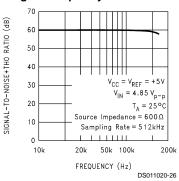

| SNR                 | Signal-to-Noise Ratio             | $f_{IN} = 10 \text{ kHz}, 4.85 \text{ V}_{P-P}$<br>$f_{IN} = 160 \text{ kHz}, 4.85 \text{ V}_{P-P}$ | 61<br>60            |                       | dB<br>dB         |

|                     | Effective Number of Bits          | $f_{IN} = 10 \text{ kHz}, 4.85 \text{ V}_{P-P}$<br>$f_{IN} = 160 \text{ kHz}, 4.85 \text{ V}_{P-P}$ | 9.6<br>9.4          |                       | Bits<br>Bits     |

| R <sub>REF</sub>    | Reference Resistance              |                                                                                                     | 650                 | 400                   | Ω (min)          |

| R <sub>REF</sub>    | Reference Resistance              |                                                                                                     | 650                 | 900                   | Ω (max)          |

| V <sub>REF(+)</sub> | V <sub>REF(+)</sub> Input Voltage |                                                                                                     |                     | V+ + 0.05             | V (max)          |

| V <sub>REF(-)</sub> | V <sub>REF(-)</sub> Input Voltage |                                                                                                     |                     | GND - 0.05            | V (min)          |

| V <sub>REF(+)</sub> | V <sub>REF(+)</sub> Input Voltage |                                                                                                     |                     | V <sub>REF(-)</sub>   | V (min)          |

| V <sub>REF(-)</sub> | V <sub>REF(-)</sub> Input Voltage |                                                                                                     |                     | V <sub>REF(+)</sub>   | V (max)          |

| V <sub>IN</sub>     | Input Voltage                     |                                                                                                     |                     | V <sup>+</sup> + 0.05 | V (max)          |

| V <sub>IN</sub>     | Input Voltage                     |                                                                                                     |                     | GND - 0.05            | V (min)          |

|                     | OFF Channel Input Leakage Current | $\overline{CS} = V^+, V_{IN} = V^+$                                                                 | 0.01                | 3                     | μA (max)         |

|                     | ON Channel Input Leakage Current  | $\overline{CS} = V^+, V_{IN} = V^+$                                                                 | ±1                  | -3                    | μA (max)         |

#### **DC Electrical Characteristics**

The following specifications apply for V<sup>+</sup> = +5V,  $V_{REF(+)}$  = 5V  $V_{REF(-)}$  = GND, and Speed Adjust pin unconnected unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = +25°C.

| Symbol             | Parameter                 | Conditions            | Typical<br>(Note 7) | Limit<br>(Note 8) | Units<br>(Limit) |

|--------------------|---------------------------|-----------------------|---------------------|-------------------|------------------|

| V <sub>IN(1)</sub> | Logical "1" Input Voltage | V <sup>+</sup> = 5.5V |                     | 2.0               | V (min)          |

| V <sub>IN(0)</sub> | Logical "0" Input Voltage | V <sup>+</sup> = 4.5V |                     | 0.8               | V (max)          |

| I <sub>IN(1)</sub> | Logical "1" Input Current | $V_{IN(1)} = 5V$      | 0.005               | 3.0               | μA (max)         |

| I <sub>IN(0)</sub> | Logical "0" Input Current | V <sub>IN(0)</sub> 0V | -0.005              | -3.0              | μA (max)         |

#### DC Electrical Characteristics (Continued)

The following specifications apply for  $V^+ = +5V$ ,  $V_{REF(+)} = 5V$   $V_{REF(-)} = GND$ , and Speed Adjust pin unconnected unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> =  $+25^{\circ}$ C.

| Symbol              | Parameter                       | Conditions                                                                                                           | Typical<br>(Note 7) | Limit<br>(Note 8) | Units<br>(Limit) |

|---------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|------------------|

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage      | $V^{+} = 4.5V$ , $I_{OUT} = -360 \mu A$                                                                              |                     | 2.4               | V (min)          |

|                     |                                 | $V^{+} = 4.5V$ , $I_{OUT} = -10 \mu A$                                                                               |                     | 4.25              | V (min)          |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage      | V <sup>+</sup> = 4.5V, I <sub>OUT</sub> = 1.6 mA                                                                     |                     | 0.4               | V (max)          |

| I <sub>OUT</sub>    | TRI-STATE® Output Current       | V <sub>OUT</sub> = 5V                                                                                                | 0.1                 | 50                | μA (max)         |

|                     |                                 | $V_{OUT} = 0V$                                                                                                       | -0.1                | -50               | μA (max)         |

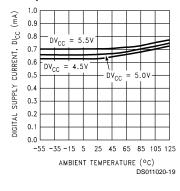

| DI <sub>CC</sub>    | DV <sub>CC</sub> Supply Current | $\overline{\text{CS}} = \overline{\text{S}}/\text{H} = \overline{\text{RD}} = 0, R_{\text{SA}} = \infty$             | 1.0                 | 2                 | mA (max)         |

|                     |                                 | $\overline{\text{CS}} = \overline{\text{S}}/\text{H} = \overline{\text{RD}} = 0, R_{\text{SA}} = 18 \text{ k}\Omega$ | 1.0                 | 2                 | mA (max)         |

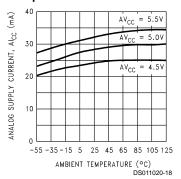

| Al <sub>CC</sub>    | AV <sub>CC</sub> Supply Current | $\overline{\text{CS}} = \overline{\text{S}}/\text{H} = \overline{\text{RD}} = 0, R_{\text{SA}} = \infty$             | 30                  | 45                | mA (max)         |

|                     |                                 | $\overline{\text{CS}} = \overline{\text{S}}/\text{H} = \overline{\text{RD}} = 0, R_{\text{SA}} = 18 \text{ k}\Omega$ | 30                  | 40                | mA (max)         |

#### **AC Electrical Characteristics**

The following specifications apply for V<sup>+</sup> = +5V,  $t_r = t_f = 20$  ns,  $V_{REF(+)} = 5V$ ,  $V_{REF(-)} = GND$ , and Speed Adjust pin unconnected unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = +25°C.

| Symbol                            | Parameter                                                             | Conditions                                           | Typical<br>(Note 7) | Limit<br>(Note 8)     | Units<br>(Limit) |

|-----------------------------------|-----------------------------------------------------------------------|------------------------------------------------------|---------------------|-----------------------|------------------|

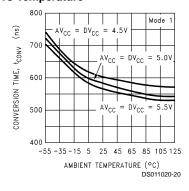

| t <sub>CONV</sub>                 | Mode 1 Conversion Time from Rising Edge of S/H to Falling Edge of INT | $R_{SA} = \infty$ $R_{SA} = 18k$                     | 600<br>375          | 750/ <b>900</b>       | ns(max)<br>ns    |

| t <sub>CRD</sub>                  | Mode 2 Conversion Time                                                | R <sub>SA</sub> = ∞<br>Mode 2, R <sub>SA</sub> = 18k | 850<br>530          | 1400                  | ns(max)<br>ns    |

| t <sub>ACC1</sub>                 | Access Time (Delay from Falling Edge of RD to Output Valid)           | Mode 1; C <sub>L</sub> = 100 pF                      | 30                  | 60                    | ns (max)         |

| t <sub>ACC2</sub>                 | Access Time (Delay from Falling Edge of RD to Output Valid)           | Mode 2; C <sub>L</sub> = 100 pF                      | 900                 | t <sub>CRD</sub> + 50 | ns (max)         |

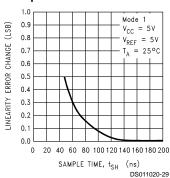

| t <sub>SH</sub>                   | Minimum Sample Time                                                   | (Figure 1); (Note 8)                                 |                     | 250                   | ns (max)         |

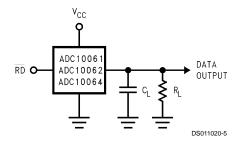

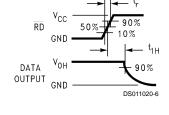

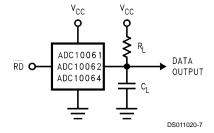

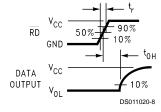

| t <sub>1H</sub> , t <sub>OH</sub> | TRI-STATE Control (Delay from Rising Edge of RD to High-Z State)      | $R_{L} = 1k, C_{L} = 10 pF$                          | 30                  | 60                    | ns (max)         |

| t <sub>INTH</sub>                 | Delay from Rising Edge of RD to Rising Edge of INT                    | C <sub>L</sub> = 100 pF                              | 25                  | 50                    | ns (max)         |

| t <sub>P</sub>                    | Delay from End of Conversion to<br>Next Conversion                    |                                                      |                     | 50                    | ns (max)         |

| t <sub>MS</sub>                   | Multiplexer Control Setup Time                                        |                                                      | 10                  | 75                    | ns (max)         |

| t <sub>MH</sub>                   | Multiplexer Hold Time                                                 |                                                      | 10                  | 40                    | ns (max)         |

| C <sub>VIN</sub>                  | Analog Input Capacitance                                              |                                                      | 35                  |                       | pF (max)         |

| C <sub>OUT</sub>                  | Logic Output Capacitance                                              |                                                      | 5                   |                       | pF (max)         |

| C <sub>IN</sub>                   | Logic Input Capacitance                                               |                                                      | 5                   |                       | pF (max)         |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional. These ratings do not guarantee specific performance limits, however. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply rails  $(V_{IN} \le GND \text{ or } V_{IN} > V^*)$  the absolute value of current at that pin should be limited to 5 mA or less. The 20 mA package input current limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. In most cases, the maximum derated power dissipation will be reached only during fault conditions. For these devices,  $T_{JMAX}$  for a board-mounted device can be found from the tables below:

| Device       | θ <sub>JA</sub> (°C/W) |

|--------------|------------------------|

| ADC10061CIWM | 54                     |

| ADC10062CIWM | 48                     |

| ADC10064CIWM | 44                     |

Note 5: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

#### AC Electrical Characteristics (Continued)

Note 6: See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" or the section titled "Surface Mount" found in a current National Semiconductor Linear Data Book for other methods of soldering surface mount devices.

Note 7: Typicals are at +25°C and represent must likely parametric norm.

Note 8: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 9: Accuracy may degrade if t<sub>SH</sub> is shorter than the value specified. See curves of Accuracy vs t<sub>SH</sub>.

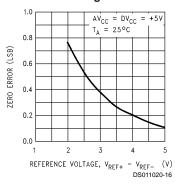

### **Typical Performance Characteristics**

# Zero (Offset) Error vs Reference Voltage

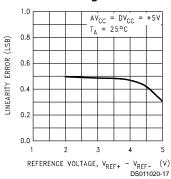

# Linearity Error vs Reference Voltage

# Analog Supply Current vs Temperature

# Digital Supply Current vs Temperature

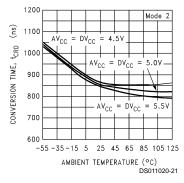

# Conversion Time vs Temperature

# Conversion Time vs Temperature

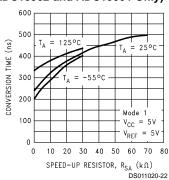

#### Conversion Time vs Speed-Up Resistor (ADC10062 and ADC10064 Only)

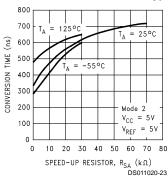

#### Conversion Time vs Speed-Up Resistor (ADC10062 and ADC10064 Only)

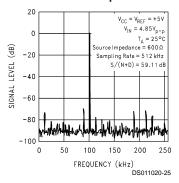

Spectral Response with100 kHz Sine Wave Input

#### **Typical Performance Characteristics (Continued)**

# Spectral Response with 100 kHz Sine Wave Input

# Signal-to-Noise + THD Ratio vs Signal Frequency

#### Linearity Change vs Speed-Up Resistor (ADC10062 and ADC10064 Only)

#### Linearity Change vs Speed-Up Resistor (ADC10062 and ADC10064 Only)

# Linearity Error Change vs Sample Time

#### **TRI-STATE Test Circuits and Waveforms**

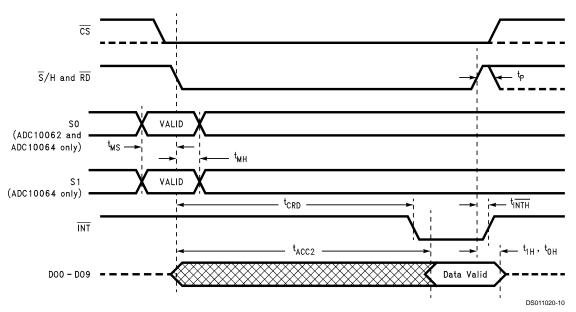

# Timing Diagrams So (ADC10062 and ADC10064 only) (ADC10064 only) VALID VALID VALID VALID VALID VALID

FIGURE 1. Mode 1. The conversion time  $(t_{CONV})$  is set by the internal timer.

t<sub>ACC1</sub> -

tconv

FIGURE 2. Mode 2 ( $\overline{\text{RD}}$  Mode). The conversion time ( $t_{\text{CRD}}$ ) includes the sampling time and is determined by the internal timer.

#### **Functional Description**

RD

INT

DO0 - DO9

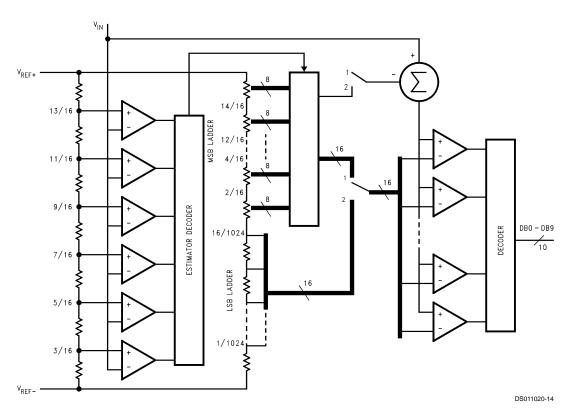

The ADC10061, ADC10062 and ADC10064 digitize an analog input signal to 10 bits accuracy by performing two lower-resolution "flash" conversions. The first flash conversion provides the six most significant bits (MSBs) of data, and the second flash conversion provides the four least significant bits LSBs).

Figure 3 is a simplified block diagram of the converter. Near the center of the diagram is a string of resistors. At the bottom of the string of resistors are 16 resistors, each of which has a value 1/1024 the resistance of the whole resistor string. These lower 16 resistors (the **LSB Ladder**) therefore have a voltage drop of 16/1024, or 1/64 of the total reference voltage ( $V_{REF+} - V_{REF-}$ ) across them. The remainder of the resistor string is made up of eight groups of eight resistors connected in series. These comprise the **MSB Ladder**. Each section of the MSB Ladder has 1/8 of the total reference voltage across it, and each of the LSB resistors has 1/64 of

₹<u>NTH</u>

DS011020-9

#### Functional Description (Continued)

the total reference voltage across it. Tap points across these resistors can be connected, in groups of sixteen, to the sixteen comparators at the right of the diagram.

On the left side of the diagram is a string of seven resistors connected between  $V_{REF+}$  and  $V_{REF-}$ . Six comparators compare the input voltage with the tap voltages on this resistor string to provide a low-resolution "estimate" of the input voltage. This estimate is then used to control the multiplexer that connects the MSB Ladder to the sixteen comparators on the right. Note that the comparators on the left needn't be very accurate; they simply provide an estimate of the input voltage. Only the sixteen comparators on the right and the six on the left are necessary to perform the initial six-bit flash conversion, instead of the 64 comparators that would be required using conventional half-flash methods.

To perform a conversion, the estimator compares the input voltage with the tap voltages on the seven resistors on the left. The estimator decoder then determines which MSB Ladder tap points will be connected to the sixteen comparators on the right. For example, assume that the estimator determines that  $\rm V_{IN}$  is between 11/16 and 13/16 of  $\rm V_{REF}$ . The estimator decoder will instruct the comparator MUX to connect the 16 comparators to the taps on the MSB ladder between 10/16 and 14/16 of  $\rm V_{REF}$ . The 16 comparators will

then perform the first flash conversion. Note that since the comparators are connected to ladder voltages that extend beyond the range indicated by the estimator circuit, errors in the estimator as large as 1/16 of the reference voltage (64 LSBs) will be corrected. This first flash conversion produces the six most significant bits of data—four bits in the flash itself, and 2 bits in the estimator.

The remaining four LSBs are now determined using the same sixteen comparators that were used for the first flash conversion. The MSB Ladder tap voltage just below the input voltage (as determined by the first flash) is subtracted from the input voltage and compared with the tap points on the sixteen LSB Ladder resistors. The result of this second, four-bit flash conversion is then decoded, and the full 10-bit result is latched.

Note that the sixteen comparators used in the first flash conversion are reused for the second flash. Thus, the multistep conversion technique used in the ADC10061, ADC10062, and ADC10064 needs only a small fraction of the number of comparators that would be required for a traditional flash converter, and far fewer than would be used in a conventional half-flash approach. This allows the ADC10061, ADC10062, and ADC10064 to perform high-speed conversions without excessive power drain.

FIGURE 3. Block Diagram of the Multistep Converter Architecture

#### **Applications Information**

#### 1.0 MODES OF OPERATION

The ADC10061, ADC10062, and ADC10064 have two basic digital interface modes. *Figure 1* and *Figure 2* are timing diagrams for the two modes. The ADC10062 and ADC10064

have input multiplexers that are controlled by the logic levels on pins  $S_0$  and  $S_1$  when  $\overline{S}/H$  goes low. *Table 1* is a truth table showing how the input channels are assigned.

#### **Applications Information** (Continued)

#### Mode 1

In this mode, the  $\overline{S}/H$  pin controls the start of conversion.  $\overline{S}/H$  is pulled low for a minimum of 250 ns. This causes the comparators in the "coarse" flash converter to become active. When  $\overline{S}/H$  goes high, the result of the coarse conversion is latched and the "fine" conversion begins. After 600 ns (typical),  $\overline{INT}$  goes low, indicating that the conversion results are latched and can be read by pulling  $\overline{RD}$  low. Note that  $\overline{CS}$  must be low to enable  $\overline{S}/H$  or  $\overline{RD}$ .  $\overline{CS}$  is internally "ANDed" with  $\overline{S}/H$  and  $\overline{RD}$ ; the input voltage is sampled when  $\overline{CS}$  and  $\overline{S}/H$  are low, and data is read when  $\overline{CS}$  and  $\overline{RD}$  are low.  $\overline{INT}$  is reset high on the rising edge of  $\overline{RD}$ .

**TABLE 1. Input Multiplexer Programming**

| ADC10064 (a)   |    |                  |

|----------------|----|------------------|

| S <sub>1</sub> | So | Channel          |

| 0              | 0  | V <sub>INO</sub> |

| 0              | 1  | V <sub>IN1</sub> |

| 1              | 0  | V <sub>IN2</sub> |

| 1              | 1  | V <sub>IN3</sub> |

| ADC10062 (b) |                  |  |

|--------------|------------------|--|

| So           | Channel          |  |

| 0            | V <sub>INO</sub> |  |

| 1            | V <sub>IN1</sub> |  |

#### Mode 2

In Mode 2, also called " $\overline{RD}$  mode", the  $\overline{S}/H$  and  $\overline{RD}$  pins are tied together. A conversion is initiated by pulling both pins low. The A/D converter samples the input voltage and causes the coarse comparators to become active. An internal timer then terminates the coarse conversion and begins the fine conversion. 850 ns (typical) after  $\overline{S}/H$  and  $\overline{RD}$  are pull low,  $\overline{INT}$  goes low, indicating that the conversion is completed. Approximately 20 ns later the data appearing on the TRI-STATE output pins will be valid. Note that data will appear on these pins throughout the conversion, but until  $\overline{INT}$  goes low the data at the output pins will be the result of the previous conversion.

#### 2.0 REFERENCE CONSIDERATIONS

The ADC10061, ADC10062, and ADC10064 each have two reference inputs. These inputs,  $V_{REF+}$  and  $V_{REF-}$ , are fully differential and define the zero to full-scale range of the input signal. The reference inputs can be connected to span the entire supply voltage range ( $V_{REF-} = 0V$ ,  $V_{REF+} = V_{CC}$ ) for ratiometric applications, or they can be connected to different voltages (as long as they are between ground and  $V_{CC}$ ) when other input spans are required. Reducing the overall  $V_{REF}$  span to less than 5V increases the sensitivity of the converter (e.g., if  $V_{REF} = 2V$ , then 1 LSB = 1.953 mV). Note,

however, that linearity and offset errors become larger when lower reference voltages are used. See the Typical Performance Curves for more information. For this reason, reference voltages less than 2V are not recommended.

In most applications,  $V_{REF-}$  will simply be connected to ground, but it is often useful to have an input span that is offset from ground. This situation is easily accommodated by the reference configuration used in the ADC10061, ADC10062, and ADC10064.  $V_{REF-}$  can be connected to a voltage other than ground as long as the voltage source connected to this pin is capable of sinking the converter's reference current (12.5 mA Max @  $V_{REF}$  = 5V). If  $V_{REF-}$  is connected to a voltage other than ground, bypass it with multiple capacitors.

Since the resistance between the two reference inputs can be as low as  $400\Omega$ , the voltage source driving the reference inputs should have low output impedance. Any noise on either reference input is a potential cause of conversion errors, so each of these pins must be supplied with a clean, low noise voltage source. Each reference pin should be bypassed with a 10 µF tantalum and a 0.1 µF ceramic.

#### 3.0 THE ANALOG INPUT

The ADC10061, ADC10062, and ADC10064 sample the analog input voltage once every conversion cycle. When this happens, the input is briefly connected to an impedance approximately equal to  $600\Omega$  in series with 35 pF. Short-duration current spikes can therefore be observed at the analog input during normal operation. These spikes are normal and do not degrade the converter's performance.

Large source impedances can slow the charging of the sampling capacitors and degrade conversion accuracy. Therefore, only signal sources with output impedances less than  $500\Omega$  should be used if rated accuracy is to be achieved at the minimum sample time (250 ns maximum). If the sampling time is increased, the source impedance can be larger. If a signal source has a high output impedance, its output should be buffered with an operational amplifier. The operational amplifier's output should be well-behaved when driving a switched 35 pF/600 $\Omega$  load. Any ringing or voltage shifts at the op amp's output during the sampling period can result in conversion errors.

Correct conversion results will be obtained for input voltages greater than GND – 50 mV and less than V+ +50 mV. Do not allow the signal source to drive the analog input pin more than 300 mV higher than AV $_{\rm CC}$  and DV $_{\rm CC}$ , or more than 300 mV lower than GND. If an analog input pin is forced beyond these voltages, the current flowing through the pin should be limited to 5 mA or less to avoid permanent damage to the IC. The sum of all the overdrive currents into all pins must be less than 20 mA. When the input signal is expected to extend more than 300 mV beyond the power supply limits, some sort of protection scheme should be used. A simple network using diodes and resistors is shown in Figure 4.

#### **Applications Information** (Continued)

FIGURE 4. Typical Connection. Note the multiple bypass capacitors on the reference and power supply pins. If V<sub>REF</sub>is not grounded, it should also be bypassed to analog ground using multiple capacitors (see 5.0 "Power Supply Considerations"). AGND and DGND should be at the same potential. V<sub>INO</sub> is shown with an input protection network. Pin 17 is normally left open, but optional "speedup" resistor R<sub>SA</sub> can be used to reduce the conversion time.

#### 4.0 INHERENT SAMPLE-AND-HOLD

Because the ADC10061, ADC10062, and ADC10064 sample the input signal once during each conversion, they are capable of measuring relatively fast input signals without the help of an external sample-hold. In a non-sampling successive-approximation A/D converter, regardless of speed, the input signal must be stable to better than  $\pm 1/2$  LSB during each conversion cycle or significant errors will result. Consequently, even for many relatively slow input signals, the signals must be externally sampled and held constant during each conversion if a SAR with no internal sample-and-hold is used.

Because they incorporate a direct sample/hold control input, the ADC10061, ADC10062, and ADC10064 are suitable for use in DSP-based systems. The  $\overline{S}/H$  input allows synchronization of the A/D converter to the DSP system's sampling rate and to other ADC10061s, ADC10062s, and ADC10064s.

The ADC10061, ADC10062, and ADC10064 can perform accurate conversions of input signals with frequency components from DC to over 160 kHz.

#### 5.0 POWER SUPPLY CONSIDERATIONS

The ADC10061, ADC10062, and ADC10064 are designed to operate from a +5V (nominal) power supply. There are two supply pins, AV $_{\rm CC}$  and DV $_{\rm CC}$ . These pins allow separate external bypass capacitors for the analog and digital portions of the circuit. To guarantee accurate conversions, the two supply pins should be connected to the same voltage source, and each should be bypassed with a 0.1  $\mu$ F ceramic capacitor in parallel with a 10  $\mu$ F tantalum capacitor. Depending on the circuit board layout and other system considerations, more bypassing may be necessary.

The ADC10061 has a single ground pin, and the ADC10062 and ADC10064 each have separate analog and digital ground pins for separate bypassing of the analog and digital

supplies. The devices with separate analog and digital ground pins should have their ground pins connected to the same potential, and all grounds should be "clean" and free of noise.

In systems with multiple power supplies, careful attention to power supply sequencing may be necessary to avoid over-driving inputs. The A/D converter's power supply pins should be at the proper voltage before digital or analog signals are applied to any of the other pins.

#### **6.0 LAYOUT AND GROUNDING**

In order to ensure fast, accurate conversions from the ADC10061, ADC10062, and ADC10064, it is necessary to use appropriate circuit board layout techniques. The analog ground return path should be low-impedance and free of noise from other parts of the system. Noise from digital circuitry can be especially troublesome, so digital grounds should always be separate from analog grounds. For best performance, separate ground planes should be provided for the digital and analog parts of the system.

All bypass capacitors should be located as close to the converter as possible and should connect to the converter and to ground with short traces. The analog input should be isolated from noisy signal traces to avoid having spurious signals couple to the input. Any external component (e.g., a filter capacitor) connected across the converter's input should be connected to a very clean ground return point. Grounding the component at the wrong point will result in reduced conversion accuracy.

#### 7.0 DYNAMIC PERFORMANCE

Many applications require the A/D converter to digitize AC signals, but conventional DC integral and differential nonlinearity specifications don't accurately predict the A/D converter's performance with AC input signals. The important specifications for AC applications reflect the converter's ability to

#### **Applications Information** (Continued)

digitize AC signals without significant spectral errors and without adding noise to the digitized signal. Dynamic characteristics such as signal-to-noise ratio (SNR) and total harmonic distortion (THD), are quantitative measures of this capability.

An A/D converter's AC performance can be measured using Fast Fourier Transform (FFT) methods. A sinusoidal waveform is applied to the A/D converter's input, and the transform is then performed on the digitized waveform. The resulting spectral plot might look like the ones shown in the typical performance curves. The large peak is the fundamental frequency, and the noise and distortion components (if any are present) are visible above and below the fundamental frequency. Harmonic distortion components appear at whole multiples of the input frequency. Their amplitudes are combined as the square root of the sum of the squares and compared to the fundamental amplitude to yield the THD specification. Typical values for THD are given in the table of Electrical Characteristics.

Signal-to-noise ratio is the ratio of the amplitude at the fundamental frequency to the rms value at all other frequencies, excluding any harmonic distortion components. Typical values are given in the Electrical Characteristics table. An alternative definition of signal-to-noise ratio includes the distortion components along with the random noise to yield a signal-to-noise-plus-distortion ratio, or S/(N + D).

The THD and noise performance of the A/D converter will change with the frequency of the input signal, with more distortion and noise occurring at higher signal frequencies. One way of describing the A/D's performance as a function of signal frequency is to make a plot of "effective bits" versus frequency. An ideal A/D converter with no linearity errors or self-generated noise will have a signal-to-noise ratio equal to

(6.02n + 1.76) dB, where n is the resolution in bits of the A/D converter. A real A/D converter will have some amount of noise and distortion, and the effective bits can be found by:

n (effective) =

$$\frac{S/(N + D) (dB) - 1.76}{6.02}$$

where S/(N + D) is the ratio of signal to noise and distortion, which can vary with frequency.

As an example, an ADC10061 with a 5  $V_{P-P}$ , 100 kHz sine wave input signal will typically have a signal-to-noise-plus-distortion ratio of 59.2 dB, which is equivalent to 9.54 effective bits. As the input frequency increases, noise and distortion gradually increase, yielding a plot of effective bits or S/(N + D) as shown in the typical performance curves.

#### 8.0 SPEED ADJUST

In applications that require faster conversion times, the Speed Adjust pin (pin 14 on the ADC10062, pin 17 on the ADC10064) can significantly reduce the conversion time. The speed adjust pin is connected to an on-chip current source that determines the converter's internal timing. By connecting a resistor between the speed adjust pin and ground as shown in Figure 4, the internal programming current is increased, which reduces the conversion time. As an example, an 18k resistor reduces the conversion time of a typical part from 600 ns to 350 ns with no significant effect on linearity. Using smaller resistors to further decrease the conversion time is possible as well, although the linearity will begin to degrade somewhat (see curves). Note that the resistor value needed to obtain a given conversion time will vary from part to part, so this technique will generally require some "tweaking" to obtain satisfactory results.

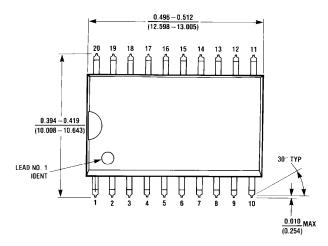

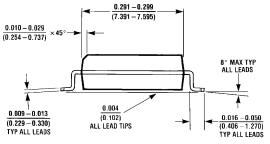

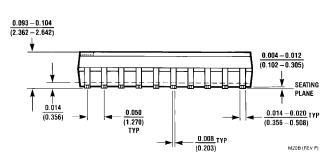

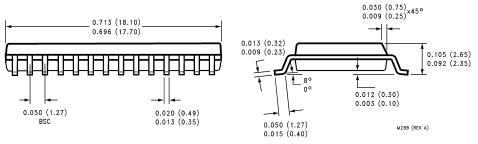

#### Physical Dimensions inches (millimeters) unless otherwise noted

# Order Number ADC10061CIWM NS Package Number M20B

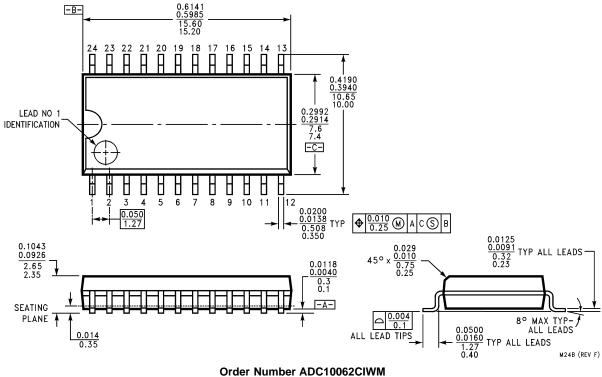

NS Package Number M24B

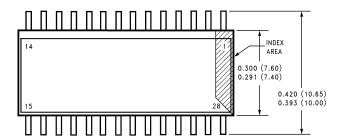

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

Order Number ADC10064CIWM NS Package Number M28B

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor** Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.