# LM1815 Adaptive Variable Reluctance Sensor Amplifier General Description

The LM1815 is an adaptive sense amplifier and default gating circuit for motor control applications. The sense amplifier provides a one-shot pulse output whose leading edge coincides with the negative-going zero crossing of a ground referenced input signal such as from a variable reluctance

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 12V Power Dissipation (Note 2) 1250 mW Operating Temperature Range Storage Temperature Range Junction Temperature Input Current Lead Temperature (Soldering, 10 sec.)  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$   $-65^{\circ}\text{C} \le \text{T}_{\text{J}} \le +150^{\circ}\text{C}$   $+150^{\circ}\text{C}$   $\pm 30 \text{ mA}$  $260^{\circ}\text{C}$

# **Electrical Characteristics** ( $T_A = 25^{\circ}C$ , $V_{CC} = 10V$ , unless otherwise specified, see *Figure 1*)

| Parameter                 | Conditions                                                             | Min | Тур  | Max | Units                                |

|---------------------------|------------------------------------------------------------------------|-----|------|-----|--------------------------------------|

| Operating Supply Voltage  |                                                                        | 2.5 | 10   | 12  | V                                    |

| Supply Current            | f <sub>IN</sub> = 500 Hz, Pin 9 = 2V, Pin 11 = 0.8V                    |     | 3.6  | 6   | mA                                   |

| Reference Pulse Width     | $f_{\text{IN}}$ = 1 Hz to 2 kHz, R = 150k $\Omega$ , C = 0.00 $\mu$ F  | 70  | 100  | 130 | μs                                   |

| Logic Input Bias Current  | V <sub>IN</sub> = 2V, (Pin 9 and Pin 11)                               |     |      | 5   | μΑ                                   |

| Signal Input Bias Current | V <sub>IN</sub> = 0V dc, (Pin 3)                                       |     | 200  |     | nA                                   |

| Input Impedance           | V <sub>IN</sub> = 5 Vrms, (Note 3)                                     | 12  | 20   | 28  | kΩ                                   |

| Zero Crossing Threshold   | V <sub>IN</sub> = 100 mV <sub>P-P</sub> , (Pin 3)                      |     |      | 25  | mV                                   |

| Logic Threshold           | (Pin 9 and Pin 11)                                                     | 0.8 | 1.1  | 2.0 | V                                    |

| V <sub>OUT</sub> High     | $R_L = 1 \text{ k}\Omega, \text{ (Pin 10)}$                            | 7.5 | 8.6  |     | V                                    |

| V <sub>OUT</sub> Low      | I <sub>SINK</sub> = 0.1 mA, (Pin 10)                                   |     | 0.3  | 0.4 | V                                    |

| Input Arming Threshold    | Pin 5 Open, V <sub>IN</sub> = 135 mV <sub>P-P</sub> (Mode 1)           | 30  | 45   | 60  | mV                                   |

|                           | Pin 5 Open, V <sub>IN</sub> ≥ 230 mV <sub>P-P</sub> (Mode 1)           | 40  | 80   | 90  | % of V <sub>3</sub> + P <sub>K</sub> |

|                           | Pin 5 to V <sup>+</sup> , V <sub>IN</sub> ≥ 1V <sub>P-P</sub> (Mode 2) | 200 | 300  | 450 | mV                                   |

|                           | Pin 5 to Gnd, V <sub>IN</sub> ≥ 100mV <sub>P-P</sub> (Mode 3)          | -25 | 0    | 25  | mV                                   |

| Output Leakage Pin 12     | V <sub>12</sub> = 11V                                                  |     | 0.01 | 10  | μA                                   |

| Saturation Voltage P12    | I <sub>12</sub> = 2 mA                                                 |     | 0.2  | 0.4 | V                                    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

**Note 2:** For operation at elevated temperatures, the device must be derated based on a 150°C maximum junction temperature and a thermal resistance of 80°C/W (DIP), 120°C/W (SO-14) junction to ambient.

Note 3: Measured at input to external 18  $k\Omega$  resistor. IC contains 1  $k\Omega$  in series with diode to attenuate the input signal.

#### **Truth Table**

| Signal<br>Input<br>Pin 3 | RC<br>Timing<br>Pin 14 | Input<br>Select<br>Pin 11 | Timing<br>Input<br>Pin 9 | Gated<br>Output<br>Pin 10 |

|--------------------------|------------------------|---------------------------|--------------------------|---------------------------|

| ± Pulses                 | RC                     | L                         | Х                        | Pulses = RC               |

| Х                        | Х                      | Н                         | Н                        | Н                         |

| Х                        | Х                      | Н                         | L                        | L                         |

| ± Pulses                 | L                      | L                         | L                        | Zero                      |

|                          |                        |                           |                          | Crossing                  |

www.national.com

# Truth Table (Continued)

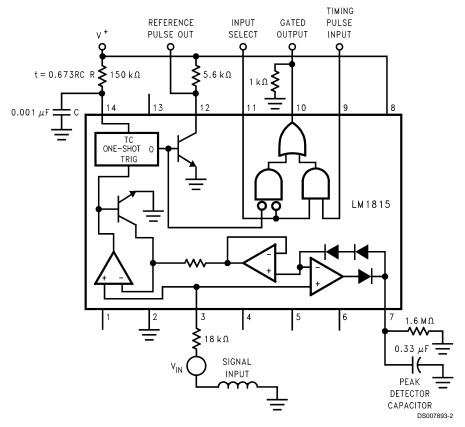

FIGURE 1. LM1815 Adaptive Sense Amplifier

3 www.national.com

### **Application Hints**

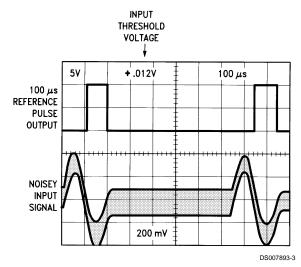

FIGURE 2. LM1815 Oscillograms

#### **Input Voltage Clamp**

The signal input voltage at pin 3 is internally clamped. Current limit for the Input pin is provided by an external resistor which should be selected to allow a peak current of ±3 mA in normal operation. Positive inputs are clamped by a 1 kohm resistor and series diode (see R4 and Q12 in the internal schematic diagram), while an active clamp limits pin 3 to typically 350mV below Ground for negative inputs (see R2. R3, Q10, and Q11 in the internal schematic diagram). Thus for input signal transitions that are more than 350mV below Ground, the input pin current (up to 3mA) will be pulled from the V+ supply. If the V+ pin is not adequately bypassed the resulting voltage ripple at the V+ pin will disrupt normal device operation. Likewise, for input signal transitions that are more than 500mV above Ground, the input pin current will be dumped to Ground through device pin 2. Slight shifts in the Ground potential at device pin 2, due to poor grounding techniques relative to the input signal ground, can cause unreliable operation. As always, adequate device grounding, and V+ bypassing, needs to be considered across the entire input voltage and frequency range for the intended applica-

#### **Input Current Limiting**

As stated earlier, current limiting for the Input pin is provided by a user supplied external resistor. For purposes of selecting the appropriate resistor value the Input pin should be considered to be a zero ohm connection to ground. For applications where the input voltage signal is not symmetrical with relationship to Ground the worst case voltage peak should be used.

Minimum Rext = ((Vin peak)/3mA)

In the application example shown in figure 1 (Rext=18kohms) the recommended maximum input signal voltage is  $\pm 54V$  (i.e. 108Vp-p).

#### Operation of Zero Crossing Detector

The LM1815 is designed to operate as a zero crossing detector, triggering an internal one shot on the negative-going edge of the input signal. Unlike other zero crossing detectors, the LM1815 cannot be triggered until the input signal has crossed an 'arming' threshold on the positive-going portion of the waveform. The arming circuit is

reset when the chip is triggered, and subsequent zero crossings are ignored until the arming threshold is exceeded again. This threshold varies depending on the connection at pin 5. Three different modes of operation are possible:

#### MODE 1, Pin 5 open

The adaptive mode is selected by leaving device pin 5 open circuit. For input signals of less than  $\pm 135 \text{mV}$  (i.e. 270 mVp-p) and greater than typically  $\pm 75 \text{mV}$  (i.e. 150 mVp-p), the input arming threshold is typically at 45 mV. Under these conditions the input signal must first cross the 45 mV threshold in the positive direction to arm the zero crossing detector, and then cross zero in the negative direction to trigger it.

If the signal is less than 30mV peak (minimum rating in Electrical Characteristics), the one shot is guaranteed to not trigger.

Input signals of greater than ±230mV (i.e. 460 mVp-p) will cause the arming threshold to track at 80% of the peak input voltage. A peak detector capacitor at device pin 7 stores a value relative to the positive input peaks to establish the arming threshold. Input signals must exceed this threshold in the positive direction to arm the zero crossing detector, which can then be triggered by a negative-going zero crossing

The peak detector tracks rapidly as the input signal amplitude increases, and decays by virtue of the resistor connected externally at pin 7 track decreases in the input signal. If the input signal amplitude falls faster than the voltage stored on the peak detector capacitor there may be a loss of output signal until the capacitor voltage has decayed to an appropriate level.

Note that since the input voltage is clamped, the waveform observed at pin 3 is not identical to the waveform observed at the variable reluctance sensor. Similarly, the voltage stored at pin 7 is not identical to the peak voltage appearing at pin 3.

#### MODE 2, Pin 5 connected to V+.

The input arming threshold is fixed at 200mV minimum when device pin 5 is connected to the positive supply. The chip has

# Application Hints (Continued)

no output for signals of less than  $\pm 200$  mV (i.e. 400mVp-p) and triggers on the next negative-going zero crossing when the arming threshold is has been exceeded.

#### MODE 3, Pin 5 grounded.

With pin 5 grounded, the input arming threshold is set to 0V, ±25mV maximum. Positive-going zero crossings arm the chip, and the next negative-going zero crossing triggers it. This is the very basic form of zero-crossing detection.

#### One Shot Timing

The one shot timing is set by a resistor and capacitor connected to pin 14. The recommended maximum resistor value is 150kohms. The capacitor value can be changed as needed, as long as the capacitor type does not present any signfigant leakage that would adversely affect the RC time constant.

The output pulse width is:

pulse width =

$$0.673 \times R \times C$$

(1)

For a given One Shot pulse width, the recommended maximum input signal frequency is:

$$Fin(max) = 1/(1.346 \times R \times C)$$

(2)

In the application example shown in figure 1 (R=150kohms, C=0.001µF) the recommended maximum input frequency will typically be 5kHz. Operating with input frequencies above the recommended Fin (max) value may result in unreliable performance of the One Shot circuitry. For those applications where the One Shot circuit is not required, device pin 14 can be tied directly to Ground.

#### **Logic Inputs**

In some systems it is necessary to externally generate pulses, such as during stall conditions when the variable reluctance sensor has no output. External pulse inputs at pin 9 are gated through to pin 10 when Input Select (pin 11) is pulled high. Pin 12 is a direct output for the one shot and is unaffected by the status of pin 11.

Input/output pins 9, 11, 10, and 12 are all CMOS logic compatible. In addition, pins 9, 11, and 12 are TTL compatible. Pin 10 is not guaranteed to drive a TTL load.

Pins 1, 4, 6 and 13 have no internal connections and can be grounded.

www.national.com

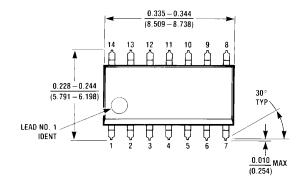

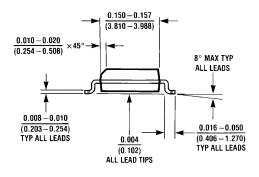

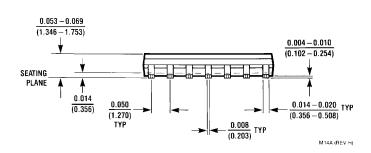

# Physical Dimensions inches (millimeters) unless otherwise noted

# 14-Lead Small Outline Circuit (M) Order Number LM1815M NS Package Number M14A

Molded Dual-In-Line Package (N) Order Number LM1815N NS Package Number N14A

#### **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Email: support@nsc.com

www.national.com

**National Semiconductor**

Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor** Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.