## DC Restored 100 MHz Current Feedback Video Amplifier

by John Lidgey and Chris Toumazou

#### Summary

The EL2090 is an extremely versatile video amplifier with an integral on-board DC loop amplifier and sample-hold control circuitry. It is the first complete DC-restored monolithic video amplifier subsystem. It uses a current-feedback video amplifier with a nulling sample and hold amplifier specifically designed to stabilize video performance. This application note includes a video signal restorer with some fundamentals about DC restoration. As an application circuit of the EL2090, a x2 gain video amplifier is described together with a full evaluation circuit and double sided pc-board artwork. The EL2090 is a high-speed part, and some useful tips on layout have been included.

Although DC restoration is not a new concept, the high slew-rate, fast settling-time and low phase distortion at high frequencies provided by Elantec's family of monolithic current-feedback amplifiers, make CFAs the most attractive video amplifier choice for this application.

#### Video Signal Refresher

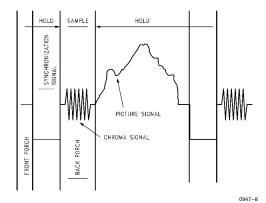

Figure 1 is a typical composite video signal which has a standard distribution level of 1V peak-to-peak into  $75\Omega$ , and comprises

several sections. The video signal is the part containing the visible picture information, with a maximum amplitude between black and white of 0.7V. At the end of the picture information is the front-porch followed by a -0.3V of sync pulse, which is regenerated to provide system synchronization. The back porch is the part of the signal that represents the black or blanking level. In color NTSC systems the chroma or color burst signal is added to the back porch, normally occupying 9 cycles of 3.58 MHz subcarrier (4.43 MHz for PAL systems).

Video signals are often AC coupled to avoid DC bias interaction between different systems. The blanking level of the composite video signal needs to be restored to an externally set DC voltage, which locks the video signal to a predetermined common reference level, ensuring consistency in the picture displayed. This DC reference voltage  $V_R$ , sets and controls the picture brightness. The fundamental objective of the DC restore system is to force the DC baseline from the video amplifier to equal the externally set reference voltage  $V_R$ .

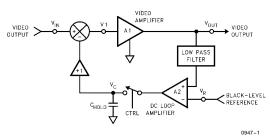

Figure 2 shows the schematic of a classical DC control servo system.

Figure 1. Video Signal

Figure 2. Classical DC Control Servo

#### Video Signal Refresher — Contd.

The sync pulse is used to drive the control switch so that the DC servo loop is closed during the back porch of the video signal. The low pass filter removes the chroma burst. Operation of the DC loop is best understood by considering the voltage, V<sub>C</sub>, across the hold capacitor, C<sub>HOLD</sub>. During the back porch sample period, the switch is closed and the hold capacitor charges up. It can be shown from the loop dynamics that,

$$V_C = V_{BP} - V_{BP}/[A_1^*A_2] - V_R/A_1$$

where  $V_{\mbox{\footnotesize{BP}}}$  is the average back porch voltage for the sample period.

The net result is that  $V_{OUT} = V_R - V_{BP}/A_2$ , which shows that the output is clamped to  $V_R$  with an offset term of  $-V_{BP}/A_2$ . This offset is clearly small with a high gain DC loop amplifier,  $A_2$ . The EL2090 has a DC loop amplifier gain of 15 kV/V, reducing this offset to the order of a few millivolts. During the hold period the switch is open and the stored DC value of  $V_C$  is now subtracted from the incoming video signal, making

$$\begin{split} \textbf{V}_1 &= \textbf{V}_{IN} - \textbf{V}_{BP} + \textbf{V}_R/\textbf{A}_1 \\ &\text{and so} \\ \textbf{V}_{OUT} &= \textbf{A}_1 \left[ \textbf{V}_{IN} - \textbf{V}_{BP} \right] + \textbf{V}_R \end{split}$$

which effectively sets the back porch to  $V_R$  and the video signal is amplified by the forward amplifier with gain,  $A_1$ .

## **Subcircuits**

The EL2090 DC restored amplifier is a 14-pin monolithic version of the circuit shown in Figure 2. The video amplifier,  $A_1$ , is a 100 MHz current feedback amplifier or CFA. These devices offer very high speed performance with excellent differential gain and phase. In many respects the CFA behaves as a conventional op-amp, but there are several key differences that must be considered by the user. In particular the two input impedances of the amplifier are different. The non-inverting input is high impedance and the inverting low impedance. However, the special feature of the CFA is that when in closed loop, the feedback current is determined by resistor, R<sub>F</sub>, which controls the bandwidth of the amplifier independently of the gain setting resistor R<sub>G</sub>.

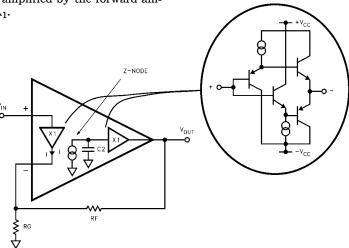

The current feedback amplifier is essentially a transimpedance amplifier with an input voltage buffer to create a high input impedance non-inverting input. The transimpedance amplifier is formed by mirroring the output current of the input unity gain buffer into a high impedance internal Z-node and buffering this Z-node voltage through a low impedance output, as shown schematically in Figure 3 below.

Figure 3. The Current-Feedback Amplifier

### Subcircuits — Contd.

The unity gain buffers are a complementary class-AB common-collector stage, with DC current biasing. The slew-rate of the CFA is excellent due to the non-current-limiting input stage. The CFA has only one internal high impedance node (Z), so it is essentially a single pole dominant amplifier. Since the inverting input terminal is the output terminal of a voltage buffer, it is a low impedance point and the feedback signal is current. Intuitively one can see that in closed loop the feedback current through R<sub>F</sub> supplies the current demanded by RG and the input error current into the inverting input terminal. It is this feedback current component of R<sub>F</sub> which is used to charge the compensation capacitance at the Z-node. Theoretically it can be shown that the -3 dB bandwidth is approximately,

$$f - 3 dB = 1/[2\pi R_F C_Z]$$

where  $C_Z$  is the compensation capacitance of the Z-node. However, as for conventional op-amps, the closed loop gain,  $A_1$ , is simply

$$A_1 = [1 + R_F/R_G],$$

and the -3 dB frequency can be controlled with  $R_{\rm F}$  while the closed loop gain can be set independently with  $R_{\rm G}.$

#### Features of the EL2090

Elantec pioneered the development of monolithic CFAs. A first to the market with the CFA the established reputation is confirmed with the EL2090 which is the first monolithic DC restored video amplifier. The device is built with Elantec's fast proprietary complementary bipolar technology which yields NPN and PNP transistors with equivalent AC and DC performance.

The on-chip current-feedback ampifier is optimized for video performance, and since it is a current-feedback amplifier it ensures that the  $-3~\mathrm{dB}$

bandwidth stays essentially constant for various closed-loop gains. The amplifier performs well at frequencies as high as 100 MHz when driving  $75\Omega$ . The sample and hold circuit is optimized for fast sync pulse response; the switch operates in only 40 ns. A particular feature of this sample and hold output buffer is its low output impedance which is fairly constant over frequency and load current. This provides good isolation and thus prevents the DC restore circuit from interfering with video amplifier performance through  $R_{\rm AZ}$ .

Note that the burst output of Elantec's EL4581 and EL4583 sync separator chips can drive the Hold input of the 2090 directly.

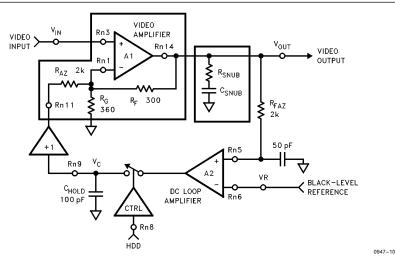

#### **Typical Application Circuit**

Figure 4 shows a component level schematic diagram of the gain x2 DC restored video amplifier. The operation of the circuit is based upon the simple analysis given with the amplifier connected in the non-inverting mode of operation. The application circuit will restore the video DC level in ten scan lines, even if the hold pulse is as short as 2  $\mu s$  long. The current-feedback resistor  $R_F$  of  $300\Omega$  will give a stable bandwidth of 115 MHz and all component values are chosen to maintain optimum speed and performance.

DC feedback resistor  $R_{AZ}$  is 2 k $\Omega$  and is sufficiently larger than RF to provide reasonable isolation between the sample and hold circuit and video amplifier and thus avoid any video signal coupling back to the sample-hold. RAZ may be (optionally) split into two 1 k $\Omega$  resistors and a 820 pF bypass capacitor to reduce unwanted transient feedthrough from the sample and hold to the video signal to less than about 1 mV seen at the amplifier's output. The circuit is designed to operate using  $\pm 15V$  supplies, but it can operate down to  $\pm 5V$  supplies by changing  $R_{AZ}$  and CAZ values. Alternatively an inverting configuration video amplifier could be used with appropriate exchange of the input signals to the DC loop amplifier.

Figure 4. DC Restored Video Amplifier with  $A_V = 2$

### **Design Procedures**

### 1. Determining R<sub>AZ</sub>

Ideally RAZ should be large to provide good isolation between the sample and hold buffer and the video amplifier. This is because any videoinduced current through RAZ will cause changes in the buffer output impedance. A large series RAZ will reduce the effect of buffer output impedance variations and thus preserve the differential gain error of the video amplifier. However, too large a value of RAZ along with the output voltage compliance of the buffer will limit the maximum  $I_{AZ}$ , the DC correction current. A lower IAZ will result in a lower restored reference level. Consequently, trade-offs have to be made between R<sub>AZ</sub>, the maximum restored reference level, and the supply voltage which controls the output voltage compliance of the buffer. The following equations address some of the issues related to the trade-offs.

During the back-porch of the video signal, the sample and hold switch is closed. The servo loop charges  $C_{\mbox{HOLD}}$  to a voltage level necessary to bring the video amplifier output to the reference input level. The maximum voltage of  $C_{\mbox{HOLD}}$  is limited by the supply voltages.

$$V_{REF} = (V_{BP} * A_1) - V_{AZ} (R_F/R_{AZ})$$

(1)

where

V<sub>REF</sub> is the new stabilized back-porch level at the output of the video amplifier.

$V_{\mathrm{BP}}$  is the input back-porch offset voltage at the video amplifier input

$A_1$  is the close loop gain of the video amplifier.

$$A_1 = R_F (1/R_{AZ} + 1/R_G) + 1$$

(2)

$R_F$  is the feedback resistor of the current-feedback video amplifier. It is nominally  $300\Omega$  for  $A_1=+2.$  In gain of +5 application,  $R_F$  should be decreased to  $270\Omega$  to maintain gain flatness

$V_{\rm AZ}$  is the buffered  $C_{\rm HOLD}$  voltage developed by the loop to maintain the output at the reference level.

V<sub>AZ</sub> is limited to the supply rails less 2.5V.

$$\begin{array}{l} -\mathrm{V_{SUPPLY}} + 2.5\mathrm{V} < \mathrm{V_{AZ}} < \\ +\mathrm{V_{SUPPLY}} - 2.5\mathrm{V} \end{array} \tag{3}$$

Analysis of equation (1) shows that since  $V_{BP}$ ,  $A_1$ , and  $R_F$  values are established by system requirements, the maximum  $R_{AZ}$  is determined by  $V_{AZ}$  and  $V_{REF}$ . A high  $R_{AZ}$  value requires a proportionally high  $V_{AZ}$  voltage and low  $V_{ref}$ . Outside the back-porch period, the switch is opened. The DC offset is maintained.

## 2. Design Example

Below examples are intended to show how  $R_{\rm AZ}$  changes under different supply voltages and reference level.

#### Example A.

$\begin{array}{l} V_{SUPPLY} = \pm 15V \\ V_{REF} = 0V \\ A_1 = 2 \\ V_{BP} = \pm 1V \\ R_F = 300\Omega \end{array}$

Applying equation (3), the output voltage compliance  $V_{AZ}$  of the sample and hold buffer can be calculated,

$-12.5V \leq V_{AZ} \leq 12.5V$  Using equation (1),  $R_{AZ}=1.8~k\Omega$  for  $V_{BP}=+1V$

Once  $R_{AZ}$  is determined, equation (2) gives  $R_G = 360\Omega$ .

#### Example B.

$V_{SUPPLY} = \pm 5V$   $V_{REF} = 0V$   $A_1 = 2$   $V_{BP} = \pm 1V$

Applying equation (1),  $R_{AZ}=375\Omega$  for  $V_{BP}=\pm 1V$ .

Equation (2) gives  $R_G = 1.5 \text{ k}\Omega$ .

#### Example C.

$V_{SUPPLY} = \pm 15V$   $V_{REF} = 1$   $A_1 = 2$   $V_{BP} = \pm 1V$

Applying equation (3),  $-12.5 V \leq V_{AZ} \leq 12.5 V$   $R_F = 300 \Omega$  Equation (1) gives  $R_{AZ} = 1.2 \ k\Omega \ \text{for} \ V_{BP} = -1 V$   $R_{AZ} = 3.75 \ k\Omega \ \text{for} \ V_{BP} = -1 V$  Therefore,  $R_{AZ} = 1.2 \ k\Omega$  Using equation (2),  $R_G = 400 \Omega.$

The above examples demonstrate the trade-off between the supply voltage,  $R_{AZ}$ , and the reference level. Examples A and B reveal that a lower supply voltage requires a lower  $R_{AZ}$ . Examples A

and C show that when the supply rails are kept constant, a higher reference level requires a lower  $R_{\Delta Z}$ .

## 3. Determine C<sub>HOLD</sub>

Fast acquisition time is achieved with small values of  $C_{HOLD}$ , but this degrades droop performance. For video the droop needs to be better than  $\frac{1}{2}$  IRE in one horizontal line, or less than 3.5 mV in 45  $\mu$ s for NTSC. The droop is primarily caused by  $C_{HOLD}$  voltage decaying. Since the droop of  $C_{HOLD}$  is amplified to the output by the ratio  $R_F/R_{AZ}$  then  $C_{HOLD}$  must be chosen to satisfy  $dV_C/dt < 3.5$  mV/45 $\mu$ s multiply  $R_{AZ}/R_F = 510$  V/ $\mu$ s

$R_F = 510V/\mu s$ .

Since  $dVC/dt = I_{DROOP}/C_{HOLD}$ , and the discharge current  $I_{DROOP}$  is a maximum of 50 nA, then

C<sub>HOLD</sub> • 98 pF, or 100 pF, the nearest preferred value.

If  $R_{AZ}$  is decreased for lower supply operation,  $C_{AZ}$  is correspondingly increased to preserve droop and acquisition characteristics.

## 4. Acquisition Time

Based on the values shown in Figure 4 the acquisition time is approximately  $20\mu s$ . Note that it will take 10 chroma-burst of  $2\mu s$  each to finish settling from a  $\Delta 1.0V$  input signal shift.

#### **Evaluation Printed Circuit Board**

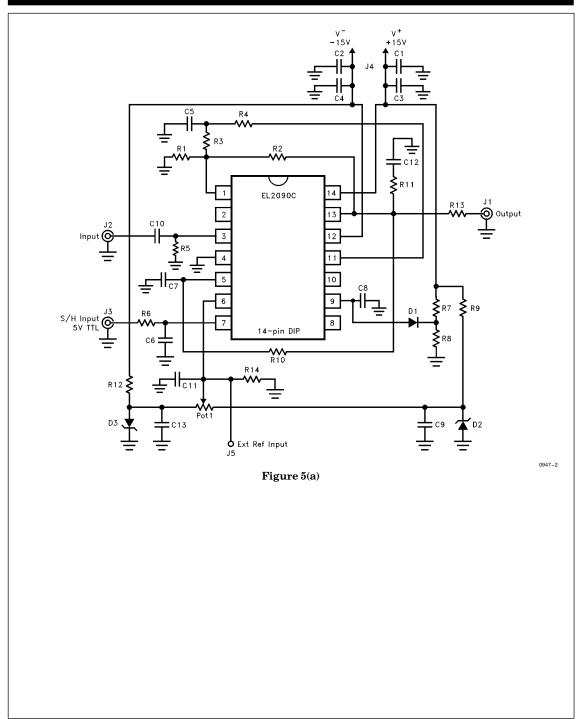

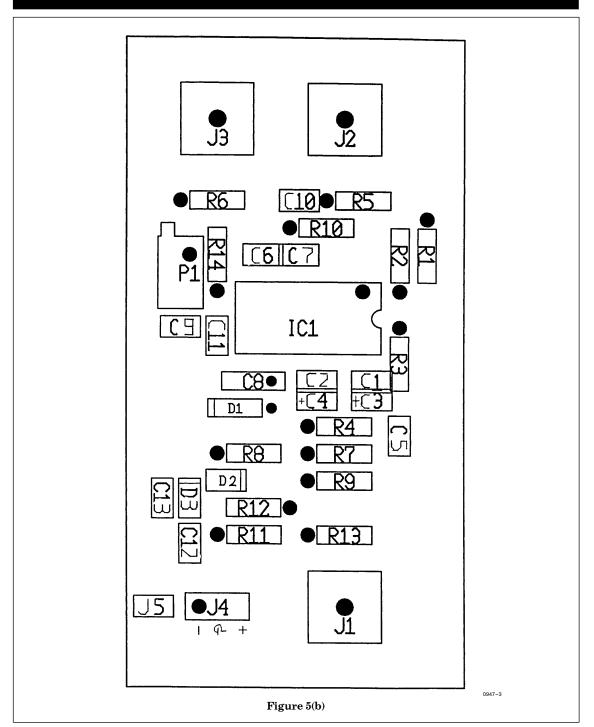

A component layout of the application circuit is shown in Figure 5(b) with some additional features.

- V<sub>REF</sub> is applied externally to the grounded resistor R<sub>14</sub>, which is decoupled with capacitor C<sub>11</sub>.

- Optional 75Ω termination resistor has been included at the input and output.

- Built in guard ring on PCB board layout (Figure 5(b)) ensures that leakage from the hold capacitor is minimal to improve droop performance. The guard ring is connected to the S/H Out. The hold capacitor should be low leakage and so mica or mylar capacitors are recommended here.

## **Evaluation Printed Circuit Board**

#### — Contd.

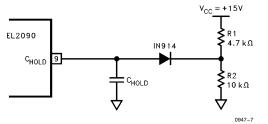

- Diode clamp circuit to overcome lock-up has been included on board.

- Optional AC input coupling capacitors of about 10  $\mu F$  has been included.

- Optional snubber circuit has been included.

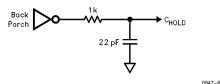

- Optional R-C low pass filter on hold input logic drive has been included should the logic signal require slowing down.

# Printed Circuit Board and Layout Hints

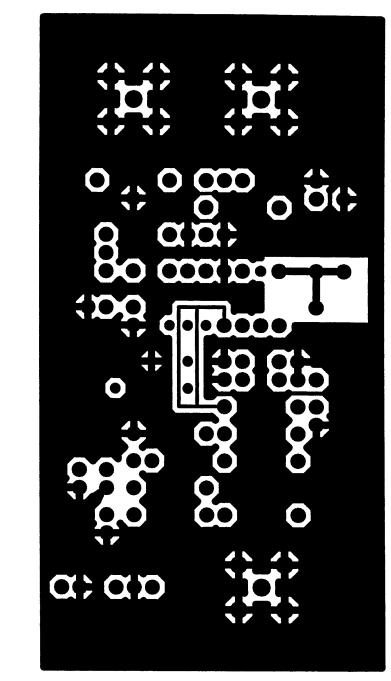

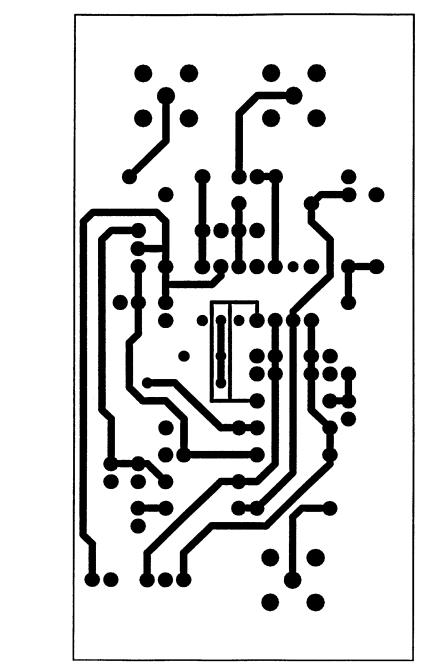

Figure 5(a)-(d) on following pages, shows a component layout together with double sided pcboard. Ground plane is essential throughout to reduce parasitic inductance and stray pickup. Special precautions have been taken to avoid any discontinuity in ground plane since this will make the function of ground plane much less effective. Supply decoupling capacitors are kept close to the power supply pins to ensure good power supply integrity. The feedback path of the video amplifier should be kept as small as possible to avoid deterioration in high frequency gain accuracy. BNC connectors are included at the input and output.

| R1  | $= 360\Omega$          | C1         | $= 0.1 \ \mu F$            | POT1 | $=$ 10 k $\Omega$         |

|-----|------------------------|------------|----------------------------|------|---------------------------|

| R2  | $=300\Omega$           | <b>C</b> 2 | $= 0.1 \ \mu F$            | D1   | = 1N914                   |

| R3  | $=$ 1 k $\Omega$       | <b>C</b> 3 | = $4.7 \mu F$ (Tant.)      | D2   | = ZN458B                  |

| R5  | $=75\Omega$            | <b>C</b> 5 | =820 pF                    | D3   | $= ZN458B (2.45 V_{REF})$ |

| R6  | $= 220\Omega$          | <b>C</b> 6 | = 39 pF                    |      |                           |

| R7  | $=$ 4.7 k $\Omega$     | <b>C</b> 7 | = 50 pF                    |      |                           |

| R8  | $=$ 10 k $\Omega$      | C8         | = 100 pF                   |      |                           |

| R9  | $=$ 10 k $\Omega$      | <b>C</b> 9 | = $0.1 \mu F$ (Ceramic)    |      |                           |

| R10 | $=$ 2 k $\Omega$       | C10        | = 4.7 $\mu$ F (Tant., 25V) |      |                           |

| R11 | $= 100\Omega$          | C11        | = 4.7 $\mu$ F (Tant., 25V) |      |                           |

| R12 | $=$ 10 k $\Omega$      | C12        | = 30 pF                    |      |                           |

| R13 | $=75\Omega$            | C13        | = $0.1 \mu F$ (Ceramic)    |      |                           |

| R14 | $= 10 \text{ k}\Omega$ |            |                            |      |                           |

Figure 5(a). Component Values

Figure 5(c)

Figure 5(d)

0947-5

### Do's and Don'ts

### General Circuit Layout

As with all high frequency devices care must be taken with printed circuit board layout. Good ground plane construction is essential and DC power supply integrity must be ensured, so the power supply pins should be bypassed to ground with ceramic capacitors as close to the supply pins of the device as possible. The video current feedback amplifier is, like all CFAs, particularly sensitive to stray capacitance at the inverting input. This capacitance combined with the inverting node input resistance generates an additional high frequency pole in the feedback loop of the CFA leading to gain peaking in the response. Consequently pc-boards should be designed to keep lead lengths as short as possible around the inverting input node, with the ground plane positioned sufficiently far away to prevent this gain peaking effect.

#### **Load Capacitance**

In general load capacitance with negative feedback amplifiers causes gain peaking. This is because the load capacitance with the non-zero output resistance of the amplifier creates an additional pole in the feedback loop. The video CFA within the EL2090 is no exception to this and it may be necessary to add a series R-C snubber network to ground to minimize peaking, as shown in the data sheet, where the appropriate components are selected for a particular value of load capacitance.

#### Sample and Hold Section

Clock-feedthrough to C<sub>HOLD</sub> leads to an undesirable hold-step, effecting the DC bias level.

Figure 6

Increasing  $C_{HOLD}$  is the most direct way of reducing this effect. Under normal operation the loop amplifier only deals with a small correction to  $V_{C}$  and although increasing  $C_{HOLD}$  will compromise the slew-rate of the sample-hold section, this is not a practical limitation. However with  $C_{HOLD} > 1$  nF and the sampling interval  $t_{S} < 2$  ms then on power up the device may lock-up if  $V_{C}$  approaches  $V_{CC}$ , causing the output transistors of the sample-hold amplifier to be taken out of their active region. The net result is that the lock-up does not self recover. Limiting  $V_{C}$  to  $V_{CC} - 3V$  using the external clamp circuit shown in Figure 4 prevents this lock-up condition from occuring.

Figure 7