SOCS059 - JUNE 1996

- High-Resolution, Bulk Charge Modulated Device (BCMD) Technology Image Sensor for NTSC Color Applications

- 1/3-in Image Area Diagonal

- 680 (H) x 500 (V) Active Elements in the Image-Sensing Area

- 7.4-µm Square Pixels

- No Detectable Smear

- No Image Lag

- 2000:1 Blooming Overload Capability

- Intrinsic Exposure Control

- Random Line Addressable

- Dual-Line Readout

- Dynamic Range: > 70 dB

- 0 5-V Clocking Levels

#### description

The Texas Instruments (TI<sup>™</sup>) TC286 is designed for use in single-chip color National Television Standards Committee (NTSC) TV, computer, and special-purpose applications requiring high picture quality, excellent antiblooming capability, electronic exposure control, and no smear.

•

The TC286 is a unique imaging device based on a MOS transistor structure with a buried photosite well. This structure integrated into a high-performance image sensor array is called a bulk charge modulated device (BCMD). The BCMD image sensor features an 1/3 inch diagonal image sensing area configured into 500 lines with 680 pixels in each line. Four lines on the bottom of the image area form dark references, and 22 elements on the left side, covered by a light shield, form the dark current reference elements used for dark current subtraction and dc level restoration. The image area measures 5.0 mm (horizontal) x 3.7 mm (vertical) with each pixel being 7.4  $\mu$ m square.

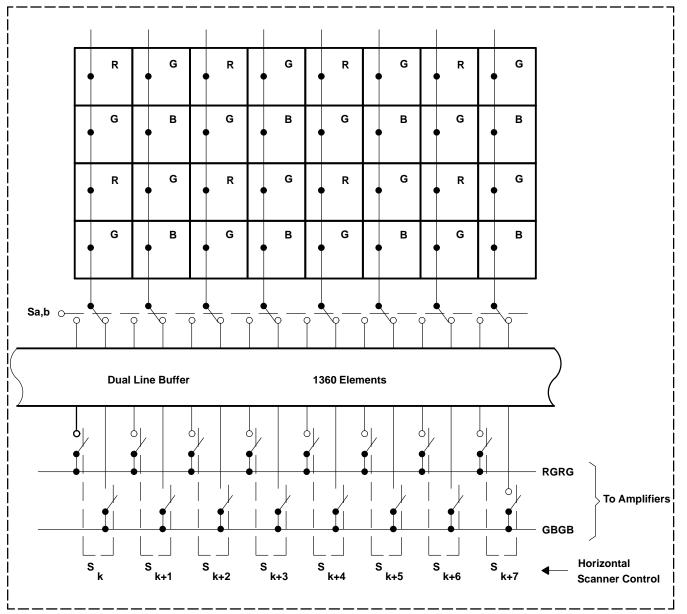

The BCMD sensor requires 0 to 5-V CMOS-level clock signals for its operation, and all dc bias levels are within the range of 0 to 8 V. The image signal from the array is processed line by line in parallel. Vertical array addressing is used to transfer two complete lines of data into a line buffer during the horizontal blanking interval. In color applications, the dual-line readout significantly improves the sensor resolution above that of competitive devices of the same format. The line buffer is configured to store two lines of 680 elements. The TC286 employs an on-chip color filter arranged in a mosaic pattern. Two serial registers are used to read out the pixels. From the first register, a red pixel is read first and then a green pixel. This alternating pixel pattern continues until the line is read out. From the second register, a green pixel is read first and then a blue pixel. The green pixel is output at the same time a red pixel is output from the first register. Using this readout method, four pixels (one red, one blue, and two greens) can be used to form one color pixel for NTSC color applications.

The BCMD cell is a n-type buried-channel MOS transistor with an additional p-type well implanted under the transistor channel. The potential valley created serves as a storage place for photogenerated holes.

As light enters the silicon in the image-sensing area, free holes are generated and collected in the potential wells of the sensing elements. The holes change the potential profile of the device structure, which, in turn, affects the threshold of the MOS transistor. As current flows through the transistor, the threshold change is sensed as a source voltage variation of each of the transistors. The hole well is emptied or reset by applying a negative pulse to the drain of the transistor. The cell reset is complete with no residual carriers in the well and, therefore, no reset noise or image lag, both important features for low light level sensitivity of the cell.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI is a trademark of Texas Instruments Incorporated.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

1

SOCS059 - JUNE 1996

#### description (continued)

After each integration cycle, the image readout sequence begins by selecting an appropriate line pair in the image-sensing array and transferring its voltage signal into the line buffer in a sequential order during the horizontal blanking interval. During this transfer operation, photocell threshold nonuniformities are internally removed by a clamping and sampling process that results in uniform output levels. The stored signal is then read out of two serial registers.

The device intrinsic exposure control operates on a principle resembling the action of a mechanical focal plane shutter used in standard photographic cameras. The equivalent width of the shutter slit is defined electronically and is scanned across the sensor in a vertical direction. The maximum range of control available in the sensor is 288:1.

The TC286 is built using TI-proprietary advanced virtual phase (AVP) technology, which provides devices with high blue response, low dark signal, good uniformity, and single-phase clocking. The TC286 is characterized for operation from  $-10^{\circ}$ C to  $45^{\circ}$ C.

# $\begin{array}{c} \text{TC286} \\ \text{680-} \times \text{500-PIXEL CCD IMAGE SENSOR} \end{array}$

SOCS059 - JUNE 1996

### functional block diagram

## TC286 680- $\times$ 500-PIXEL CCD IMAGE SENSOR

SOCS059 - JUNE 1996

### **Terminal Functions**

| TERMINAL        |           |     |                           |  |

|-----------------|-----------|-----|---------------------------|--|

| NAME            | NO.       | I/O | DESCRIPTION               |  |

| ADB             | 8         | I   | Antiblooming drain bias   |  |

| B00             | 13        | I   | Vertical address bit 0    |  |

| B01             | 12        | I   | Vertical address bit 1    |  |

| B02             | 11        | Ι   | Vertical address bit 2    |  |

| B03             | 10        | Ι   | Vertical address bit 3    |  |

| B04             | 7         | Ι   | Vertical address bit 4    |  |

| B05             | 6         | Ι   | Vertical address bit 5    |  |

| B06             | 5         | Ι   | Vertical address bit 6    |  |

| B07             | 4         | Ι   | Vertical address bit 7    |  |

| B08             | 3         | Ι   | Vertical address bit 8    |  |

| IBA             | 18        | Ι   | Amplifier bias current    |  |

| IBP             | 32        | Ι   | Photosite bias current    |  |

| PC1             | 26        | Ι   | Horizontal register 1     |  |

| PC2             | 25        | Ι   | Horizontal register 2     |  |

| PCP             | 31        | Ι   | Line clamp                |  |

| PGB             | 9         | Ι   | Photocell gate bias       |  |

| PIN             | 24        | Ι   | Horizontal register pulse |  |

| PRS             | 17        | -   | Reset clock               |  |

| PS1             | 29        | -   | Sample and hold 1         |  |

| PS2             | 28        | Ι   | Sample and hold 2         |  |

| PST             | 27        | Ι   | Pixel strobe              |  |

| VAS             | 14        | Ι   | Vertical address strobe   |  |

| V <sub>DD</sub> | 1, 16     | Ι   | 5-V substrate bias        |  |

| VRF             | 30        | Ι   | Line clamp reference      |  |

| VR1             | 21        | 0   | Output reference 1        |  |

| VR2             | 22        | 0   | Output reference 2        |  |

| V <sub>SS</sub> | 2, 15, 23 | Ι   | Ground                    |  |

| V01             | 19        | 0   | Output 1                  |  |

| V02             | 20        | 0   | Output 2                  |  |

## $\begin{array}{c} \text{TC286} \\ \text{680-} \times \text{500-PIXEL CCD IMAGE SENSOR} \end{array}$

SOCS059 - JUNE 1996

### operating conditions, clock levels = 0 to 5 V, dc bias = -5 V to 5 V, T<sub>A</sub> = $25^{\circ}$ C

| PARAMETER                         | MIN TYP          | MAX UNIT           |

|-----------------------------------|------------------|--------------------|

| Output impedance                  | 500              | Ω                  |

| Saturation output voltage         | 1000             | mV                 |

| Saturation current                | 320              | nA                 |

| Photosite charge capacity         | 100,000          | е                  |

| Charge conversion factor          | 10               | μV/e               |

| Dark signal (@ 25°C)              | 1.5              | nA/cm <sup>2</sup> |

| Noise floor                       | 32               | е                  |

| Dynamic range                     | 70               | dB                 |

| Faceplate saturation (T = 2856°K) | 20               | lux                |

| Response nonuniformity            | <2%              |                    |

| Blooming overload range           | >2000 saturation |                    |

| Exposure control range            | 288:1            |                    |

| Smear                             | 0%               |                    |

| Lag                               | 0%               |                    |

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated