Edited by Bill Travis

## Tricks increase utility of parallel port

Lorenzo Tazzari, Selex SNC, Alessandria, Italy

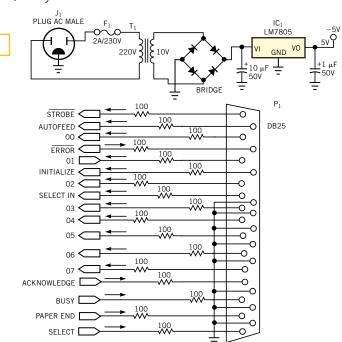

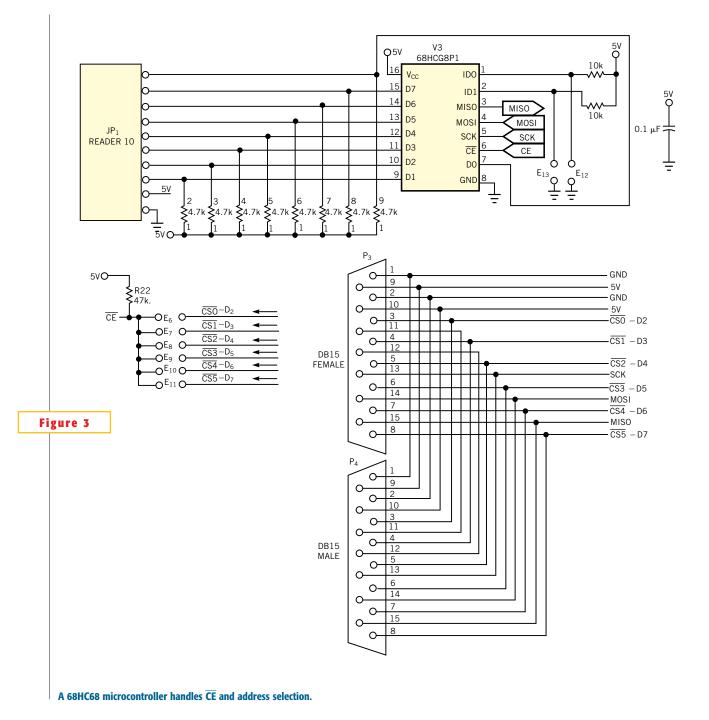

N THIS SIMPLE APPLICATION of the 68HC68 microcontroller's se-**Figure 1** rial-I/O utility, the goal is to configure a simple circuit, driven by any LPT parallel-printer port, which you can use as a remote I/O for a PC. You can independently program each I/O line as either an input or an output. The protocol in this application is an SPI (MISO/ MOSI/SCK) type, using synchronous serial communications. Figure 1 shows a circuit that effects the connection with the PC and power supply for all I/O signals. A bus carries signals of the SPI protocol, and the LPT port can drive all the  $\overline{\text{CE}}$  (Chip Enable) signals. With this type of bus, you drive as many as five  $\overline{CE}$  signals, and each  $\overline{CE}$  line can address four 68HC68 chips. Each microcontroller can drive eight I/O lines, with each line independently programmable. Thus, the system can address as many as 160 I/O ports.

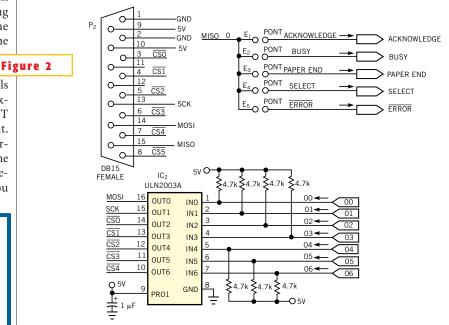

Figure 2 shows a simple way to select the MISO signal. You can choose which pin of the LPT port to use in receiving the MISO signal. This circuit uses the ULN2003 as an amplifier to drive the critical  $\overline{CE}$  signal. By joining the SIP and  $\overline{CE}$  signals, you can configure a bus system in which all signals go to the bus connector. You need an external power supply, because the LPT port cannot supply sufficient current. You can connect as many as five I/O circuits. The circuit in Figure 3 contains the 68HC68 chip with its  $\overline{CE}$  and address selection. With jumpers  $E_{12}$  and  $E_{13}$ , you

| Tricks increase utility of parallel port          |    |

|---------------------------------------------------|----|

| Transistors tame perfidious<br>leakage inductance | 80 |

| 18-bit ADC uses<br>PC's serial port               | 84 |

ideas

This simple scheme facilitates selection of the MISO signal in the SPI protocol.

www.ednmag.com

can select the chip's address. It is important to emphasize that the system has no check for an address conflict arising from choosing the same address, with the same  $\overline{CE}$ , in more than one chip. If the conflict arises, however, it does not cause hardware damage. Theoretically, using an LPT port at a baud rate of 1 Mbyte/sec, the technique can read or write 160 I/O signals in less than 16 msec. Is this the best Design Idea in this issue? Vote at www.ednmag.com.

## Transistors tame perfidious leakage inductance

Christophe Basso, On Semiconductor, Toulouse, France

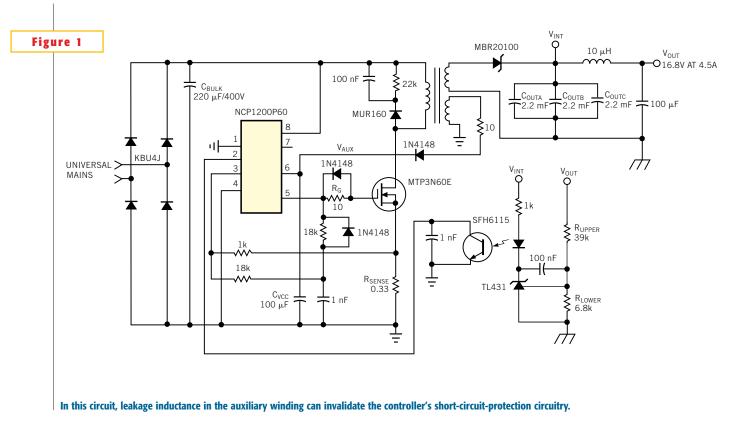

N FLYBACK CONVERTERS that use primary regulation, the loose coupling between the power secondary and the primary auxiliary windings often results in poor cross-regulation. This situation arises mainly from the leakage inductance but also comes from the level of the primary clamp voltage. Figure 1 shows a typical application schematic using On Semiconductor's (www.onsemi.com) NCP1200 in an auxiliary-winding configuration. This IC uses a DSS (dynamic self-supply), but in some low-standbypower applications, it is desirable to permanently disconnect this feature through an auxiliary level. The DSS simply acts as a standard start-up current source until the auxiliary level takes over. In this application, the regu-

lation takes place on the secondary side by means of the TL431, but the primary

level assumes importance in short-circuit conditions. Each time the NCP1200's  $V_{CC}$  crosses 10V while dropping, the internal logic senses the eventual presence of a short circuit through the feedback pin. Should the circuit confirm a short circuit, the NCP1200 emits a safe-autorecovery, low-frequency burst. However, if poor coupling prevents the auxiliary winding from collapsing, in the presence of a secondary short circuit,  $V_{CC}$  never crosses the 10V threshold, and damage to the circuit may ensue.

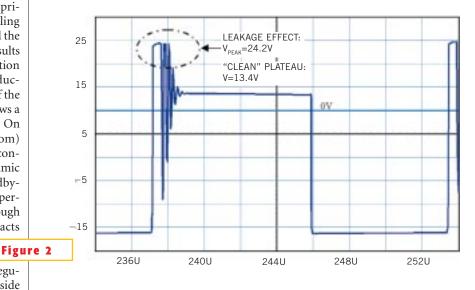

**Figure 2** details the effects of the leakage inductance when a short circuit occurs at the output. As you can see, the leakage spike pushes the auxiliary level well above its regular plateau voltage, which is the value you'd like to obtain. With the rectifying diode playing the role of an envelope detector, the result is a final level close to 24V, far from the 13.4V you would expect. As a result, a

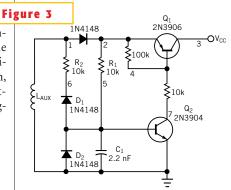

possibly destructive condition exists if the levels exceed the maximum ratings in the controller's data sheet. You need to clamp the auxiliary voltage using a dissipative element, such as a zener diode. Figure 3 shows the circuitry you adopt to avoid the leakage-inductance problems. The component arrangement actually implements a self-contained sample-and-hold system. When the main power switch is on, capacitor C1 discharges through R<sub>2</sub> and D<sub>1</sub>, and D<sub>2</sub> avoids a large reverse bias of Q<sub>2</sub>'s base-emitter junction. When the main switch opens, the secondary voltage sharply rises, and Node 1 becomes positive. However, because C1 discharges, Q1 remains open, and  $V_{CC}$  does not increase.

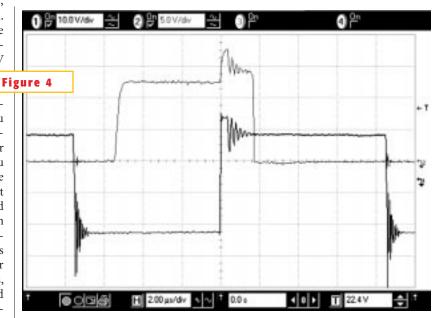

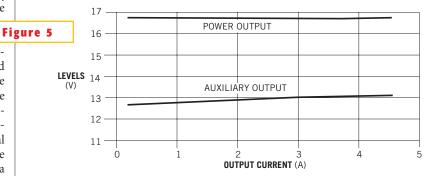

After a short period (adjustable via  $R_1$ or  $C_1$ ),  $Q_2$  closes and brings  $Q_1$ 's base closer to ground.  $V_{CC}$  now increases and catches up to the level at Node 2, minus  $Q_1$ 's  $V_{CE(SAT)}$ . If you correctly select the time delay,  $V_{CC}$  is devoid of any voltage spike, because you have sampled the plateau. **Figure 4** shows the final result. Performing some measurements on a 70W application board featuring low standby power yields the final tracking results in **Figure 5**. You can see that a 4.3A change in  $I_{OUT}$  results in a change of only 420 mV in  $V_{OUT}$ . You can use the circuit in a primary-regulation application in which you need a precise level without either heavily filtering the secondary winding (and thus lowering the available auxiliary energy in standby mode) or reducing the primary clamp voltage to a higher dissipative value. In the NCP1200 application, when a short circuit appears at the output, the auxiliary winding properly triggers the short-circuit protection.

Is this the best Design Idea in this issue? Vote at www.ednmag.com.

This component arrangement creates a discrete sample-and-hold system.

By delaying the sampling time, you obtain a clean auxiliary level that is devoid of any leakageinductance effects.

Thanks to the circuit in Figure 3, the auxiliary winding better tracks the primary winding.

## **18-bit ADC uses PC's serial port**

Yongping Xia, Teldata, Los Angeles, CA

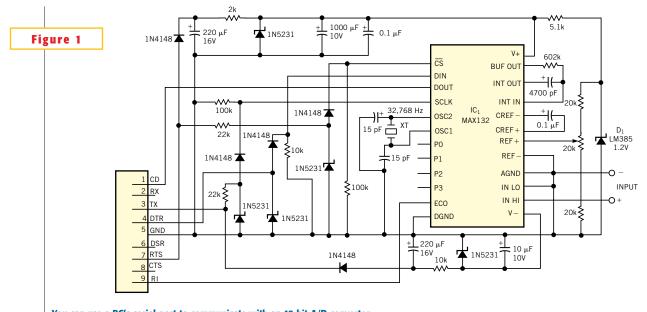

PC USUALLY REQUIRES a plug-in ADC card to process analog signals. However, with the circuitry in Figure 1, a PC can communicate with an 18bit ADC through its serial port. The port provides both positive and negative power supplies as well as control signals. IC<sub>1</sub> is an 18-bit MAX132 ADC with a serial interface. It requires three input control signals,  $\overline{CS}$ , DIN, and SCLK, and emits serial data, DOUT, and EOC (end-of-conversion) signals. An RS-232 port has three output lines: Pin 3 (TX), Pin 4 (DTR), and Pin 7 (RTS). TX generates the clock signal for the MAX132 and provides the negative power supply. DTR transmits serial data. RTS provides the CS signal and the positive power supply. Both the positive and the negative supplies use large capacitors for energy storage. When TX generates a clock signal or DTR sends a CS logic-low signal, the capacitors provide power to the MAX-132. The MAX132 integrates everything except a reference that comes from a 1.2V LM385 voltage-reference diode, D., The

input-voltage range of the MAX132 is -512 to +512 mV. Listing 1 is a C program that displays the analog-to-digital-conversion result on-screen. You can download Listing 1 from the Web version of this Design Idea at www.ednmag.com.

Is this the best Design Idea in this issue? Vote at www.ednmag.com.

### LISTING 1-SCREEN-DISPLAY ROUTINE FOR ANALOG-TO-DIGITAL-CONVERSION RESULTS

#include <stdio.h> #include <dos.h> int control[4], out\_control; #include <time.h> data=0: #include <conio.h> for (i=0: i<4: i++) #include <bios.h> in\_data[i]=0; #include <conio.h> control[0]=0x82; control[1]=0x04; #define COM1 0 control[2]=0x00; #define MCR /\* control register control[3]=0x00: #define MSR /\* status register out\_data=0x02; /\* CS high outportb(base\_add1+MCR, out\_data); int i, j, base\_add1=0x3f8, base\_add2=0x2f8, out\_data=0x03, in\_data[4]; delay(10); float data: out data&=0x01: outportb(base\_add1+MCR, out\_data); /\* CS low void send\_clk(void) delay(10); delav(1): out control=control[0] outportb(base\_add1, 0x00); for (i=0; i<8; i++) delay(3); } if (out\_control>=0x80) out\_data=0x01; Continued on pg 86 void read port(void) معام

# designideas

in\_data[j]=in\_data[j]\*2+(inportb(base\_add1+MSR)&0x80)/0x80;

data=(float)(in\_data[1]&0x07)+(float)(in\_data[2])\*2048+(float)(in\_data[3])\*8; else /\* reading is negative \*/

/\* clock out

/\* CE high

÷,

\*/

send\_clk(); out control&=0x7f;

out\_data|=0x02;

if ((in\_data[1]&0x08)==0)

delay(10);

out\_control=out\_control\*2;

outportb(base\_add1+MOR, out\_data);

#### LISTING 1–SCREEN-DISPLAY ROUTINE FOR ANALOG-TO-DIGITAL-CONVERSION (CONTINUED) out\_data&=0x02; { in\_data[1]=in\_data[1]&0x07; outportb(base\_add1+MCR, out\_data); send\_clk(); /\* clock out \*/ in\_data[1]=(8-in\_data[1])&0x07; out control&=0x7f; in\_data[2]=(256-in\_data[2])&0xff; in\_data[3]=(256-in\_data[3])&0xff; out\_control=out\_control\*2; } data= -((float)(in\_data[1])+(float)(in\_data[2])\*2048+(float)(in\_data[3])\*8); out\_data|=0x02; } outportb(base\_add1+MCR, out\_data); /\* CS high } \* 1 void dis\_data(void) delay(10); do{ { }while((inportb(base\_add1+MSR)&0x40)==0); /\* waiting for EOC=high float show\_data; show\_data=0.000002\*data; gotoxy(1,1); for (j=1; j<4; j++) printf("%.5f ", show\_data); { gotoxy(1,1); out\_control=control[j]; in\_data[j]=0; } out\_data&=0x01; outportb(base\_add1+MCR, out\_data); /\* CS low void init(void) \*/ delay(10); for (i=0; i<8; i++) ł bioscom(0, 255, COM1); /\* set up COM1 \*/ { if (out\_control>=0x80) out\_data=0x02; out\_data = 0x01; outportb(base\_add1+MCR, out\_data); /\* CS=high, DIN=low else \* out data&=0x02; delay(100); outportb(base\_add1+MCR, out\_data); }

void main(void) {

gotoxy(60,24);

printf("Hit any key to quit");

read\_port();

dis\_data(); delay(500);

} while(!kbhit());

clrscr(); init();

do{

}