Edited by Bill Travis and Anne Watson Swager

# Bridge-temperature measurement allows software compensation

John Wynne, Analog Devices Inc, Limerick, Ireland

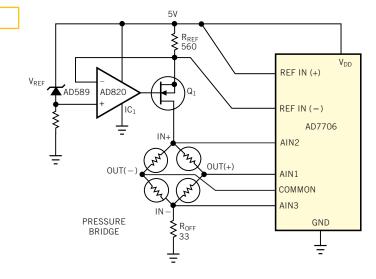

RIDGE TRANSDUCERS ARE notoriously temperature-sensitive. When the temperature changes, almost everything else varies with some parameters increasing and some decreasing. The TCS (temperature coefficient of span) is generally negative for piezoelectric pressure sensors, and the TCR (temperature coefficient of resistance) is positive. In other words, as the temperature rises, the sensitivity decreases, and the resistance of the bridge increases. In general, the TCS and TCR are close to each other. This fact has in the past motivated designers to add both active and passive external components to achieve some measure of temperature compensation. However, the calibration of such systems can be tedious; the resulting performance, problematic. Piezoelectric-bridge manufacturers have tried to ease **Figure 1**

efficients in their manufacturing processes. Another approach is to simply measure the temperature of the bridge and then use a  $\mu$ C to compensate in software, given certain basic properties, such as the bridge resistance at 25°C and the TCR. This approach is effective, but concerns that the temperature you measure may not be the real temperature of the bridge hamper it. For instance, placing the temperature sensor relative to mechanical attachment of the strain gauge has a crucial bearing on the accuracy of the reading. It's not unusual to see errors of 1°C or more in such situations. The idea presented here (Figure 1), suggested in Reference 1, is to determine the temperature of the bridge by measuring the voltage

ideas

across the bridge as a result of a known excitation current flowing through it.

$R_{REF}$ , reference voltage  $V_{REF}$ , and op amp IC<sub>1</sub> determine the excitation current, which equals  $V_{REF}/R_{REF}$ . The differential bridge output, seen between terminals OUT(+) and OUT(-), feeds directly into channel AIN1 of the AD7706 ADC. This signal is a pseudodifferential input with respect to the ADC's Common input and can accept full-scale signals as low as 20 mV while providing full 16-bit performance. The AD7706 has three pseudodifferential inputs, all having the Common input as reference. The Common input connects to the midpoint of the bridge and serves a reference point from which to make all

| Bridge-temperature measureme<br>allows software compensation . |                |

|----------------------------------------------------------------|----------------|

| Timer automatically shuts off                                  |                |

| Video amplifier provides<br>digital gain control               |                |

| Simple circuit detects dc ringing                              |                |

| Gated clock has duty-cycle cont                                | rol <b>132</b> |

| Tripler converts 5 to 15V                                      |                |

| Generate stabilized PWM signa                                  | ls <b>136</b>  |

| Switched-capacitor converter su portable applications          |                |

| Current-limit switch is digitally programmable                 | 140            |

the problem by equalizing the co-

You can provide software compensation for bridge-temperature coefficients through accurate temperature measurements.

the necessary measurements. Computing the voltage across the bridge entails two additional measurements. Input channel AIN2 measures the voltage from the top of the bridge to its midpoint (Common terminal), and input channel AIN3 measures the voltage from the midpoint to the bottom of the bridge. You can then compute the voltage across the bridge. Assume that the resistance of the bridge is independent of the pressure under measurement at least to the extent that the error is small compared with the measured results. The AD7706 is a complete, 16-bit (with 14-bit maximum integral nonlinearity) delta-sigma ADC intended for dc and low-frequency ac measurements. Because its power consumption is 1 mW maximum at 3V, you can use the device in loop-powered, battery-powered, and local applications. The on-chip programmable-gain amplifier has gain settings of 1 to 128 to accommodate both low- and high-level analog inputs without the need for external signal-conditioning hardware. You can find additional information about the IC at http:// products.analog.com/products/info.asp? product=AD7706. (DI #2576)

#### Reference

1. Paillard, Bruno, "Temperature compensating an integrated pressure sensor," *Sensors*, January 1998, pg 36.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/ednmag/ infoaccess.asp, enter No. 440 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

#### Timer automatically shuts off

Yongping Xia, Teldata Inc, Los Angeles, CA

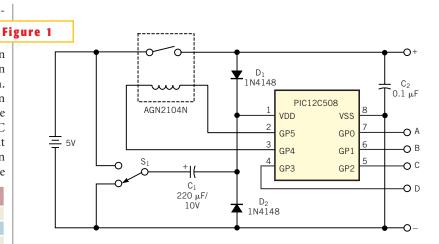

The CIRCUIT IN Figure 1 is a programmable power switch that offers on-state periods of 5 sec to three hours. It consumes zero power in the off state and has zero voltage drop in the on state.  $S_1$  is a power-on switch. When you press  $S_1$ , the battery powers an eight-pin PIC12C508  $\mu$ C. Because the value of  $C_1$  is fairly large, it powers the  $\mu$ C long enough for the processor to send out a pulse through GP5 and GP4 to turn on a latching relay. Once the relay is on, the

| TABLE 1-DELAY | TIMES         |

|---------------|---------------|

| DCBA          | Time          |

| 0000          | 10 sec        |

| 0001          | 15 sec        |

| 0010          | 20 sec        |

| 0011          | 30 sec        |

| 0100          | 45 sec        |

| 0101          | One minute    |

| 0110          | Two minutes   |

| 0111          | Three minutes |

| 1000          | Five minutes  |

| 1001          | 10 minutes    |

| 1010          | 15 minutes    |

| 1011          | 30 minutes    |

| 1100          | 45 minutes    |

| 1101          | One hour      |

| 1110          | Two hours     |

| 1111          | Three hours   |

This timer consumes no power in the off state and has zero voltage drop in the on state.

$\mu$ C derives power through D<sub>1</sub>. C<sub>1</sub> discharges through D<sub>2</sub> when you release the button. After turning on the relay, the  $\mu$ C reads the four inputs GP0 through GP3 to determine the delay time (**Table 1**). Once the time is over, an inverted pulse appears on GP5 and GP4 and turns off the latching relay. Once the relay turns off, the circuit consumes no power. You can download the PIC12C508 assembly program for the timer from *EDN*'s Web site, www.ednmag.com. Click on "Search

Databases" and then enter the Software Center to download the file for Design Idea #2571. (DI #2571)

Is this the best Design Idea in this issue? Vote at www.ednmag.com/ednmag/ infoaccess.asp, enter No. 441 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

### Video amplifier provides digital gain control

Stephen Woodward, University of North Carolina, Chapel Hill, NC

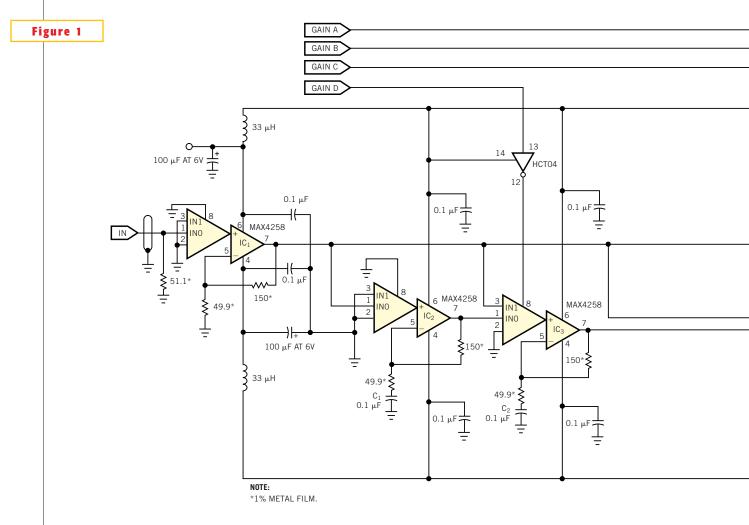

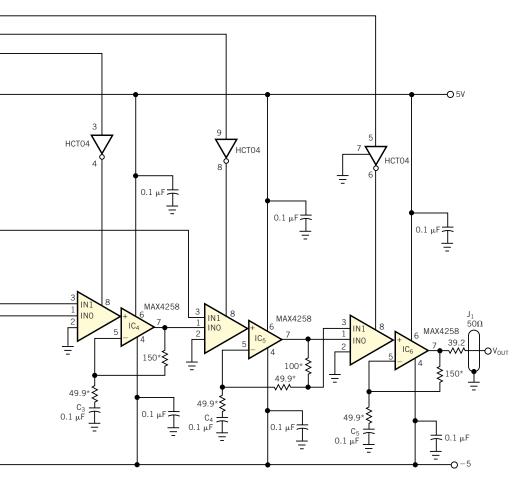

**P**ROGRAMMABLE-GAIN AMPLIFIERS, many of them monolithic, are continuously improving, with lower noise and higher gain-bandwidth products. But for high-end applications, multichip circuits are still necessary. For example, the amplifier in **Figure 1** originally served as the photomultiplier preamplifier in a Doppler system intended for eventual operation in the Martian atmosphere. The design is based on a

switchable array of six Maxim MAX4258 dual-channel video multiplexer-amplifiers,  $IC_1$  through  $IC_6$ . Under control of a 4-bit input word, you can set the number of stages in the gain cascade to three, four, five, or six. Because each multiplexer-amp has a fixed gain of four, each unit change in the stage count changes the overall gain by 12 dB. In addition, you can interpose a 6-dB attenuator between the last and the next-to-last gain stages.

The attenuator adds a factor-of-two resolution to the programmed gain and eight distinct gain settings (**Table 1**).

Gain-change settling time is lower than 30 nsec. The greater-than-100-MHz bandwidth of each stage results in an overall passband for all gain settings of greater than 60 MHz. The five lowpass-bandpass capacitors,  $C_1$  through  $C_5$ , determine the lower end of the passband. In the original application, the frequen-

You can obtain eight distinct gain settings with this low-noise, high-bandwidth video amplifier.

cies of interest don't extend much below 100 kHz. So, using  $0.1-\mu$ F capacitors results in a roll-off of approximately 50 kHz. Larger values for these capacitors would reduce this figure. Omitting the capacitors for a dc response is not recommended, however, because the resulting amplification of IC<sub>1</sub>'s input offset would produce an output offset in the order of volts at high gain settings. You can generate

|       | _  |         |    |          |                                       |

|-------|----|---------|----|----------|---------------------------------------|

| TABLE | 1- | DIGITAL | GA | IN SETTI | NGS                                   |

| Code  | D  | С       | В  | A        | Gain (into 50 $\Omega$ , in decibels) |

| 1     | 0  | 0       | 0  | 0        | ×16=24.1                              |

| 2     | 0  | 0       | 0  | 1        | ×32=30.1                              |

| 3     | 0  | 0       | 1  | 0        | ×64=36.1                              |

| 4     | 0  | 0       | 1  | 1        | ×128=42.1                             |

| 5     | 0  | 1       | 1  | 0        | ×256=48.2                             |

| 6     | 0  | 1       | 1  | 1        | ×512=54.2                             |

| 7     | 1  | 1       | 1  | 0        | ×1024=60.2                            |

| 8     | 1  | 1       | 1  | 1        | ×2048=66.2                            |

|       |    |         |    |          |                                       |

the gain-programming word using any TTLcompatible, 8-bit parallel-I/O port, such as a PC's parallel printer port or an EIA-1284compatible port. The HCT04 CMOS inverter chip in the gain-control pathway blocks any possible noise entry in the gain-control lines.

The overall input-referred voltage noise is approximately 2 nV per the square root of hertz, equivalent to the Johnson noise of a  $250\Omega$  resistor. Maximum output level is 15 dBm (3.6V p-p) into  $50\Omega$  and twice that into high-impedance loads. The combination of extreme gain and high-frequency response (gain-bandwidth products approaching 200 GHz) of this circuit mandates careful attention to issues of ground-plane and power-supply-bypass integrity. In addition, you must make every effort to minimize stray capacitance around the feedback-pin (Pin 5) components of all gain stages. (DI #2559)

Is this the best Design Idea in this issue? Vote at www.ednmag.com/ ednmag/infoaccess.asp, enter No. 442 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

#### Simple circuit detects dc ringing

Jerzy Chrzaszcz, Warsaw Institute of Technology, Poland

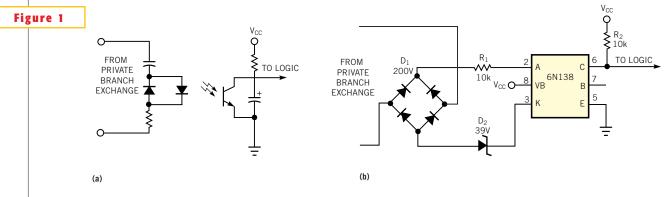

**R** ING DETECTION IS a common task in telephony-related digital design. The goal is to sense an ac ringing voltage applied to the telephone line by a central office or PBX (private branch exchange) and then pass an appropriate signal to the  $\mu$ C or  $\mu$ P. **Figure 1a** shows a typical ac-coupled ring-detection circuit. The serially connected capacitor closes the ac path and the optoisolator provides galvanic isolation between the line and the logic. The output capacitor integrates the pulse train to form a ring envelope signal. More sophisticated designs may use the unfiltered output for ring-frequency discrimination. Unfortunately, some PBX systems signal ringing to extension phones by raising the dc line voltage. A traditional ac-coupled detector is thus useless. The circuit in **Figure 1b** consists of a full-wave rectifier, a current-limiting resistor, a zener diode, and a high-gain optoisolator with output pullup. By changing component values, you can easily meet circuit requirements for circuit isolation, input-voltage range, threshold voltage, and line load. (DI #2567)

Is this the best Design Idea in this issue? Vote at www.ednmag.com/ednmag/ infoaccess.asp, enter No. 443 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

The ac-coupled circuit in (a) is useless in some PBX systems; the configuration in (b) takes over for PBX-generated dc ringing signals.

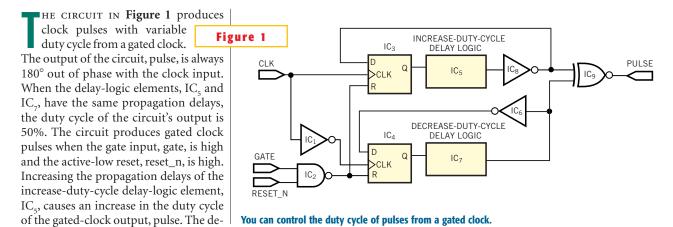

#### Gated clock has duty-cycle control

Paul Kemp, University of Colorado, Colorado Springs, CO

crease-duty-cycle delay-logic element,  $IC_{7}$ , reduces the duty cycle of the gatedclock output. **Listing 1** is a Verilog model of the circuit; a Verilog testbench verifies the circuit's function. A pair of delay-logic elements is modeled with 20 de-

| igure 2         |                   |     |     |              |              |           |               | Cursor2     | = 1475 |

|-----------------|-------------------|-----|-----|--------------|--------------|-----------|---------------|-------------|--------|

|                 |                   | 100 | 200 | ,400         | ,600         | ,800      | ,1000         | ,1200       | 1475   |

| Group: Inputs   |                   |     |     |              |              | <b>_</b>  |               |             |        |

|                 | GATE = 0          |     |     |              |              |           | mm            |             |        |

| R               | SET N = 0         |     |     |              |              |           |               |             |        |

| Group: Outputs  |                   | ۲   |     |              |              |           |               |             |        |

|                 | PULSE = 0         |     |     | บบบบบ        |              |           |               |             |        |

| Group: Variable | s                 |     |     |              |              |           |               |             |        |

| count [5:0      | )] ≃ 'h xx        | xx  |     |              |              |           | 04 06 08 0A 0 |             |        |

| duty_cycle[31:  |                   |     | 0 5 | 0 54 57 62 6 | 5 70 72 78 8 | 0 86 50   | 47 41 37      | 33 29 26 22 | 19 14  |

| Group: Increase |                   |     |     |              |              |           |               |             |        |

| SELECT [4 :     | 0] = 'd 0         | -   | 2   | 4 6 8 1      | 0 12 14 16 1 | .8 10     |               |             |        |

|                 | IN = 0<br>OUT = 0 |     |     |              |              |           |               |             |        |

| Group: Decrease |                   |     |     |              |              | ليا ليصحا |               |             |        |

| ~               | [0] = 'd 0        |     |     |              |              | 1         | 2 4 6 8 1     | 0 12 14 16  | 18 20  |

| Dilliger [1.    | IN = 0            |     |     |              |              |           |               |             |        |

|                 | OUT = 0           |     |     |              |              |           |               |             |        |

|                 |                   |     |     |              |              |           |               |             |        |

|                 |                   |     |     |              |              |           |               |             |        |

|                 |                   |     |     |              |              |           |               |             |        |

|                 |                   |     |     |              |              |           |               |             |        |

|                 |                   |     |     |              |              |           |               |             |        |

|                 |                   |     |     |              |              |           |               |             |        |

|                 |                   |     |     |              |              |           |               |             |        |

lay lines of 1 nsec each. The testbench instantiated this operation. A simulation (**Figure 2**) used Cadence Verilog-XL. A

> 20-MHz clock serves as the input clock. The select signals in Figure 2 for the increase-dutycycle delay-logic element, IC<sub>5</sub>, and the decrease-duty-cycle delay-logic element, IC<sub>7</sub>, correspond to the number of 1-nsec delay elements inserted into the delay paths. Thus, a select value of 12 corresponds to a 12nsec delay. You can download Listing 1 and the Verilog testbench from EDN's Web site, www.ednmag.com. Click on "Search Databases" and then enter the Software Center to download the file for Design Idea #2554. (DI #2554)

Is this the best Design Idea in this issue? Vote at www.edn mag.com/ednmag/infoaccess. asp, enter No. 444 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

Verilog simulates the function of the circuit in Figure 1.

| LISTIN                 | G 1-GATED-CLOCK DUTY-CYCLE CONTROLI                                                   | .ER                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| `timescale 1:          | ns/lps // lns time units with lps resolution                                          | <pre>// Parameter Declarations parameter dly = 1;</pre>                                                                                         |

| module pulse           | shaper (                                                                              |                                                                                                                                                 |

| • • •                  | CLK, // I<br>GATE, // I<br>GATE DEC DLY, // I                                         | <pre>// Generate a pulse from the system clock (CLK) and GATE signals.<br/>assign #dly FULSE = GATE_INC_DLY ^ GATE_DEC_DLY;</pre>               |

|                        | GATE INC_DLY, // I<br>RESET N, // I<br>GATE_DEC, // O<br>GATE_INC, // O<br>PULSE // O | always @(posedge CLK or negedge RESET_N or negedge GATE) begin<br>if (~RESET_N) begin<br>GATE_INC <= #dly 1'b0;<br>end<br>else if (~GATE) begin |

|                        | );                                                                                    | GATE_INC <= #dly 1'b0;<br>end                                                                                                                   |

|                        | eclarations                                                                           | else begin                                                                                                                                      |

| input                  | CLK; // System clock                                                                  | GATE_INC <= #dly ~GATE_INC_DLY;                                                                                                                 |

| input                  | GATE; // Active high signal produces variable duty cycle                              | end                                                                                                                                             |

| pulses                 |                                                                                       | end                                                                                                                                             |

| input                  | GATE_DEC_DLY; //                                                                      |                                                                                                                                                 |

| input<br>input         | GATE INC DLY; //<br>RESET N; // Active low asynchronous reset                         | always @(negedge CLK or negedge RESET_N or negedge GATE) begin<br>if (~RESET N) begin                                                           |

| Input                  | RESET_N; // ACLIVE IOW asynchronous reset                                             | II (~RESET_N) Begin<br>GATE_DEC <= #dly 1'b0;<br>end                                                                                            |

| // Output              | Declarations                                                                          | else if (~GATE) begin                                                                                                                           |

| output                 | PULSE; // Variable duty cycle output pulse                                            | GATE_DEC <= #dly 1'b0;                                                                                                                          |

| output                 | GATE_DEC; //                                                                          | end                                                                                                                                             |

| output                 | GATE_INC; //                                                                          | else begin<br>GATE_DEC <= #dly ~GATE_DEC_DLY;<br>end                                                                                            |

| <pre>// Registe:</pre> | r Declarations                                                                        | end                                                                                                                                             |

| reg                    | GATE_DEC; //                                                                          |                                                                                                                                                 |

| reg                    | GATE INC; //                                                                          | endmodule                                                                                                                                       |

### **Tripler converts 5 to 15V**

Ken Yang, Maxim Integrated Products, Sunnyvale, CA

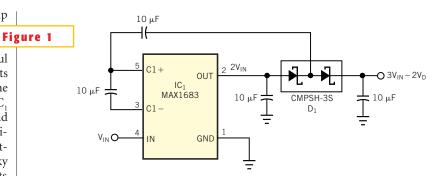

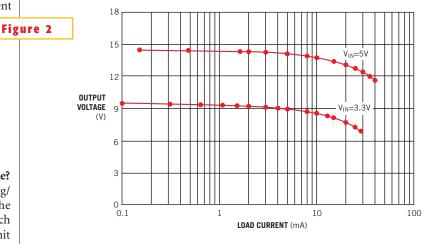

**B** Y CONFIGURING A charge-pump voltage doubler as a tripler, you can readily derive 15V from 5V (Figure 1). A 15V rail is useful for powering op amps, LCD-bias circuits and other low-current applications. The connections shown configure the IC<sub>1</sub> voltage doubler as a tripler. The no-load output voltage of the circuit is approximately  $3V_{IN}-2V_{D}$ , where  $V_{D}$  is the voltage drop across one diode. Use Schottky diodes as shown to minimize  $V_{D}$  and its effect on output voltage. Because the circuit's finite output impedance causes the output voltage to drop with load current

(Figure 2), a practical limit for load current is approximately 30

This circuit (almost) triples the input voltage for low-current applications.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/ednmag/ infoaccess.asp, enter No. 445 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

## **Generate stabilized PWM signals**

Martin Ossmann, FH, Aachen, Germany

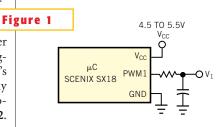

STANDARD TECHNIQUE FOR generating analog voltages using  $\mu$ Cs is to use a PWM output and filter the signal with a simple RC filter (Figure 1). The voltage of the PWM signal is directly proportional to the  $\mu$ C's supply voltage, so it is not necessarily clean or stable. To overcome this problem, you can use the circuit in Figure 2. Here, a 74HC14 Schmitt-trigger array serves as an output stage for three PWM signals from an SX18  $\mu$ C. (The idea ap-

This classic PWM circuit suffers from supplyvoltage sensitivity.

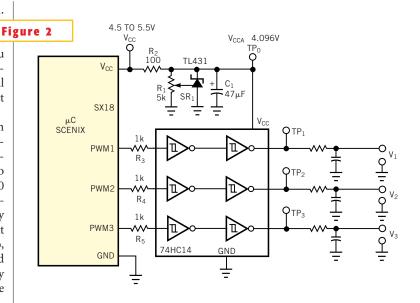

plies to other  $\mu$ Cs, too.) The 74HC14 derives its supply voltage, V<sub>CCA</sub>, from the stabilization circuit comprising the inexpensive shunt regulator, SR<sub>1</sub>. You can adjust V<sub>CCA</sub> by trimming R<sub>1</sub>. The test circuit used V<sub>CCA</sub>=4.096V. The PWM signals now have a stable amplitude that varies less than 0.1% when the  $\mu$ C's supply varies from 4.5 to 5.5V. Resistors R<sub>3</sub> to R<sub>5</sub> limit the current flowing from the  $\mu$ C through the 74HC14's input-protection diodes when V<sub>CCA</sub> is too low. The values

of R and C depend on the application. The test circuit uses  $10 \text{ k}\Omega$  and 4.7

μF. If you feed multiple analog (or PWM) signals through a single IC, you usually encounter crosstalk. To characterize the circuit in **Figure 1** for internal crosstalk and unmatched delays, conduct the following tests.

Generated three PWM signals with different frequencies and 1-to-1 duty cycles. With a 0-dB reference-level squarewave signal at test point TP<sub>1</sub>, crosstalk to test points  $TP_2$  and  $TP_3$  measures -70dB. The first harmonic of the PWM signal (theoretically zero for a 1-to-1 duty cycle) is down 65 dB at test point TP<sub>1</sub>. At test point  $TP_{o}$ , spurs are down 75 dB. So, the circuit in Figure 1 has very good crosstalk characteristics. Also, if the duty cycle of one PWM channel changes, the influence on the voltage that other channels generates is less than 0.1%. You must take care to ensure that the switching delays of the 74HC14 do not change with varying  $V_{cc}$  applied to the  $\mu$ C. If the switching delays change with  $V_{CC}$  because of the changing levels of the driving signals, V<sub>CC</sub> influences the generated output voltage, even if  $V_{CCA}$  is constant. You can use the circuit for precise generation of

Schmitt triggers with a stabilized supply make the PWM signals insensitive to supply voltage.

voltages, thanks to the temperature stability of the TL431. You can also use it for inexpensive implementations of sigmadelta converters, or to generate voltagestabilized rectangular waveforms. (DI #2573) Is this the best Design Idea in this issue? Vote at www.ednmag.com/ednmag/ infoaccess.asp, enter No. 446 in the "Circle Number" field and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

# Switched-capacitor converter suits portable applications

Clinton Jensen, National Semiconductor, Santa Clara, CA

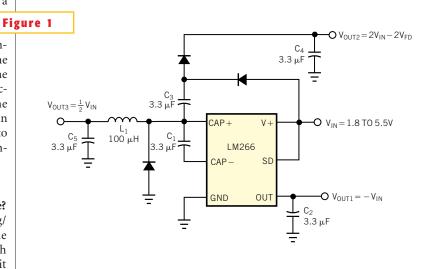

ASIC SWITCHED CONVERTERS generally provide one simple voltage conversion. The most common application for these circuits are to double, invert, and sometimes halve the input voltage. Because they are unregulated and have no stability problems, you can configure them to perform multiple conversions as well. However, because they have no inherent regulation, it is a good idea to use a regulated voltage as the input source. Multiple converters exhibit some voltage change at the output as a function of loading (because of the output resistance), but this drop is often acceptable. The circuit in Figure 1 is a triple-output

switched-capacitor circuit. You can configure the circuit using any switched-capacitor IC that's capable of inversion. This example uses the LM2664, but you can use larger ICs, such as the LM2661 or LM2663, to obtain higher current. The circuit in **Figure 1** can simultaneously invert, double, and halve the input voltage over an input range of 1.8 to 5.5V. The combined current capability of the three outputs equals the maximum load current of the IC in either of the standard topologies: inverting or doubling (40 mA for the LM2664 and 200 mA for the LM2663).

The output resistance for any output is

equal to or less than the typical output resistance of the basic doubler or inverter. This last statement holds true only if you realize that the doubling output is actually  $2V_{IN} - 2V_{FD}$ , where  $V_{FD}$  is the forward drop of the diodes used. The doubling output simply uses two diodes to make a discrete charge pump in conjunction with the switch that connects CAP+ to V<sub>IN</sub> during one cycle and to ground during the next cycle. The extra diode drops may be a problem in some applications, but they would be insignificant if you connected a linear, low-dropout regulator to the doubled output. The halving output uses the concept of an unregulat-

ed inductive step-down switcher with a constant 50% duty cycle. At no load, the output from a 50%-duty-cycle pulse filtered through the inductor and output capacitor is half the peak voltage of the square wave. The same switch used for the doubling function produces the square wave. In the topology of **Figure 1**, you always obtain the inverting function that is inherent to the IC, and you can use or omit the other two outputs as needed. (DI #2578)

Is this the best Design Idea in this issue? Vote at www.ednmag.com/ednmag/ infoaccess.asp, enter No. 447 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."

One switched-capacitor IC simultaneously inverts, doubles, and halves the input voltage.

#### **Current-limit switch is digitally programmable**

Budge Ing, Maxim Integrated Products, Sunnyvale, CA

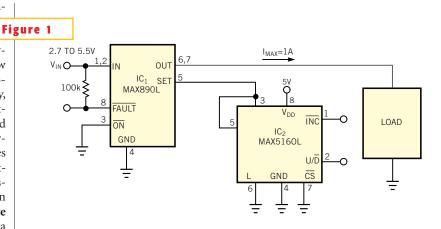

URRENT-LIMIT SWITCHES are virtually ubiquitous in system controls. They provide a safe means for regulating the current delivered to a load circuit. The switches allow the load current to increase to a programmed limit but no higher. Typically, the current limit is a function of the voltage across an external resistor, produced by the current from a fixed source internal to the switch IC. This voltage serves as the reference for an internal currentlimiting amplifier. By replacing the resistor with a digital potentiometer, you can easily program the current limit (Figure 1). IC<sub>1</sub> is a current-limit switch with a maximum programmable limit of 1A. The limit equals 1380/R<sub>SET</sub>, where R<sub>SET</sub> is the resistance between pins 5 and 6 of IC<sub>2</sub>. IC<sub>2</sub> is a 50-k $\Omega$  digital potentiometer whose resistance is programmable in 32 equal increments. With  $\overline{CS}$  held low, high-to-low transitions at INC (Pin 1) increments IC<sub>2</sub>'s internal counter.

These transitions increase the resistance between W and L when  $U/\overline{D}$  is low and reduce it when  $U/\overline{D}$  is high. IC<sub>1</sub> includes a thermal-shutdown capability

You can program a current limit to 1A in 32 equal increments by using a digital potentiometer.

that turns the load current completely off when the chip temperature exceeds 135°C. It restores the load current when the temperature cools by 10°C. If the short-circuit fault is still present, the switch cycles off and on, yielding a pulsed load current. An open-drain Fault output (Pin 8) switches low when the load demands current beyond the programmed limit, enabling an external system to monitor the condition of the current switch. (DI #2577)

Is this the best Design Idea in this issue? Vote at www.ednmag.com/ednmag/ infoaccess.asp, enter No. 448 in the "Circle Number" field, and hit the Search bar. Put a tick in the "Select" box and hit "Submit."